|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

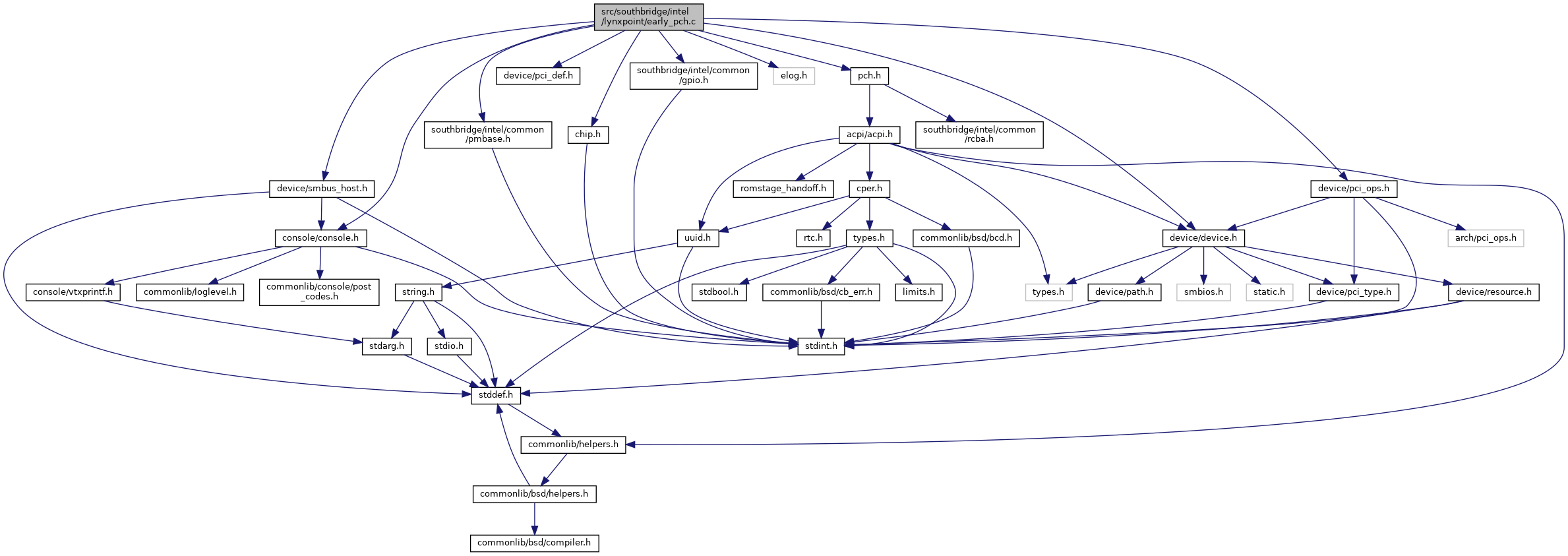

#include <console/console.h>#include <device/pci_ops.h>#include <device/device.h>#include <device/pci_def.h>#include <device/smbus_host.h>#include <southbridge/intel/common/pmbase.h>#include <elog.h>#include "pch.h"#include "chip.h"#include <southbridge/intel/common/gpio.h>

Go to the source code of this file.

Functions | |

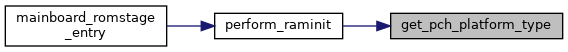

| enum pch_platform_type | get_pch_platform_type (void) |

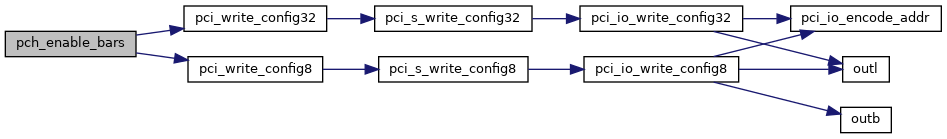

| static void | pch_enable_bars (void) |

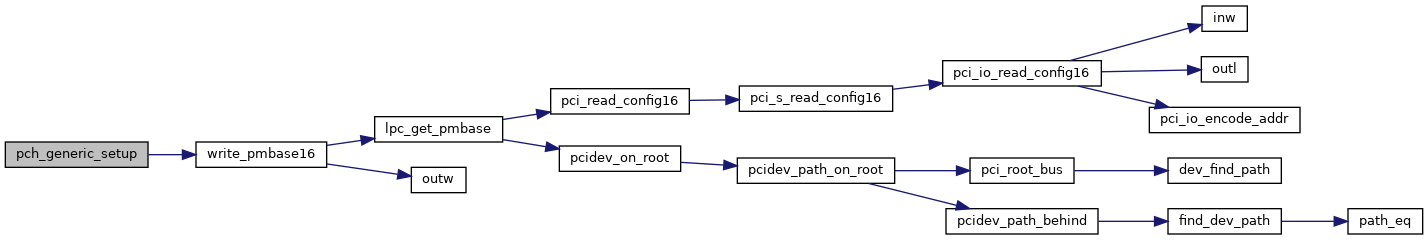

| static void | pch_generic_setup (void) |

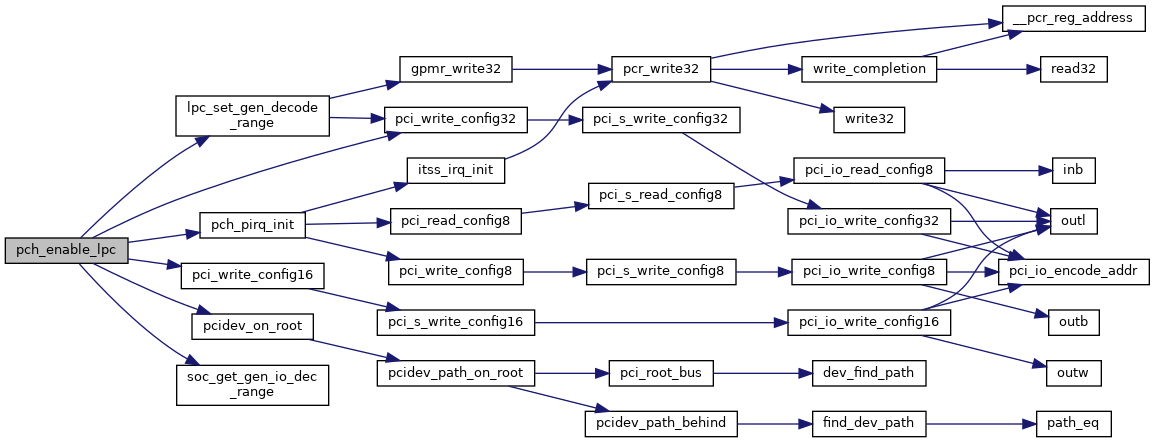

| void | pch_enable_lpc (void) |

| void __weak | mainboard_config_superio (void) |

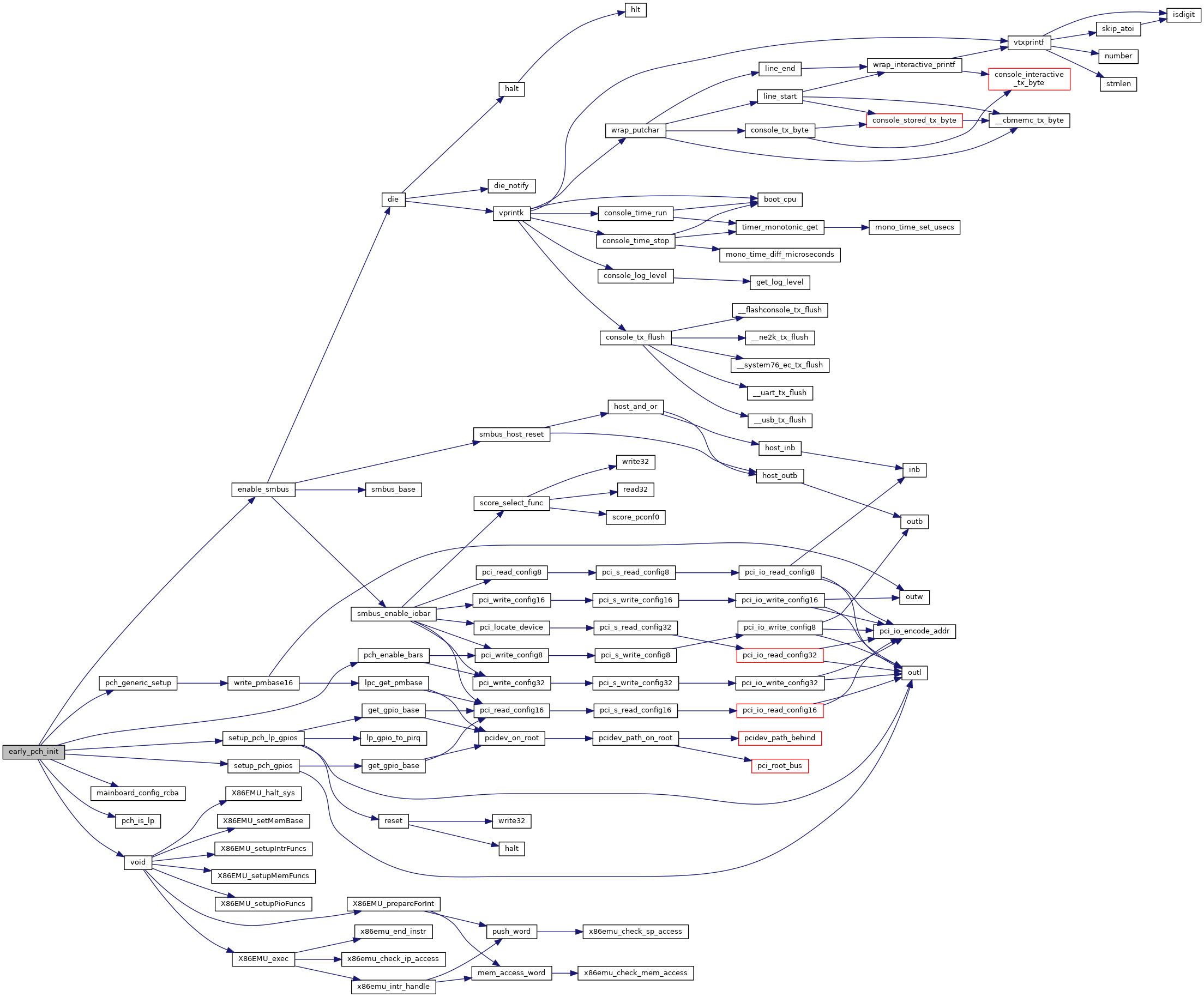

| void | early_pch_init (void) |

Definition at line 88 of file early_pch.c.

References enable_smbus(), FD, mainboard_config_rcba(), mainboard_gpio_map, mainboard_lp_gpio_map, OIC, PCH_DISABLE_ALWAYS, pch_enable_bars(), pch_generic_setup(), pch_is_lp(), RCBA16, RCBA32, RCBA32_AND_OR, RCBA32_OR, setup_pch_gpios(), setup_pch_lp_gpios(), and void().

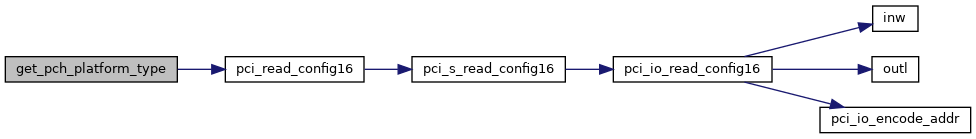

| enum pch_platform_type get_pch_platform_type | ( | void | ) |

Definition at line 1 of file early_pch.c.

References did, PCH_LPC_DEV, PCH_TYPE_DESKTOP, PCH_TYPE_MOBILE, PCH_TYPE_ULT, PCI_DEVICE_ID, and pci_read_config16().

Referenced by perform_raminit().

Definition at line 84 of file early_pch.c.

Definition at line 35 of file early_pch.c.

References ACPI_CNTL, ACPI_EN, DEFAULT_GPIOBASE, DEFAULT_PMBASE, GPIO_BASE, GPIO_CNTL, PCH_LPC_DEV, pci_write_config32(), pci_write_config8(), PMBASE, and RCBA.

Referenced by early_pch_init().

Definition at line 57 of file early_pch.c.

References device::chip_info, CNF1_LPC_EN, CNF2_LPC_EN, COMA_LPC_EN, config, ENV_PAYLOAD_LOADER, GAMEL_LPC_EN, KBC_LPC_EN, LPC_EN, LPC_GEN1_DEC, LPC_GEN2_DEC, LPC_GEN3_DEC, LPC_GEN4_DEC, LPC_IO_DEC, LPC_NUM_GENERIC_IO_RANGES, lpc_set_gen_decode_range(), MC_LPC_EN, NULL, PCH_LPC_DEV, pch_pirq_init(), pci_write_config16(), pci_write_config32(), pcidev_on_root(), and soc_get_gen_io_dec_range().

Definition at line 49 of file early_pch.c.

References BIOS_DEBUG, GCS, printk, RCBA32, and write_pmbase16().

Referenced by early_pch_init().