|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

Go to the source code of this file.

Functions | |

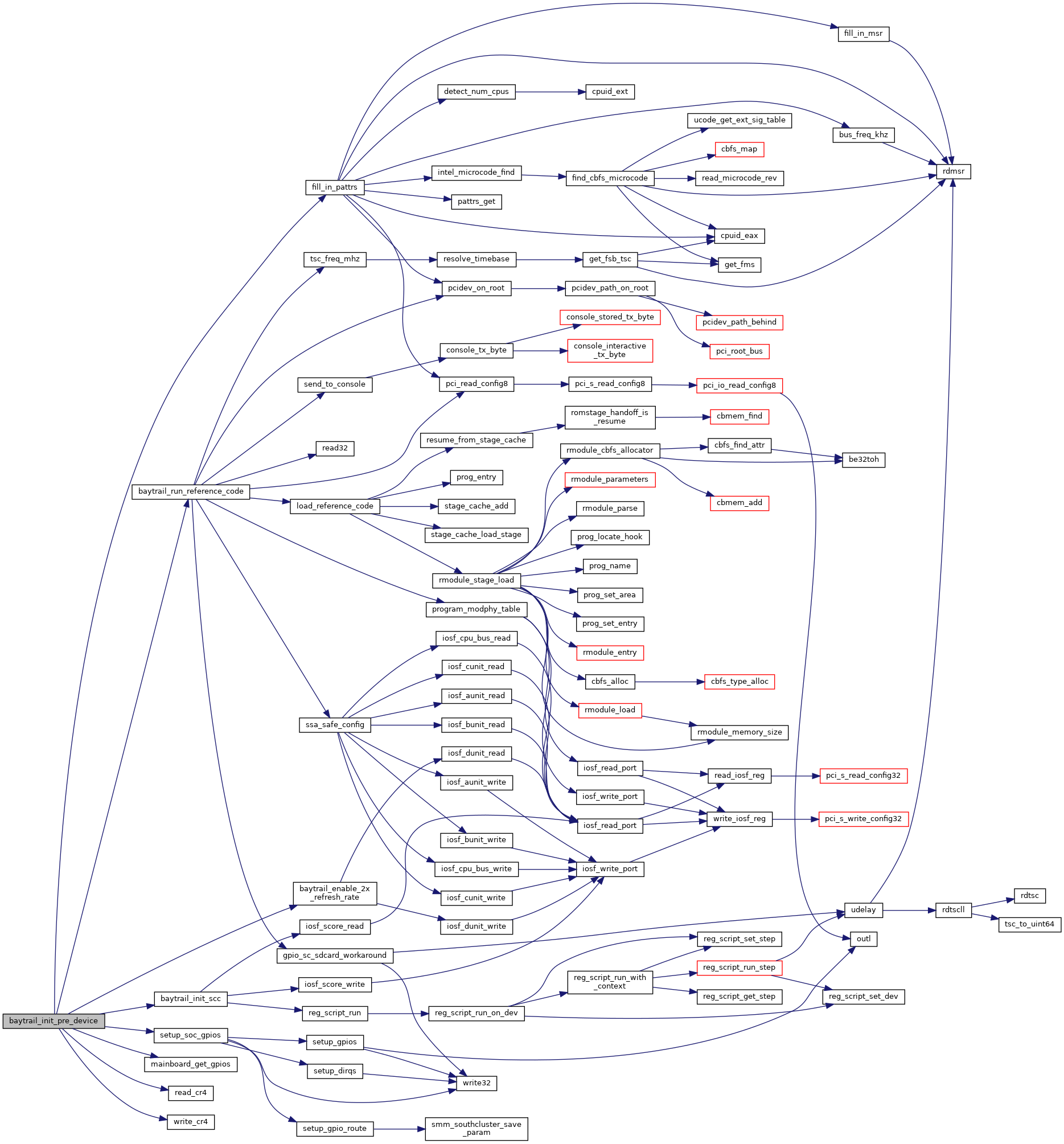

| void | baytrail_init_pre_device (struct soc_intel_baytrail_config *config) |

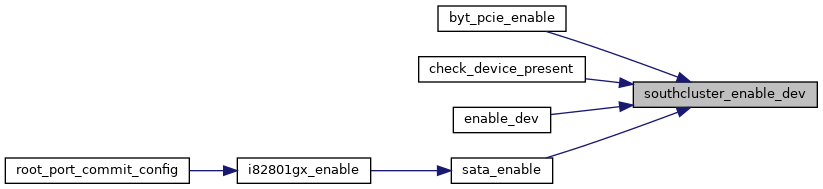

| void | southcluster_enable_dev (struct device *dev) |

| void | baytrail_run_reference_code (void) |

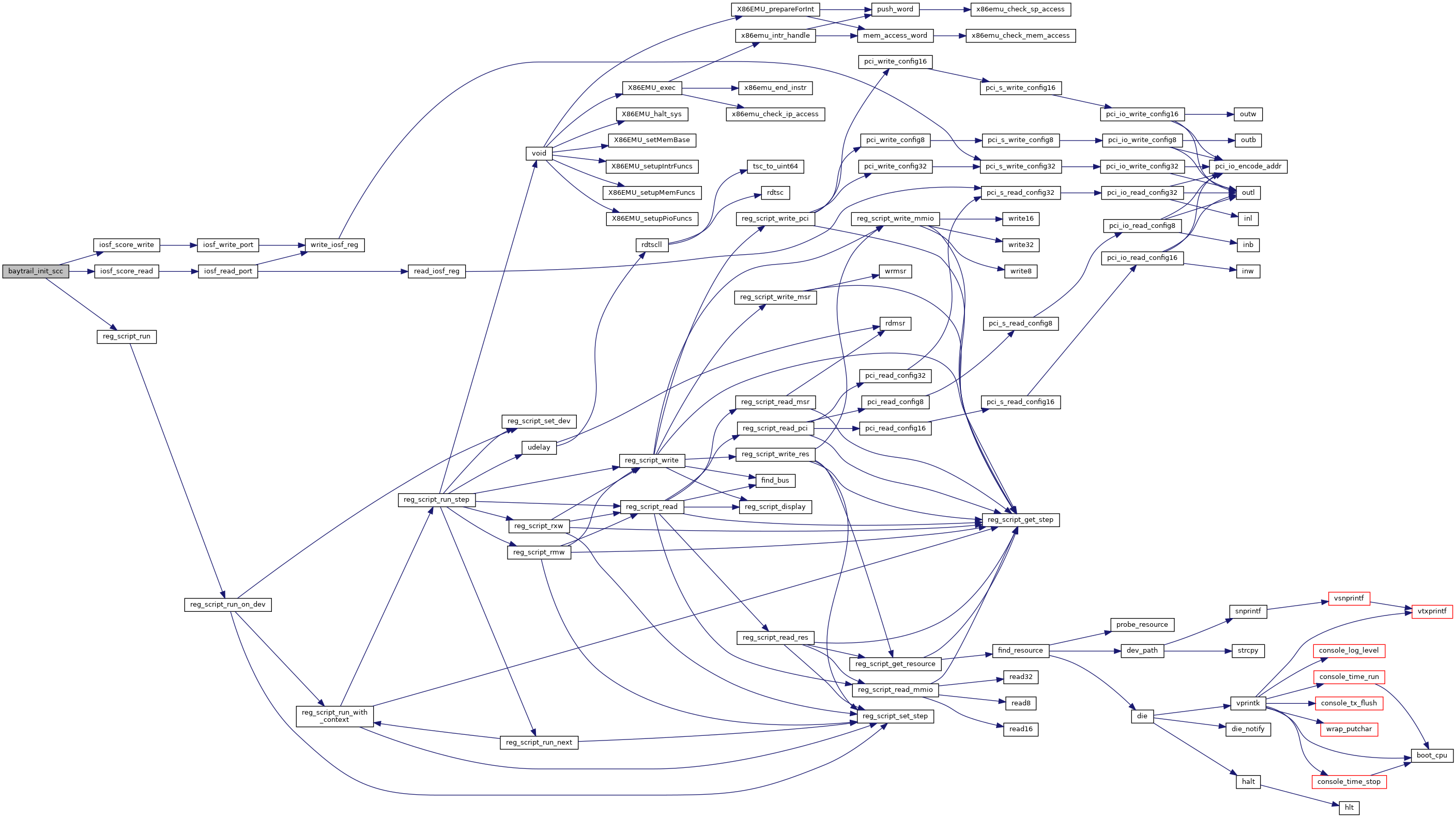

| void | baytrail_init_scc (void) |

| void | scc_enable_acpi_mode (struct device *dev, int iosf_reg, int nvs_index) |

Variables | |

| struct pci_operations | soc_pci_ops |

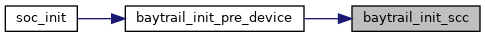

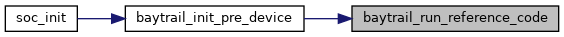

| void baytrail_init_pre_device | ( | struct soc_intel_baytrail_config * | config | ) |

Definition at line 170 of file ramstage.c.

References baytrail_enable_2x_refresh_rate(), baytrail_init_scc(), baytrail_run_reference_code(), config, CR4_OSFXSR, CR4_OSXMMEXCPT, fill_in_pattrs(), gpio_config, mainboard_get_gpios(), read_cr4(), setup_soc_gpios(), and write_cr4().

Referenced by soc_init().

Definition at line 54 of file scc.c.

References BIOS_DEBUG, iosf_score_read(), iosf_score_write(), printk, reg_script_run(), scc_after_dll, and scc_start_dll.

Referenced by baytrail_init_pre_device().

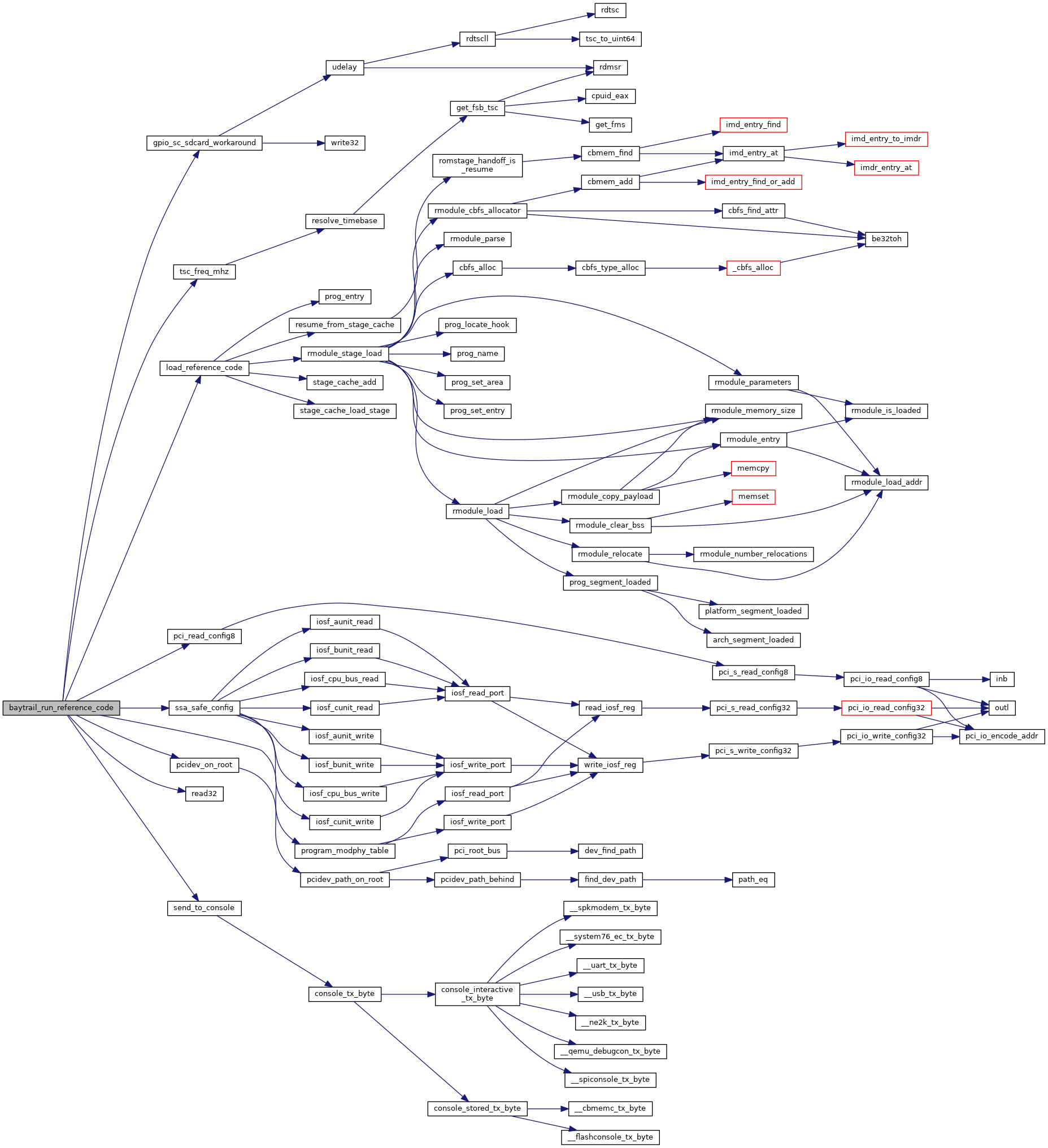

Definition at line 45 of file refcode.c.

References BIOS_DEBUG, EFI_WRAPPER_VER, gpio_sc_sdcard_workaround(), load_reference_code(), LPC_DEV, LPC_FUNC, NULL, pci_read_config8(), pcidev_on_root(), PMC_BASE_ADDRESS, printk, program_modphy_table(), R_PCH_PMC_MTPMC1, read32(), reva0_modphy_table, revb0_modphy_table, REVID, RID_B_STEPPING_START, send_to_console(), setbits32, ssa_safe_config(), tsc_freq_mhz(), efi_wrapper_params::tsc_ticks_per_microsecond, and efi_wrapper_params::version.

Referenced by baytrail_init_pre_device().

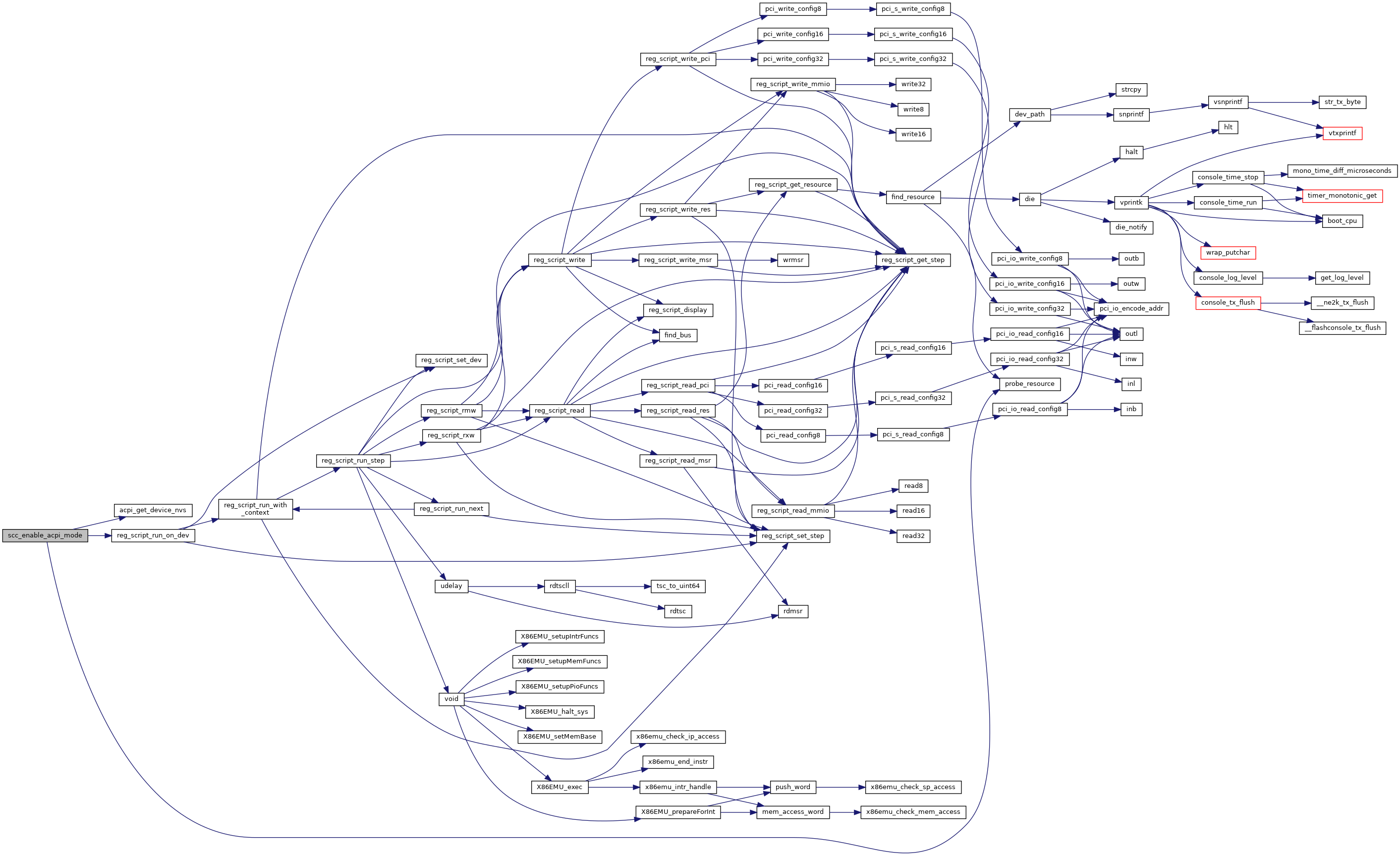

Definition at line 71 of file scc.c.

References acpi_get_device_nvs(), resource::base, IOSF_PORT_SCC, ops, PCI_BASE_ADDRESS_0, PCI_BASE_ADDRESS_1, PCI_COMMAND, PCI_COMMAND_INT_DISABLE, PCI_COMMAND_MASTER, PCI_COMMAND_MEMORY, probe_resource(), REG_PCI_OR16, REG_SCRIPT_END, reg_script_run_on_dev(), device_nvs::scc_bar0, device_nvs::scc_bar1, SCC_CTL_ACPI_INT_EN, SCC_CTL_PCI_CFG_DIS, and device_nvs::scc_en.

Definition at line 452 of file southcluster.c.

Referenced by byt_pcie_enable(), check_device_present(), enable_dev(), and sata_enable().