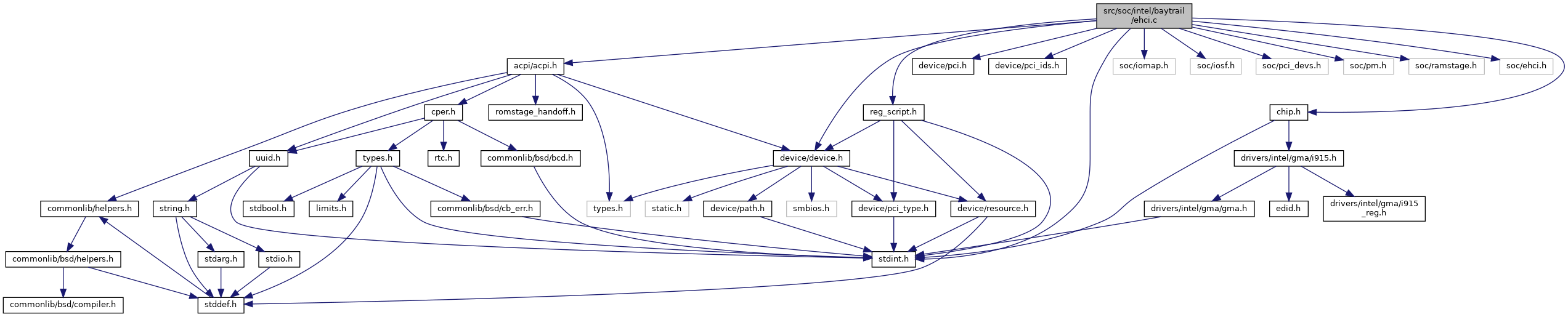

#include <acpi/acpi.h>

#include <device/device.h>

#include <device/pci.h>

#include <device/pci_ids.h>

#include <stdint.h>

#include <reg_script.h>

#include <soc/iomap.h>

#include <soc/iosf.h>

#include <soc/pci_devs.h>

#include <soc/pm.h>

#include <soc/ramstage.h>

#include <soc/ehci.h>

#include "chip.h"

Go to the source code of this file.

◆ ehci_init()

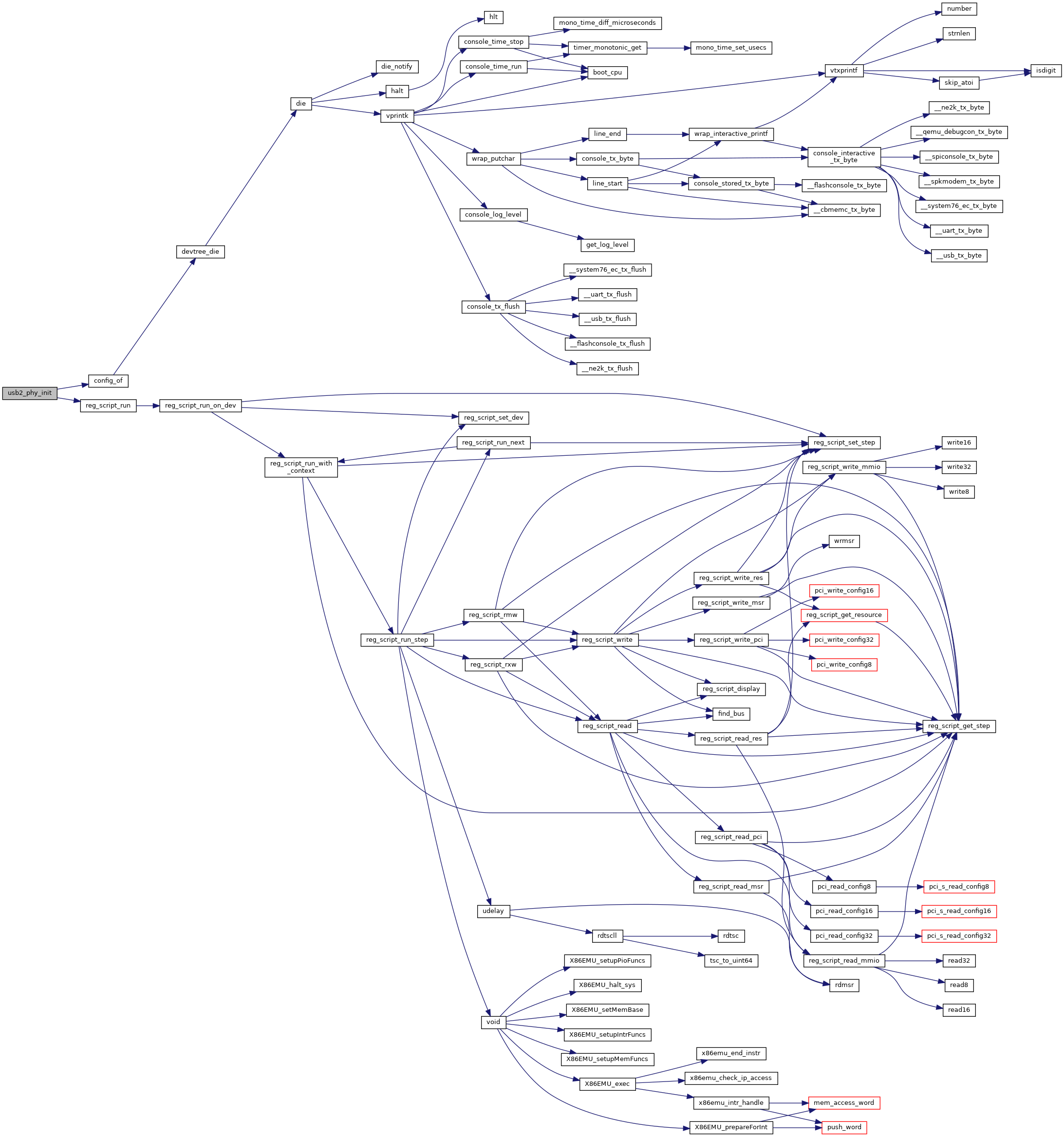

◆ usb2_phy_init()

Definition at line 76 of file ehci.c.

References config, config_of(), IOSF_PORT_USBPHY, REG_SCRIPT_END, reg_script_run(), soc_intel_baytrail_config::usb2_comp_bg, USBPHY_COMPBG, USBPHY_PER_PORT_LANE0, USBPHY_PER_PORT_LANE1, USBPHY_PER_PORT_LANE2, USBPHY_PER_PORT_LANE3, USBPHY_PER_PORT_RCOMP_HS_PULLUP0, USBPHY_PER_PORT_RCOMP_HS_PULLUP1, USBPHY_PER_PORT_RCOMP_HS_PULLUP2, and USBPHY_PER_PORT_RCOMP_HS_PULLUP3.

◆ __pci_driver

| const struct pci_driver baytrail_ehci __pci_driver |

|

static |

Initial value:= {

}

static struct device_operations ehci_device_ops

Definition at line 111 of file ehci.c.

◆ ehci_clock_gating_script

| const struct reg_script ehci_clock_gating_script[] |

|

static |

Initial value:= {

}

#define RCBA_BASE_ADDRESS

#define REG_PCI_OR32(reg_, value_)

#define REG_MMIO_WRITE32(reg_, value_)

Definition at line 1 of file ehci.c.

◆ ehci_device_ops

Initial value:= {

}

static void ehci_init(struct device *dev)

void pci_dev_enable_resources(struct device *dev)

void pci_dev_read_resources(struct device *dev)

void pci_dev_set_resources(struct device *dev)

struct pci_operations soc_pci_ops

Definition at line 111 of file ehci.c.

◆ ehci_disable_script

Initial value:= {

}

#define PCI_BASE_ADDRESS_0

#define REG_RES_RMW32(bar_, reg_, mask_, value_)

#define REG_RES_POLL32(bar_, reg_, mask_, value_, timeout_)

#define REG_MMIO_OR32(reg_, value_)

#define REG_PCI_RMW32(reg_, mask_, value_)

#define EHCI_SBRN_FLA_PWC

Definition at line 1 of file ehci.c.

◆ ehci_hc_reset

Initial value:= {

}

#define REG_RES_OR16(bar_, reg_, value_)

Definition at line 1 of file ehci.c.

◆ ehci_init_script

Initial value:= {

}

#define REG_MMIO_RMW32(reg_, mask_, value_)

#define REG_PCI_OR16(reg_, value_)

Definition at line 1 of file ehci.c.