|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

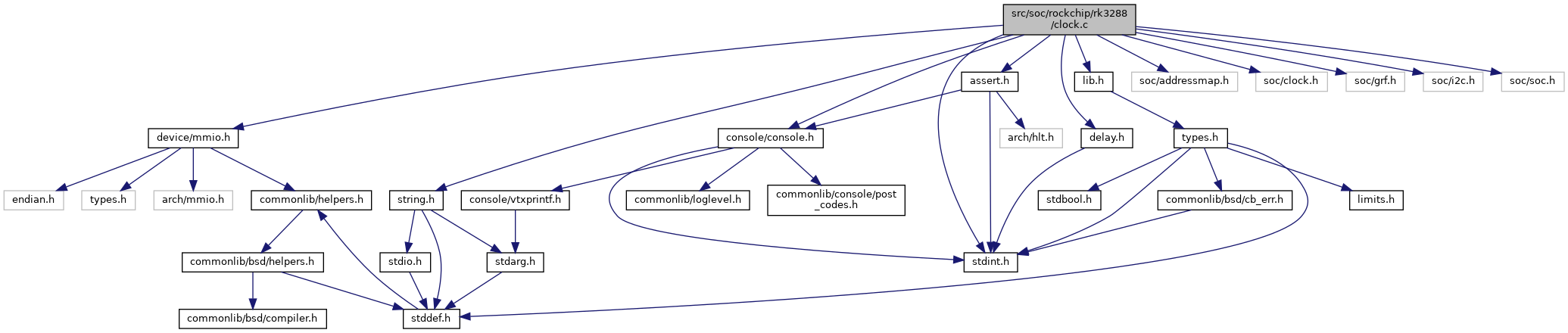

#include <device/mmio.h>#include <assert.h>#include <console/console.h>#include <delay.h>#include <lib.h>#include <soc/addressmap.h>#include <soc/clock.h>#include <soc/grf.h>#include <soc/i2c.h>#include <soc/soc.h>#include <stdint.h>#include <string.h>

Go to the source code of this file.

Data Structures | |

| struct | pll_div |

| struct | rk3288_cru_reg |

Macros | |

| #define | PLL_DIVISORS(hz, _nr, _no) |

| #define | PLL_OD_MSK (0x0F) |

| #define | PLL_NR_MSK (0x3F << 8) |

| #define | PLL_NR_SHIFT (8) |

| #define | PLL_NF_MSK (0x1FFF) |

| #define | PLL_BWADJ_MSK (0x0FFF) |

| #define | PLL_RESET_MSK (1 << 5) |

| #define | PLL_RESET (1 << 5) |

| #define | PLL_RESET_RESUME (0 << 5) |

| #define | CORE_SEL_PLL_MSK (1 << 15) |

| #define | CORE_SEL_APLL (0 << 15) |

| #define | CORE_SEL_GPLL (1 << 15) |

| #define | A12_DIV_SHIFT (8) |

| #define | A12_DIV_MSK (0x1F << 8) |

| #define | MP_DIV_SHIFT (4) |

| #define | MP_DIV_MSK (0xF << 4) |

| #define | M0_DIV_MSK (0xF) |

| #define | PD_BUS_SEL_PLL_MSK (1 << 15) |

| #define | PD_BUS_SEL_CPLL (0 << 15) |

| #define | PD_BUS_SEL_GPLL (1 << 15) |

| #define | PD_BUS_PCLK_DIV_SHIFT (12) |

| #define | PD_BUS_PCLK_DIV_MSK (0x7 << 12) |

| #define | PD_BUS_HCLK_DIV_SHIFT (8) |

| #define | PD_BUS_HCLK_DIV_MSK (0x3 << 8) |

| #define | PD_BUS_ACLK_DIV0_SHIFT (3) |

| #define | PD_BUS_ACLK_DIV0_MASK (0x1f << 3) |

| #define | PD_BUS_ACLK_DIV1_SHIFT (0) |

| #define | PD_BUS_ACLK_DIV1_MASK (0x7 << 0) |

| #define | PERI_SEL_PLL_MSK (1 << 15) |

| #define | PERI_SEL_CPLL (0 << 15) |

| #define | PERI_SEL_GPLL (1 << 15) |

| #define | PERI_PCLK_DIV_SHIFT (12) |

| #define | PERI_PCLK_DIV_MSK (0x7 << 12) |

| #define | PERI_HCLK_DIV_SHIFT (8) |

| #define | PERI_HCLK_DIV_MSK (0x3 << 8) |

| #define | PERI_ACLK_DIV_SHIFT (0x0) |

| #define | PERI_ACLK_DIV_MSK (0x1F) |

| #define | L2_DIV_MSK (0x7) |

| #define | ATCLK_DIV_MSK (0x1F << 4) |

| #define | ATCLK_DIV_SHIFT (4) |

| #define | PCLK_DBG_DIV_MSK (0x1F << 9) |

| #define | PCLK_DBG_DIV_SHIFT (9) |

| #define | APLL_MODE_MSK (0x3) |

| #define | APLL_MODE_SLOW (0) |

| #define | APLL_MODE_NORM (1) |

| #define | DPLL_MODE_MSK (0x3 << 4) |

| #define | DPLL_MODE_SLOW (0 << 4) |

| #define | DPLL_MODE_NORM (1 << 4) |

| #define | CPLL_MODE_MSK (0x3 << 8) |

| #define | CPLL_MODE_SLOW (0 << 8) |

| #define | CPLL_MODE_NORM (1 << 8) |

| #define | GPLL_MODE_MSK (0x3 << 12) |

| #define | GPLL_MODE_SLOW (0 << 12) |

| #define | GPLL_MODE_NORM (1 << 12) |

| #define | NPLL_MODE_MSK (0x3 << 14) |

| #define | NPLL_MODE_SLOW (0 << 14) |

| #define | NPLL_MODE_NORM (1 << 14) |

| #define | SOCSTS_DPLL_LOCK (1 << 5) |

| #define | SOCSTS_APLL_LOCK (1 << 6) |

| #define | SOCSTS_CPLL_LOCK (1 << 7) |

| #define | SOCSTS_GPLL_LOCK (1 << 8) |

| #define | SOCSTS_NPLL_LOCK (1 << 9) |

| #define | VCO_MAX_KHZ (2200 * (MHz/KHz)) |

| #define | VCO_MIN_KHZ (440 * (MHz/KHz)) |

| #define | OUTPUT_MAX_KHZ (2200 * (MHz/KHz)) |

| #define | OUTPUT_MIN_KHZ 27500 |

| #define | FREF_MAX_KHZ (2200 * (MHz/KHz)) |

| #define | FREF_MIN_KHZ 269 |

Functions | |

| check_member (rk3288_cru_reg, cru_emmc_con[1], 0x021c) | |

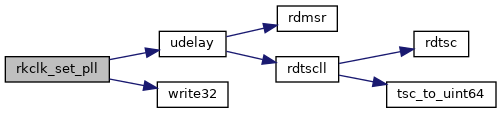

| static int | rkclk_set_pll (u32 *pll_con, const struct pll_div *div) |

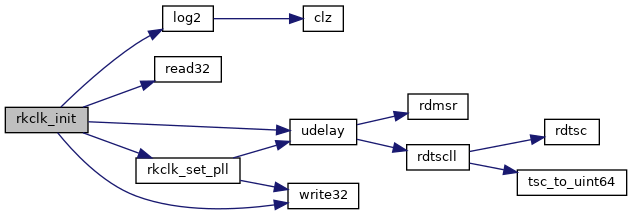

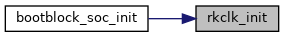

| void | rkclk_init (void) |

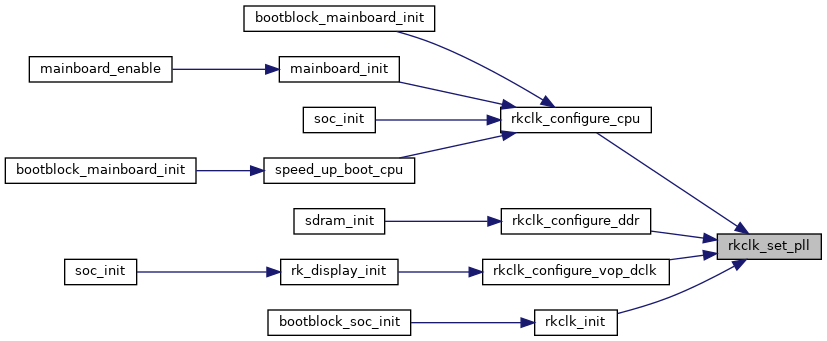

| void | rkclk_configure_cpu (enum apll_frequencies apll_freq) |

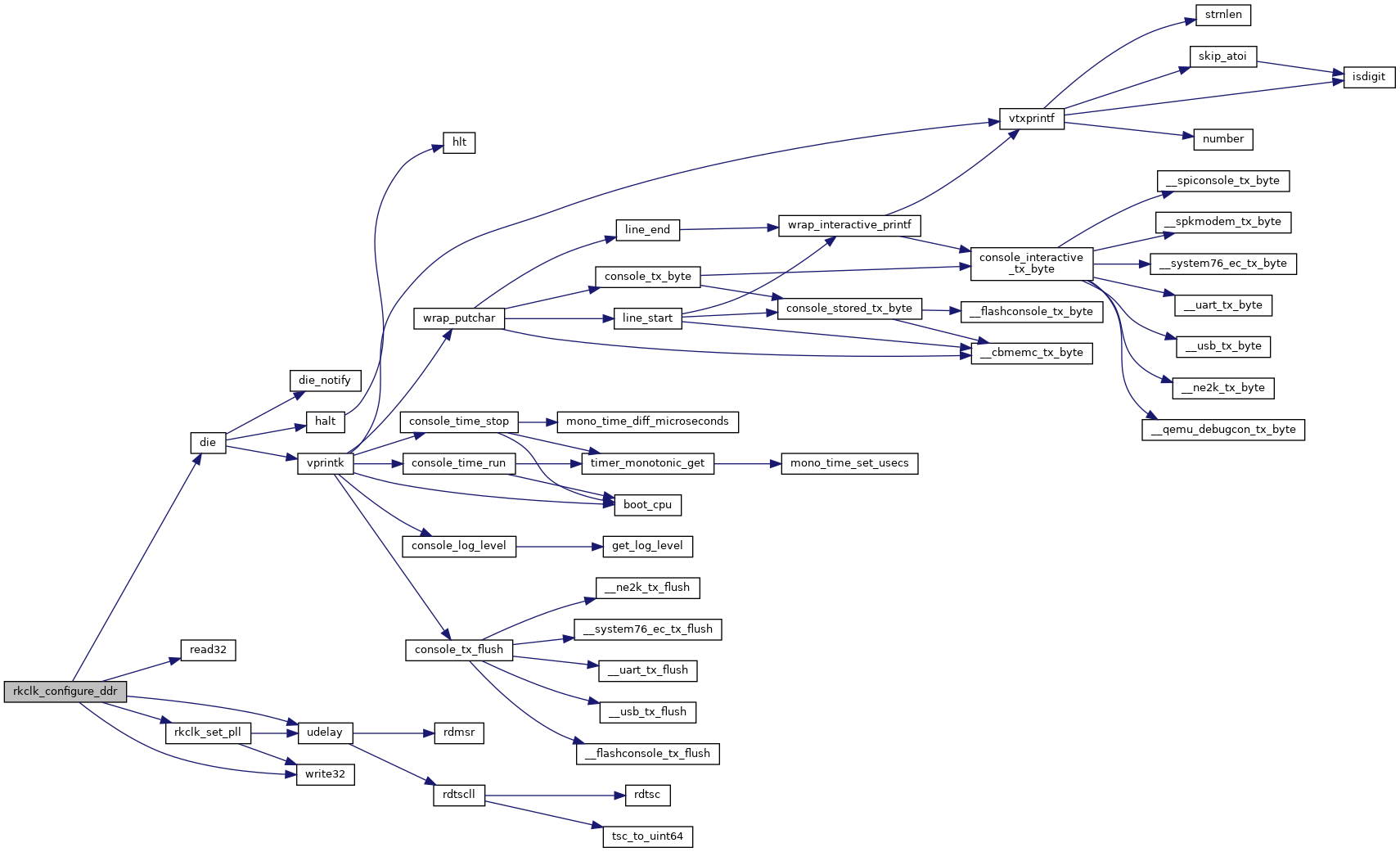

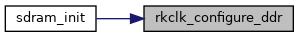

| void | rkclk_configure_ddr (unsigned int hz) |

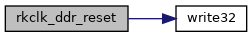

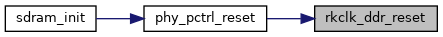

| void | rkclk_ddr_reset (u32 ch, u32 ctl, u32 phy) |

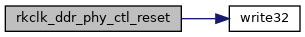

| void | rkclk_ddr_phy_ctl_reset (u32 ch, u32 n) |

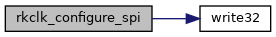

| void | rkclk_configure_spi (unsigned int bus, unsigned int hz) |

| static u32 | clk_gcd (u32 a, u32 b) |

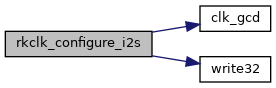

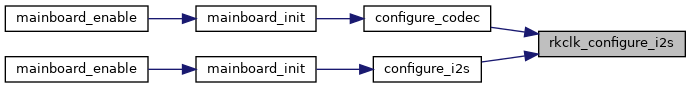

| void | rkclk_configure_i2s (unsigned int hz) |

| void | rkclk_configure_crypto (unsigned int hz) |

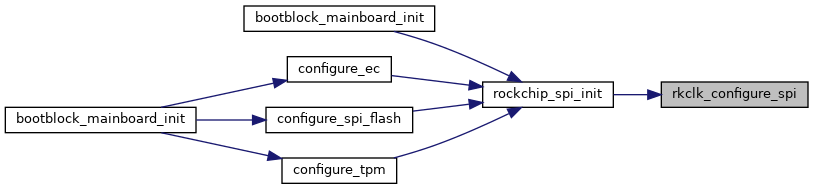

| void | rkclk_configure_tsadc (unsigned int hz) |

| static int | pll_para_config (u32 freq_hz, struct pll_div *div, u32 *ext_div) |

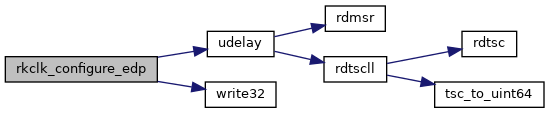

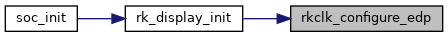

| void | rkclk_configure_edp (void) |

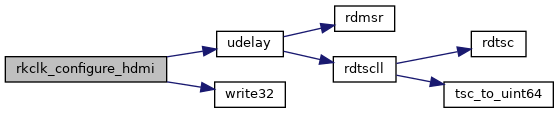

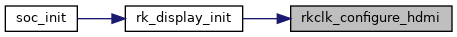

| void | rkclk_configure_hdmi (void) |

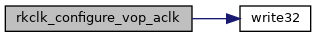

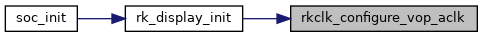

| void | rkclk_configure_vop_aclk (u32 vop_id, u32 aclk_hz) |

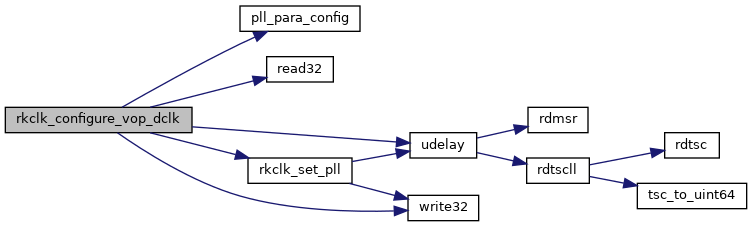

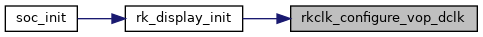

| int | rkclk_configure_vop_dclk (u32 vop_id, u32 dclk_hz) |

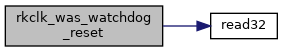

| int | rkclk_was_watchdog_reset (void) |

| unsigned int | rkclk_i2c_clock_for_bus (unsigned int bus) |

Variables | |

| static struct rk3288_cru_reg *const | cru_ptr = (void *)CRU_BASE |

| static const struct pll_div | gpll_init_cfg = PLL_DIVISORS(GPLL_HZ, 2, 2) |

| static const struct pll_div | cpll_init_cfg = PLL_DIVISORS(CPLL_HZ, 1, 2) |

| static const struct pll_div | apll_1800_cfg = PLL_DIVISORS(1800*MHz, 1, 1) |

| static const struct pll_div | apll_1416_cfg = PLL_DIVISORS(1416*MHz, 1, 1) |

| static const struct pll_div | apll_600_cfg = PLL_DIVISORS(600*MHz, 1, 2) |

| static const struct pll_div * | apll_cfgs [] |

| #define PLL_DIVISORS | ( | hz, | |

| _nr, | |||

| _no | |||

| ) |

| check_member | ( | rk3288_cru_reg | , |

| cru_emmc_con | [1], | ||

| 0x021c | |||

| ) |

Definition at line 441 of file clock.c.

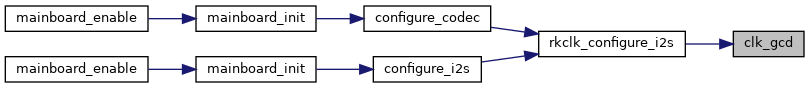

Referenced by rkclk_configure_i2s().

Definition at line 493 of file clock.c.

References BIOS_ERR, DIV_ROUND_UP, FREF_MAX_KHZ, FREF_MIN_KHZ, KHz, MHz, pll_div::nf, pll_div::no, pll_div::nr, OSC_HZ, printk, VCO_MAX_KHZ, and VCO_MIN_KHZ.

Referenced by rkclk_configure_vop_dclk().

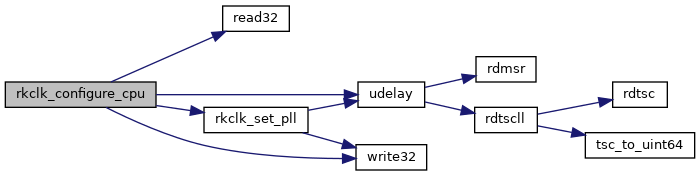

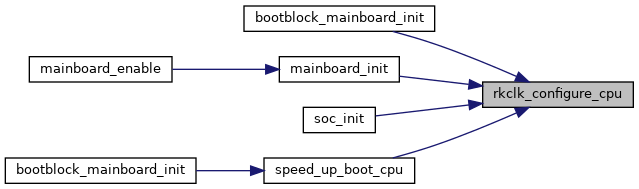

| void rkclk_configure_cpu | ( | enum apll_frequencies | apll_freq | ) |

Definition at line 309 of file clock.c.

References A12_DIV_MSK, A12_DIV_SHIFT, apll_cfgs, APLL_MODE_MSK, APLL_MODE_NORM, APLL_MODE_SLOW, ATCLK_DIV_MSK, ATCLK_DIV_SHIFT, CORE_SEL_PLL_MSK, rk3288_cru_reg::cru_apll_con, rk3288_cru_reg::cru_clksel_con, rk3288_cru_reg::cru_mode_con, cru_ptr, L2_DIV_MSK, M0_DIV_MSK, MP_DIV_MSK, MP_DIV_SHIFT, PCLK_DBG_DIV_MSK, PCLK_DBG_DIV_SHIFT, read32(), rk3288_grf, RK_CLRBITS, RK_CLRSETBITS, rkclk_set_pll(), rk3288_grf_regs::soc_status, SOCSTS_APLL_LOCK, udelay(), and write32().

Referenced by bootblock_mainboard_init(), mainboard_init(), soc_init(), and speed_up_boot_cpu().

Definition at line 472 of file clock.c.

References assert, rk3288_cru_reg::cru_clksel_con, cru_ptr, MHz, PD_BUS_ACLK_HZ, RK_CLRSETBITS, and write32().

Referenced by bootblock_soc_init().

Definition at line 349 of file clock.c.

References rk3288_cru_reg::cru_dpll_con, rk3288_cru_reg::cru_mode_con, cru_ptr, die(), DPLL_MODE_MSK, DPLL_MODE_NORM, DPLL_MODE_SLOW, MHz, pll_div::nf, read32(), rk3288_grf, RK_CLRSETBITS, rkclk_set_pll(), rk3288_grf_regs::soc_status, SOCSTS_DPLL_LOCK, udelay(), and write32().

Referenced by sdram_init().

Definition at line 565 of file clock.c.

References rk3288_cru_reg::cru_clksel_con, cru_ptr, rk3288_cru_reg::cru_softrst_con, RK_CLRBITS, RK_SETBITS, udelay(), and write32().

Referenced by rk_display_init().

Definition at line 576 of file clock.c.

References rk3288_cru_reg::cru_clkgate_con, cru_ptr, rk3288_cru_reg::cru_softrst_con, RK_CLRBITS, RK_SETBITS, udelay(), and write32().

Referenced by rk_display_init().

Definition at line 451 of file clock.c.

References assert, clk_gcd(), rk3288_cru_reg::cru_clksel_con, cru_ptr, GPLL_HZ, RK_CLRSETBITS, and write32().

Referenced by configure_codec(), and configure_i2s().

Definition at line 414 of file clock.c.

References assert, BIOS_ERR, rk3288_cru_reg::cru_clksel_con, cru_ptr, GPLL_HZ, printk, RK_CLRSETBITS, and write32().

Referenced by rockchip_spi_init().

Definition at line 482 of file clock.c.

References assert, rk3288_cru_reg::cru_clksel_con, cru_ptr, KHz, RK_CLRSETBITS, and write32().

Referenced by tsadc_init().

Definition at line 587 of file clock.c.

References assert, CPLL_HZ, rk3288_cru_reg::cru_clksel_con, cru_ptr, RK_CLRSETBITS, and write32().

Referenced by rk_display_init().

Definition at line 610 of file clock.c.

References rk3288_cru_reg::cru_clksel_con, rk3288_cru_reg::cru_mode_con, rk3288_cru_reg::cru_npll_con, cru_ptr, NPLL_MODE_MSK, NPLL_MODE_NORM, NPLL_MODE_SLOW, pll_para_config(), read32(), rk3288_grf, RK_CLRSETBITS, rkclk_set_pll(), rk3288_grf_regs::soc_status, SOCSTS_NPLL_LOCK, udelay(), and write32().

Referenced by rk_display_init().

Definition at line 405 of file clock.c.

References ch, cru_ptr, rk3288_cru_reg::cru_softrst_con, RK_CLRSETBITS, and write32().

Referenced by sdram_init().

Definition at line 388 of file clock.c.

References ch, cru_ptr, rk3288_cru_reg::cru_softrst_con, RK_CLRSETBITS, and write32().

Referenced by phy_pctrl_reset().

Definition at line 658 of file clock.c.

References PD_BUS_PCLK_HZ, and PERI_PCLK_HZ.

Referenced by i2c_init().

Definition at line 232 of file clock.c.

References assert, cpll_init_cfg, CPLL_MODE_MSK, CPLL_MODE_NORM, CPLL_MODE_SLOW, rk3288_cru_reg::cru_clksel_con, rk3288_cru_reg::cru_cpll_con, rk3288_cru_reg::cru_gpll_con, rk3288_cru_reg::cru_mode_con, cru_ptr, GPLL_HZ, gpll_init_cfg, GPLL_MODE_MSK, GPLL_MODE_NORM, GPLL_MODE_SLOW, log2(), PD_BUS_ACLK_DIV0_MASK, PD_BUS_ACLK_DIV0_SHIFT, PD_BUS_ACLK_DIV1_MASK, PD_BUS_ACLK_HZ, PD_BUS_HCLK_DIV_MSK, PD_BUS_HCLK_DIV_SHIFT, PD_BUS_HCLK_HZ, PD_BUS_PCLK_DIV_MSK, PD_BUS_PCLK_DIV_SHIFT, PD_BUS_PCLK_HZ, PD_BUS_SEL_GPLL, PERI_ACLK_DIV_MSK, PERI_ACLK_DIV_SHIFT, PERI_ACLK_HZ, PERI_HCLK_DIV_MSK, PERI_HCLK_DIV_SHIFT, PERI_HCLK_HZ, PERI_PCLK_DIV_MSK, PERI_PCLK_DIV_SHIFT, PERI_PCLK_HZ, PERI_SEL_GPLL, read32(), rk3288_grf, RK_CLRSETBITS, RK_SETBITS, rkclk_set_pll(), rk3288_grf_regs::soc_status, SOCSTS_CPLL_LOCK, SOCSTS_GPLL_LOCK, udelay(), and write32().

Referenced by bootblock_soc_init().

Definition at line 199 of file clock.c.

References assert, BIOS_DEBUG, KHz, pll_div::nf, pll_div::no, pll_div::nr, OSC_HZ, OUTPUT_MAX_KHZ, OUTPUT_MIN_KHZ, PLL_BWADJ_MSK, PLL_NF_MSK, PLL_NR_MSK, PLL_NR_SHIFT, PLL_OD_MSK, PLL_RESET_MSK, printk, RK_CLRBITS, RK_CLRSETBITS, RK_SETBITS, udelay(), VCO_MAX_KHZ, VCO_MIN_KHZ, and write32().

Referenced by rkclk_configure_cpu(), rkclk_configure_ddr(), rkclk_configure_vop_dclk(), and rkclk_init().

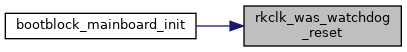

| int rkclk_was_watchdog_reset | ( | void | ) |

Definition at line 652 of file clock.c.

References rk3288_cru_reg::cru_glb_rst_st, cru_ptr, and read32().

Referenced by bootblock_mainboard_init().

|

static |

|

static |

|

static |

|

static |

Definition at line 66 of file clock.c.

Referenced by rkclk_configure_cpu().

|

static |

Definition at line 50 of file clock.c.

Referenced by rkclk_init().

|

static |

Definition at line 50 of file clock.c.

Referenced by dram_all_config(), reset_edp(), reset_usb_otg0(), reset_usb_otg1(), rkclk_configure_cpu(), rkclk_configure_crypto(), rkclk_configure_ddr(), rkclk_configure_edp(), rkclk_configure_emmc(), rkclk_configure_hdmi(), rkclk_configure_i2s(), rkclk_configure_mipi(), rkclk_configure_saradc(), rkclk_configure_spi(), rkclk_configure_tsadc(), rkclk_configure_vop_aclk(), rkclk_configure_vop_dclk(), rkclk_ddr_phy_ctl_reset(), rkclk_ddr_reset(), rkclk_i2c_clock_for_bus(), rkclk_init(), rkclk_set_dpllssc(), rkclk_was_watchdog_reset(), setup_usb_otg0(), and setup_usb_otg1().

|

static |

Definition at line 50 of file clock.c.

Referenced by rkclk_init().