|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

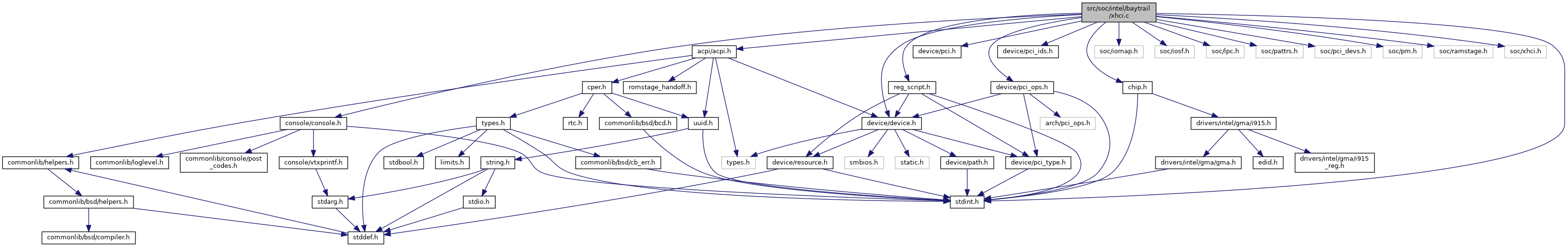

#include <acpi/acpi.h>#include <console/console.h>#include <device/device.h>#include <device/pci.h>#include <device/pci_ops.h>#include <device/pci_ids.h>#include <stdint.h>#include <reg_script.h>#include <soc/iomap.h>#include <soc/iosf.h>#include <soc/lpc.h>#include <soc/pattrs.h>#include <soc/pci_devs.h>#include <soc/pm.h>#include <soc/ramstage.h>#include <soc/xhci.h>#include "chip.h"

Go to the source code of this file.

Functions | |

| static void | xhci_reset_port_usb3 (struct device *dev, int port) |

| static void | xhci_route_all (struct device *dev) |

| static void | xhci_init (struct device *dev) |

Variables | |

| struct reg_script | usb3_phy_script [] |

| const struct reg_script | xhci_init_script [] |

| const struct reg_script | xhci_init_boot_script [] |

| const struct reg_script | xhci_init_resume_script [] |

| const struct reg_script | xhci_clock_gating_script [] |

| static struct device_operations | xhci_device_ops |

| static const struct pci_driver baytrail_xhci | __pci_driver |

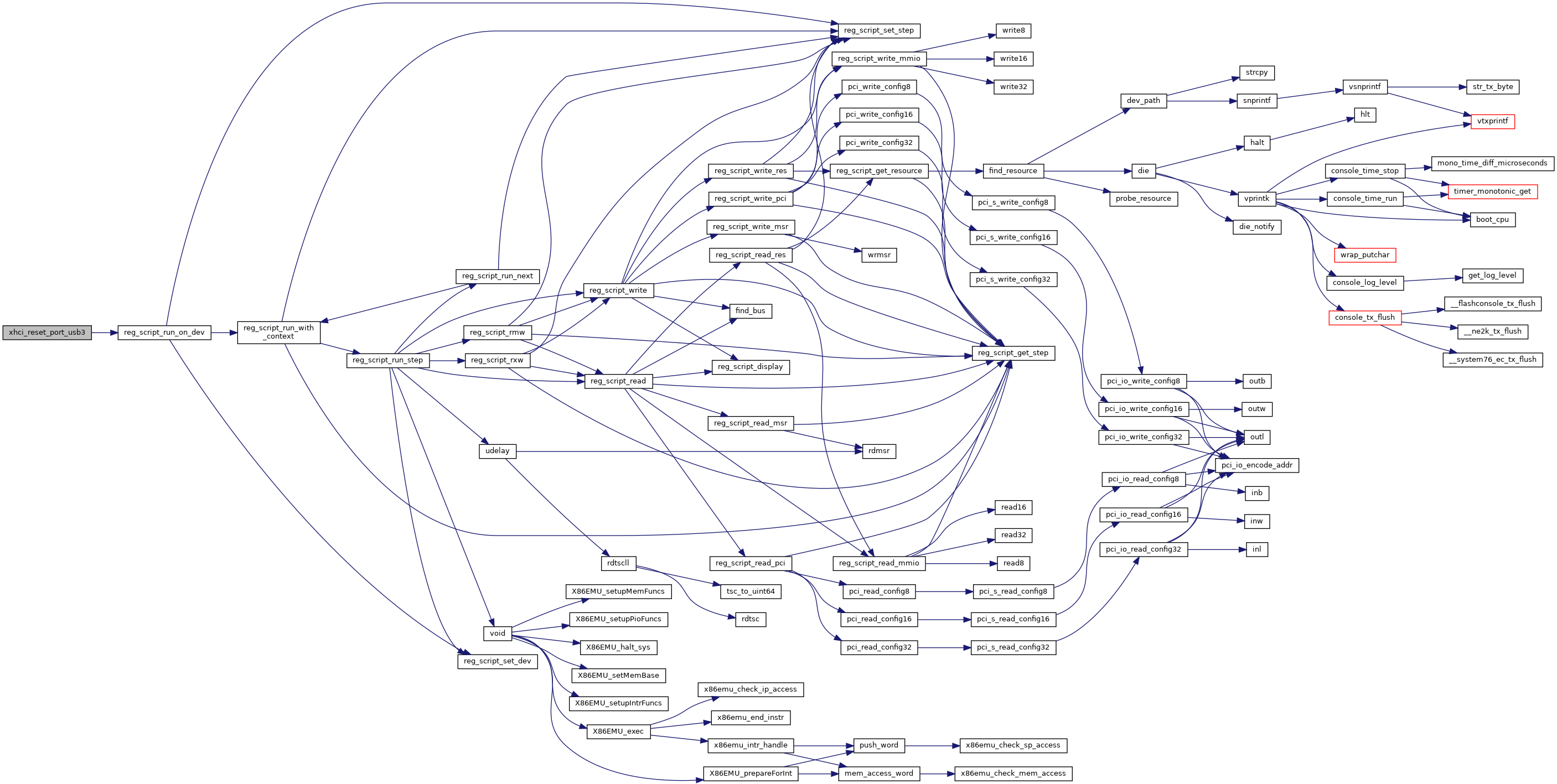

Definition at line 137 of file xhci.c.

References reg_script::dev, PCI_BASE_ADDRESS_0, REG_RES_OR32, REG_RES_POLL32, REG_RES_RMW32, REG_SCRIPT_END, reg_script_run_on_dev(), XHCI_RESET_TIMEOUT, XHCI_USB3_PORTSC, XHCI_USB3_PORTSC_CHST, XHCI_USB3_PORTSC_PED, XHCI_USB3_PORTSC_WPR, and XHCI_USB3_PORTSC_WRC.

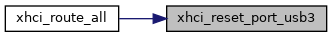

Referenced by xhci_route_all().

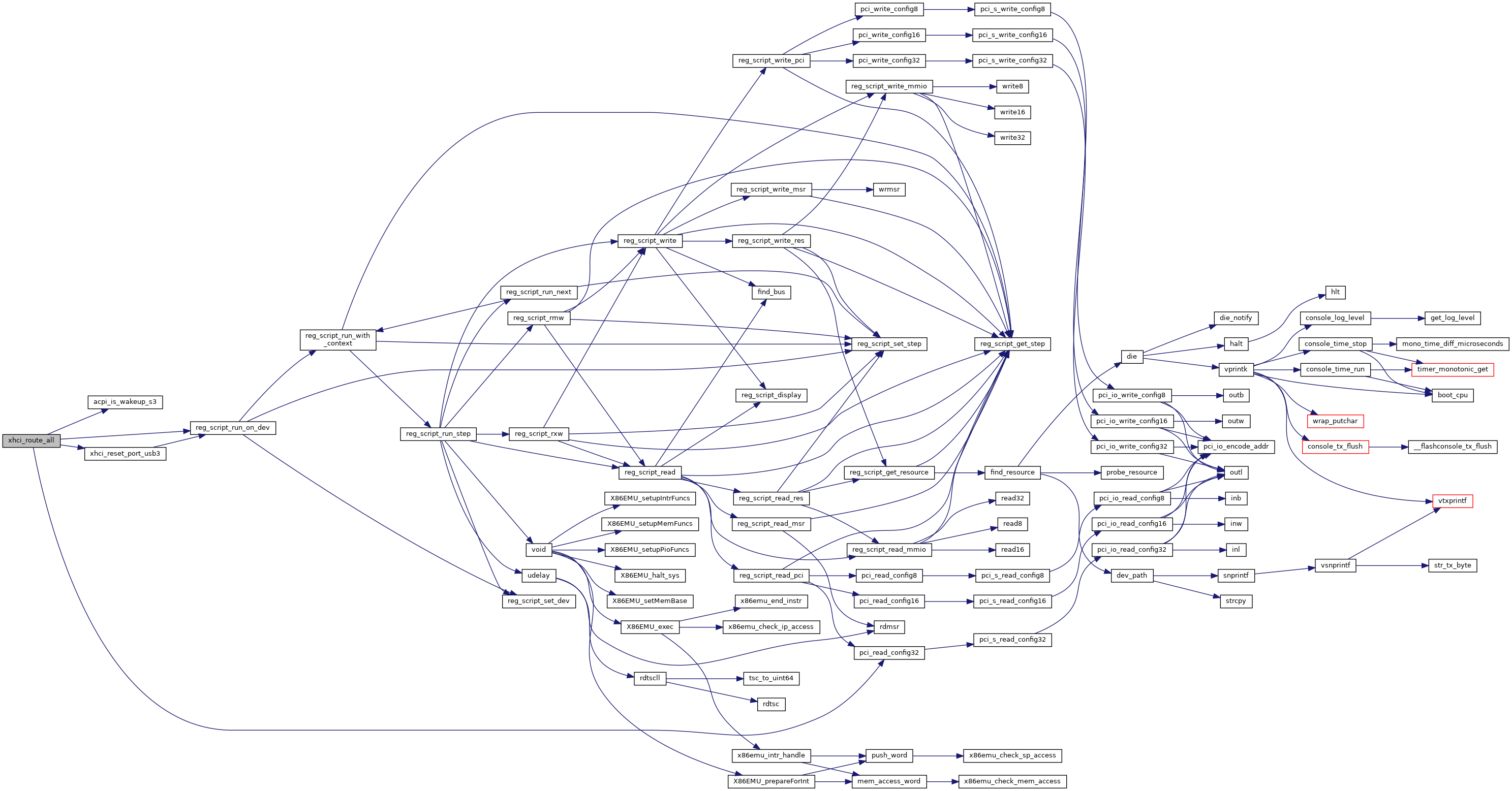

Definition at line 156 of file xhci.c.

References acpi_is_wakeup_s3(), BIOS_INFO, BYTM_USB2_PORT_MAP, BYTM_USB3_PORT_COUNT, BYTM_USB3_PORT_MAP, reg_script::dev, pci_read_config32(), printk, REG_PCI_WRITE32, REG_SCRIPT_END, reg_script_run_on_dev(), xhci_reset_port_usb3(), XHCI_USB2PR, XHCI_USB3PDO, and XHCI_USB3PR.

|

static |

| struct reg_script usb3_phy_script[] |

| const struct reg_script xhci_clock_gating_script[] |

|

static |

| const struct reg_script xhci_init_boot_script[] |

| const struct reg_script xhci_init_resume_script[] |

| const struct reg_script xhci_init_script[] |