|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

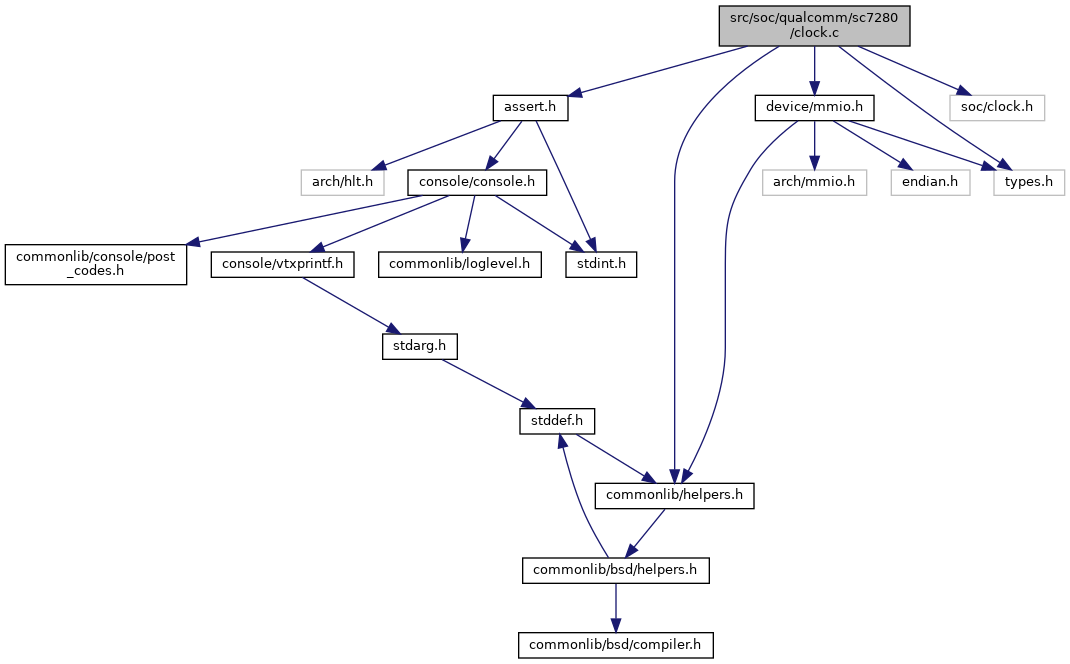

#include <assert.h>#include <commonlib/helpers.h>#include <device/mmio.h>#include <soc/clock.h>#include <types.h>

Go to the source code of this file.

Functions | |

| static enum cb_err | clock_configure_gpll0 (void) |

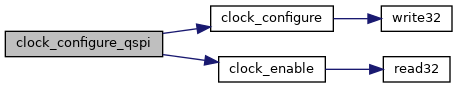

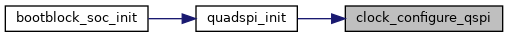

| void | clock_configure_qspi (uint32_t hz) |

| void | clock_enable_qup (int qup) |

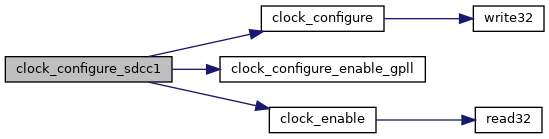

| void | clock_configure_sdcc1 (uint32_t hz) |

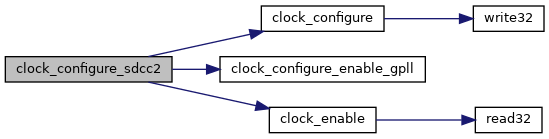

| void | clock_configure_sdcc2 (uint32_t hz) |

| void | clock_configure_dfsr (int qup) |

| static enum cb_err | pll_init_and_set (struct sc7280_apss_clock *apss, u32 l_val) |

| enum cb_err | clock_enable_gdsc (enum clk_gdsc gdsc_type) |

| enum cb_err | mdss_clock_configure (enum clk_mdss clk_type, uint32_t hz, uint32_t source, uint32_t divider, uint32_t m, uint32_t n, uint32_t d_2) |

| enum cb_err | mdss_clock_enable (enum clk_mdss clk_type) |

| enum cb_err | clock_enable_pcie (enum clk_pcie clk_type) |

| enum cb_err | clock_configure_mux (enum clk_pcie clk_type, u32 src_type) |

| static void | speed_up_boot_cpu (void) |

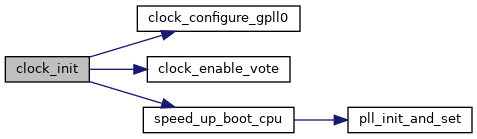

| void | clock_init (void) |

Variables | |

| static struct clock_freq_config | qspi_core_cfg [] |

| static struct clock_freq_config | qupv3_wrap_cfg [] |

| static struct clock_freq_config | sdcc1_core_cfg [] |

| static struct clock_freq_config | sdcc2_core_cfg [] |

| static struct pcie | pcie_cfg [] |

| static struct clock_freq_config | mdss_mdp_cfg [] |

| static struct clock_rcg * | mdss_clock [MDSS_CLK_COUNT] |

| static struct clock_rcg_mnd * | mdss_clock_mnd [MDSS_CLK_COUNT] |

| static u32 * | mdss_cbcr [MDSS_CLK_COUNT] |

| static u32 * | gdsc [MAX_GDSC] |

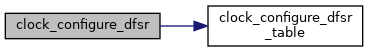

| void clock_configure_dfsr | ( | int | qup | ) |

Definition at line 335 of file clock.c.

References ARRAY_SIZE, clock_configure_dfsr_table(), and qupv3_wrap_cfg.

Definition at line 245 of file clock.c.

References gcc, mdss, MDSS_CORE_GDSC, and PCIE_1_GDSC.

Referenced by clock_init().

Definition at line 264 of file clock.c.

References ARRAY_SIZE, clock_configure(), clock_enable(), gcc, and qspi_core_cfg.

Referenced by quadspi_init().

Definition at line 293 of file clock.c.

References ARRAY_SIZE, alpha_pll_reg_val_config::cal_l_val, CLK_100MHZ, clock_configure(), clock_configure_enable_gpll(), clock_enable(), alpha_pll_reg_val_config::fsm_enable, gcc, alpha_pll_reg_val_config::l_val, alpha_pll_reg_val_config::reg_apcs_pll_br_en, alpha_pll_reg_val_config::reg_cal_l, alpha_pll_reg_val_config::reg_l, alpha_pll_reg_val_config::reg_mode, alpha_pll_reg_val_config::reg_opmode, and sdcc1_core_cfg.

Referenced by mainboard_init().

Definition at line 313 of file clock.c.

References alpha_pll_reg_val_config::alpha_val, ARRAY_SIZE, alpha_pll_reg_val_config::cal_l_val, CLK_100MHZ, clock_configure(), clock_configure_enable_gpll(), clock_enable(), alpha_pll_reg_val_config::fsm_enable, gcc, alpha_pll_reg_val_config::l_val, alpha_pll_reg_val_config::reg_alpha, alpha_pll_reg_val_config::reg_apcs_pll_br_en, alpha_pll_reg_val_config::reg_cal_l, alpha_pll_reg_val_config::reg_l, alpha_pll_reg_val_config::reg_mode, alpha_pll_reg_val_config::reg_opmode, and sdcc2_core_cfg.

Referenced by mainboard_init().

| void clock_enable_qup | ( | int | qup | ) |

Definition at line 273 of file clock.c.

References qupv3_clock::cbcr, clock_enable_vote(), gcc, QUP_WRAP1_S0, QUP_WRAP1_S6, QUPV3_WRAP0_CLK_ENA_S, QUPV3_WRAP1_CLK_ENA_1_S, QUPV3_WRAP1_CLK_ENA_S, and s.

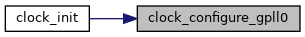

Definition at line 484 of file clock.c.

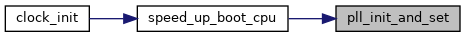

References clock_configure_gpll0(), clock_enable_vote(), gcc, QUPV3_WRAP0_CORE_2X_CLK_ENA, QUPV3_WRAP0_CORE_CLK_ENA, QUPV3_WRAP1_CORE_2X_CLK_ENA, QUPV3_WRAP1_CORE_CLK_ENA, QUPV3_WRAP_0_M_AHB_CLK_ENA, QUPV3_WRAP_0_S_AHB_CLK_ENA, QUPV3_WRAP_1_M_AHB_CLK_ENA, QUPV3_WRAP_1_S_AHB_CLK_ENA, and speed_up_boot_cpu().

|

static |

Definition at line 335 of file clock.c.

Referenced by speed_up_boot_cpu().

Definition at line 473 of file clock.c.

References apss_l3, apss_silver, BIOS_DEBUG, L_VAL_1190P4MHz, L_VAL_1516P8MHz, pll_init_and_set(), and printk.

Referenced by clock_init().

|

static |

|

static |

|

static |

|

static |

|

static |

Definition at line 1 of file clock.c.

Referenced by clock_configure_qspi().

|

static |

Definition at line 1 of file clock.c.

Referenced by clock_configure_dfsr().

|

static |

Definition at line 1 of file clock.c.

Referenced by clock_configure_sdcc1().

|

static |

Definition at line 1 of file clock.c.

Referenced by clock_configure_sdcc2().