|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

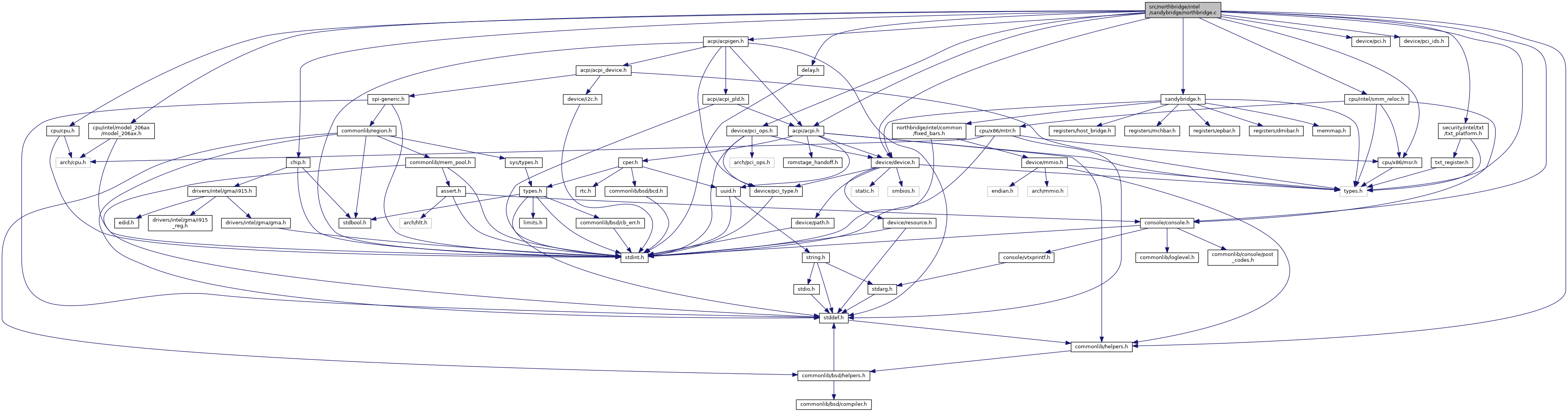

#include <cpu/cpu.h>#include <console/console.h>#include <acpi/acpi.h>#include <acpi/acpigen.h>#include <commonlib/helpers.h>#include <device/pci_ops.h>#include <delay.h>#include <cpu/intel/model_206ax/model_206ax.h>#include <cpu/x86/msr.h>#include <device/device.h>#include <device/pci.h>#include <device/pci_ids.h>#include <types.h>#include "chip.h"#include "sandybridge.h"#include <cpu/intel/smm_reloc.h>#include <security/intel/txt/txt_platform.h>

Go to the source code of this file.

Functions | |

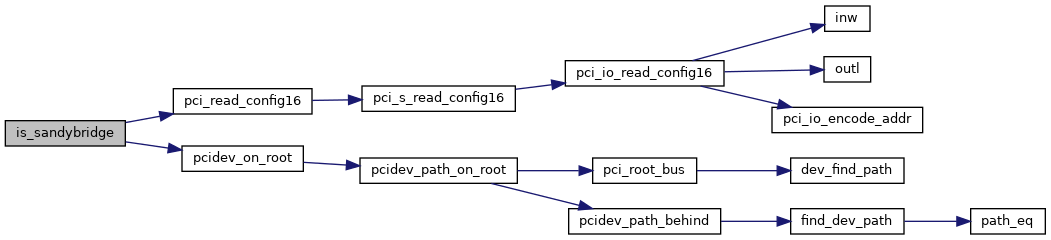

| bool | is_sandybridge (void) |

| static const char * | northbridge_acpi_name (const struct device *dev) |

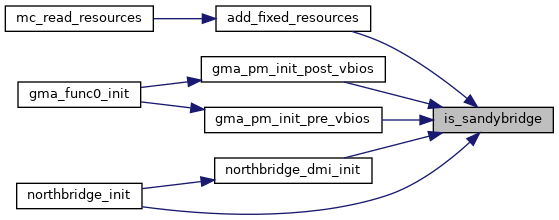

| static void | add_fixed_resources (struct device *dev, int index) |

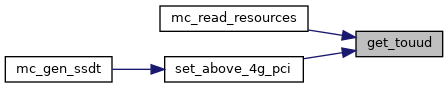

| static uint64_t | get_touud (const struct device *dev) |

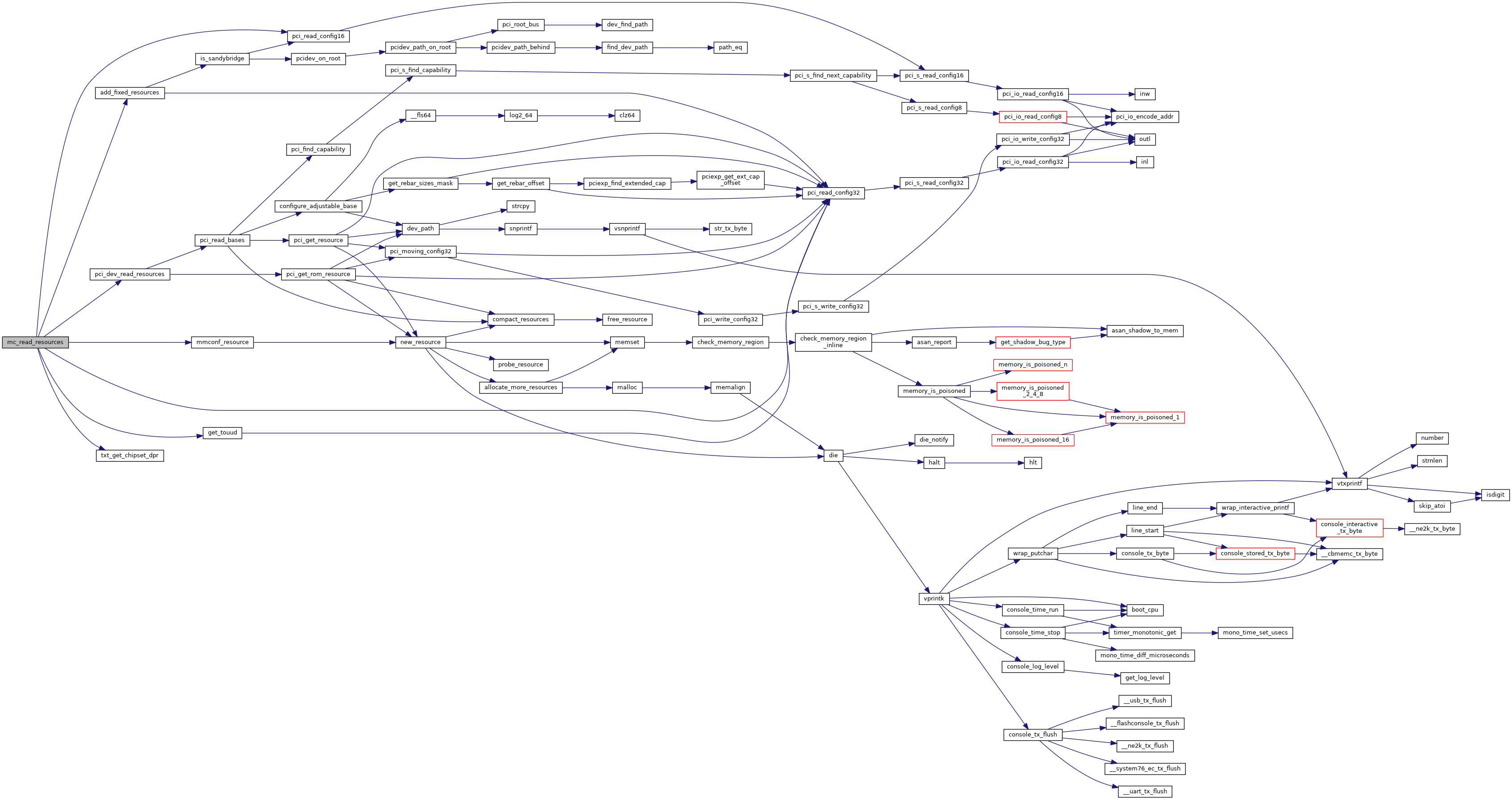

| static void | mc_read_resources (struct device *dev) |

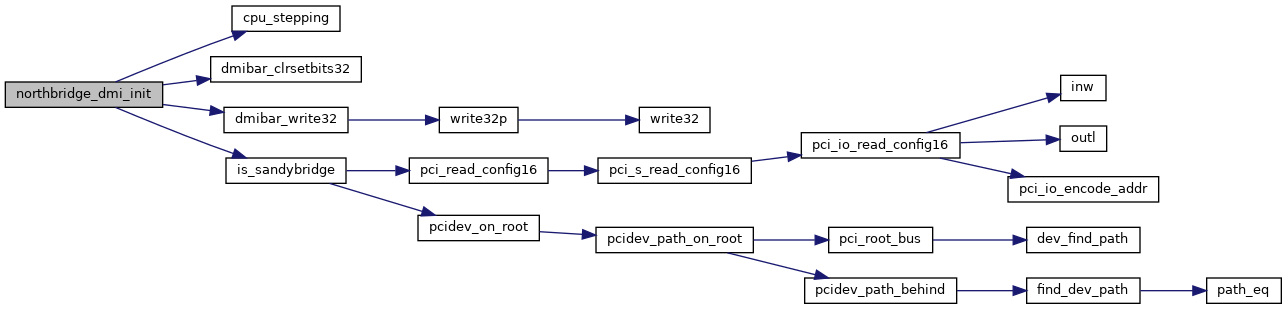

| static void | northbridge_dmi_init (struct device *dev) |

| static void | disable_peg (void) |

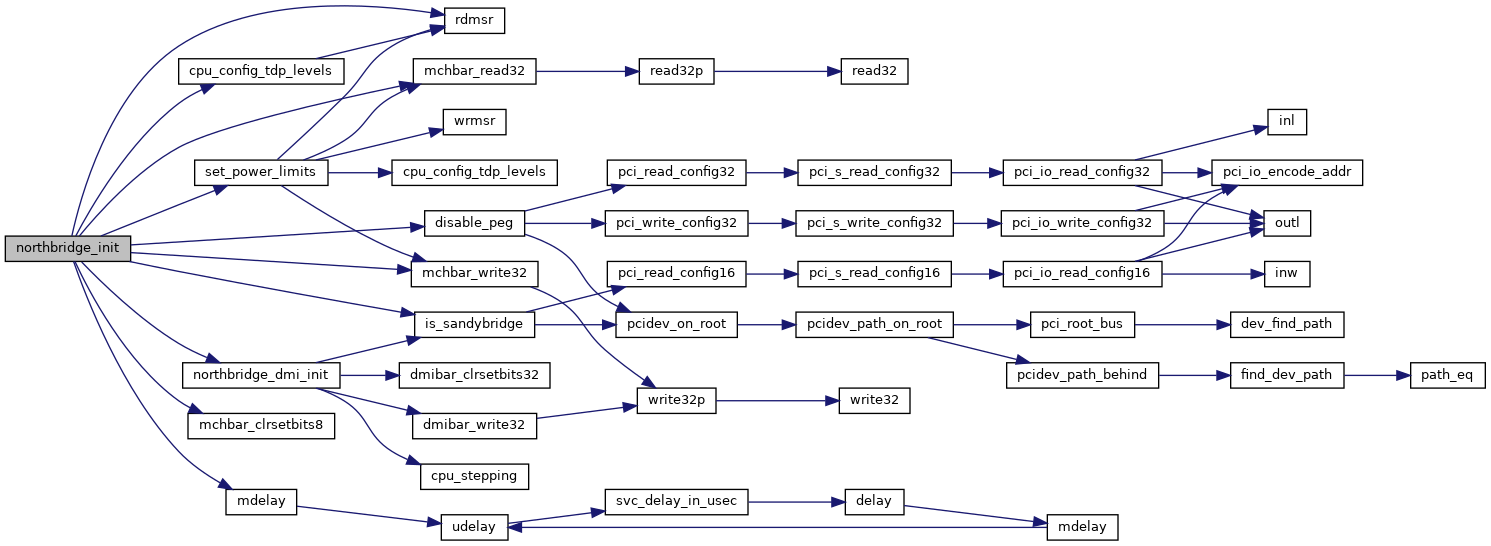

| static void | northbridge_init (struct device *dev) |

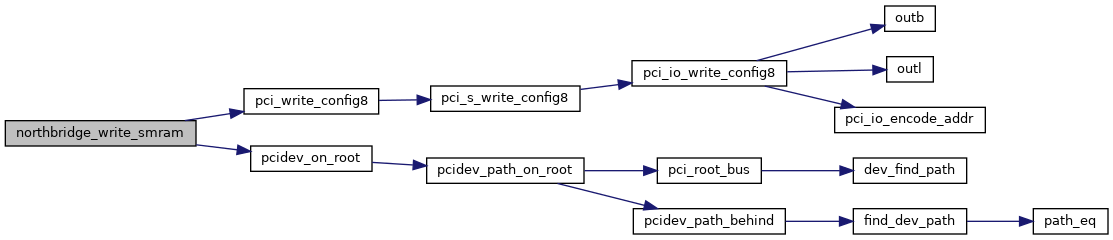

| void | northbridge_write_smram (u8 smram) |

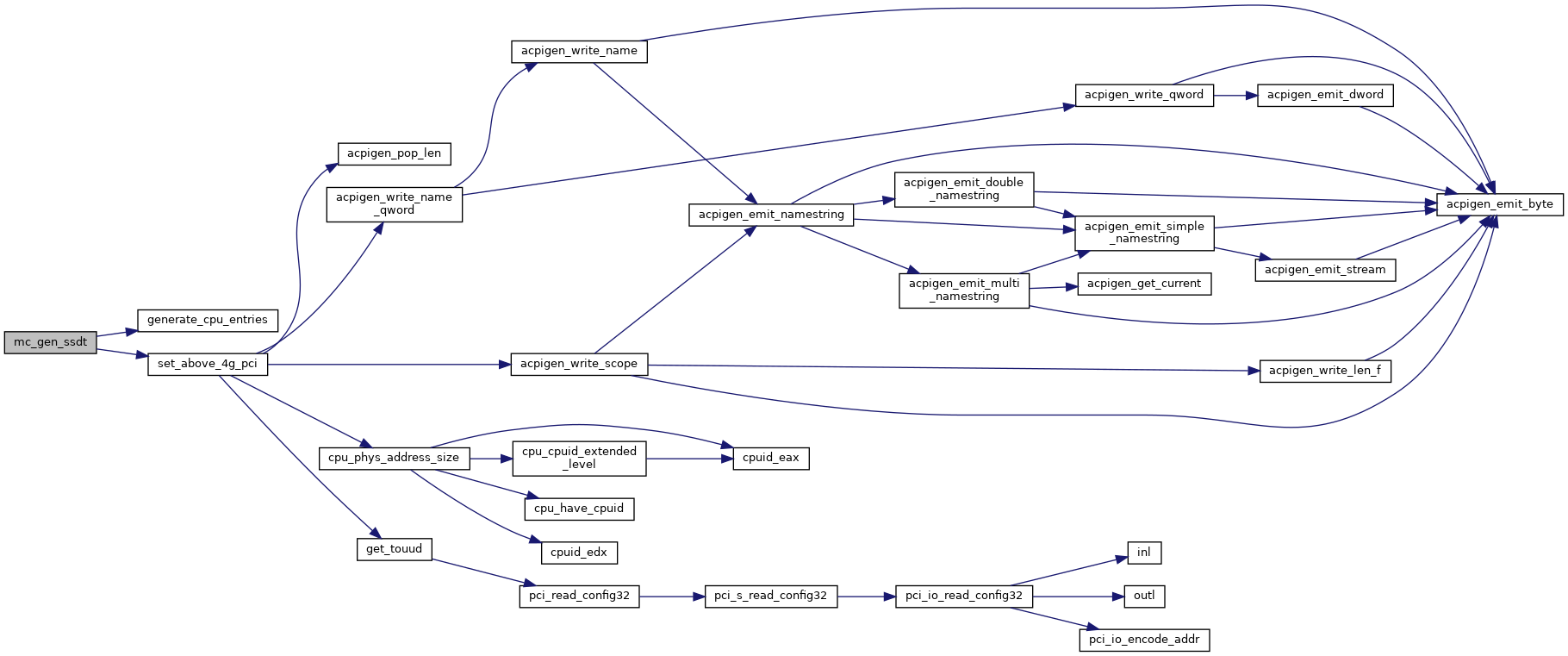

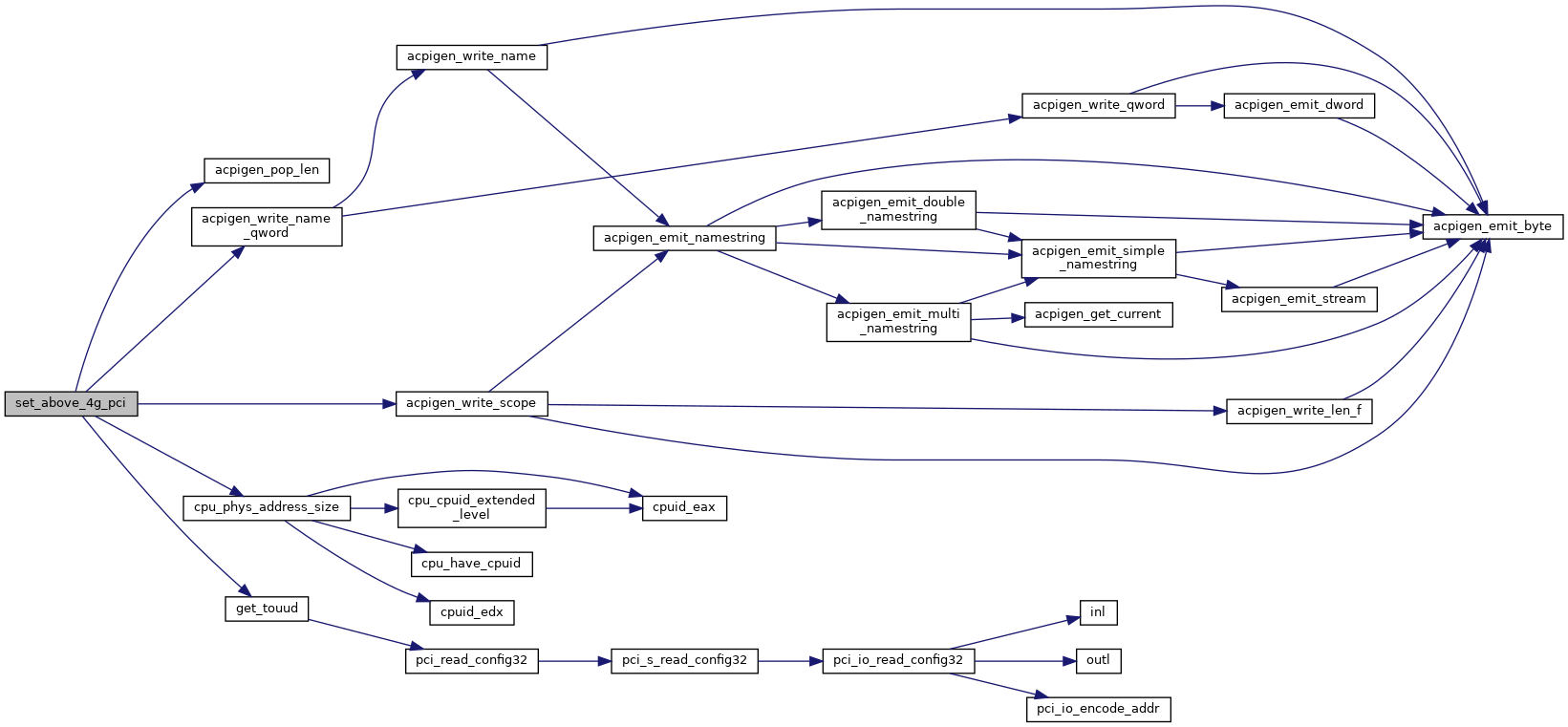

| static void | set_above_4g_pci (const struct device *dev) |

| static void | mc_gen_ssdt (const struct device *dev) |

| static void | enable_dev (struct device *dev) |

Variables | |

| static uint64_t | uma_memory_base = 0 |

| static uint64_t | uma_memory_size = 0 |

| static const int | legacy_hole_base_k = 0xa0000 / 1024 |

| static const int | legacy_hole_size_k = 384 |

| static struct device_operations | pci_domain_ops |

| static struct device_operations | mc_ops |

| static const unsigned short | pci_device_ids [] |

| static const struct pci_driver mc_driver | __pci_driver |

| static struct device_operations | cpu_bus_ops |

| struct chip_operations | northbridge_intel_sandybridge_ops |

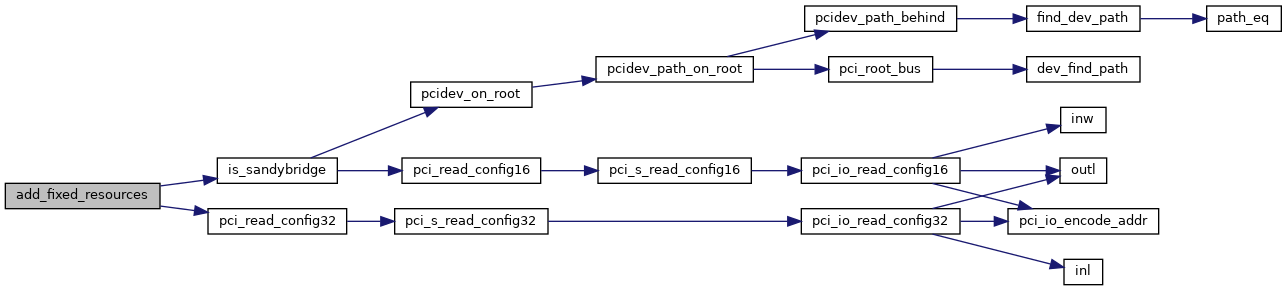

Definition at line 65 of file northbridge.c.

References bad_ram_resource, CAPID0_A, GFXVT_BASE, is_sandybridge(), legacy_hole_base_k, mmio_resource, pci_read_config32(), reserved_ram_resource, uma_memory_base, uma_memory_size, and VTVC0_BASE.

Referenced by mc_read_resources().

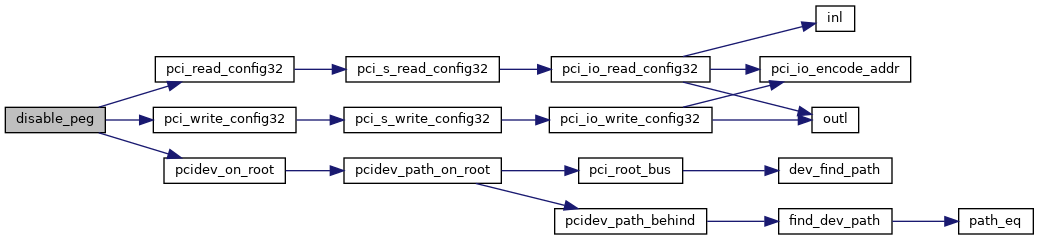

Definition at line 269 of file northbridge.c.

References BIOS_DEBUG, DEVEN, DEVEN_D4EN, DEVEN_D7EN, DEVEN_IGD, DEVEN_PEG10, DEVEN_PEG11, DEVEN_PEG12, DEVEN_PEG60, device::enabled, mchbar_clrbits32, mchbar_setbits32, pci_read_config32(), pci_write_config32(), pcidev_on_root(), PEGCTL, and printk.

Referenced by northbridge_init().

Definition at line 429 of file northbridge.c.

References cpu_bus_ops, DEVICE_PATH_CPU_CLUSTER, DEVICE_PATH_DOMAIN, device::ops, device::path, pci_domain_ops, and device_path::type.

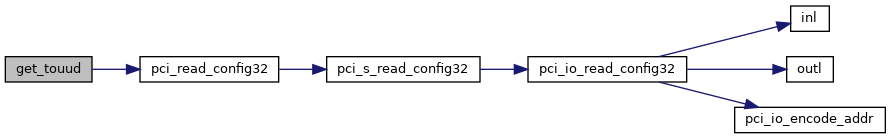

Definition at line 87 of file northbridge.c.

References pci_read_config32(), and TOUUD.

Referenced by mc_read_resources(), and set_above_4g_pci().

Definition at line 25 of file northbridge.c.

References BASE_REV_MASK, BASE_REV_SNB, PCI_DEVICE_ID, pci_read_config16(), and pcidev_on_root().

Referenced by add_fixed_resources(), gma_pm_init_post_vbios(), gma_pm_init_pre_vbios(), northbridge_dmi_init(), and northbridge_init().

Definition at line 396 of file northbridge.c.

References generate_cpu_entries(), and set_above_4g_pci().

Definition at line 95 of file northbridge.c.

References add_fixed_resources(), BIOS_DEBUG, BIOS_INFO, dpr_register::epm, get_touud(), GGC, KiB, legacy_hole_base_k, legacy_hole_size_k, MESEG_BASE, MiB, mmconf_resource(), pci_dev_read_resources(), pci_read_config16(), pci_read_config32(), PCIEXBAR, printk, ram_resource, reserved_ram_resource, dpr_register::size, TOLUD, TOM, TSEGMB, txt_get_chipset_dpr(), uma_memory_base, and uma_memory_size.

|

static |

Definition at line 41 of file northbridge.c.

References pci_path::devfn, DEVICE_PATH_DOMAIN, DEVICE_PATH_PCI, NULL, device::path, device_path::pci, PCI_DEVFN, and device_path::type.

Definition at line 227 of file northbridge.c.

References cpu_stepping(), dmibar_clrsetbits32(), dmibar_setbits32, dmibar_write32(), DMICESTS, DMILCTL, DMILLTC, DMIUESTS, is_sandybridge(), SNB_STEP_C0, SNB_STEP_D0, SNB_STEP_D1, and stepping.

Referenced by northbridge_init().

Definition at line 329 of file northbridge.c.

References BIOS_DEBUG, BIOS_RESET_CPL, cpu_config_tdp_levels(), disable_peg(), msr_struct::hi, INTRDIRCTL, is_sandybridge(), msr_struct::lo, MCH_PKG_POWER_LIMIT_HI, MCH_PKG_POWER_LIMIT_LO, mchbar_clrsetbits8(), mchbar_read32(), mchbar_setbits8, mchbar_write32(), mdelay(), MSR_PKG_POWER_LIMIT, northbridge_dmi_init(), PAVP_MSG, printk, rdmsr(), SAPMTIMERS, and set_power_limits().

Definition at line 378 of file northbridge.c.

References pci_write_config8(), pcidev_on_root(), and SMRAM.

Definition at line 383 of file northbridge.c.

References acpigen_pop_len(), acpigen_write_name_qword(), acpigen_write_scope(), BIOS_DEBUG, cpu_phys_address_size(), get_touud(), POWER_OF_2, and printk.

Referenced by mc_gen_ssdt().

|

static |

Definition at line 411 of file northbridge.c.

|

static |

Definition at line 411 of file northbridge.c.

Referenced by enable_dev().

|

static |

Definition at line 38 of file northbridge.c.

Referenced by add_fixed_resources(), and mc_read_resources().

|

static |

Definition at line 39 of file northbridge.c.

Referenced by mc_read_resources().

|

static |

Definition at line 396 of file northbridge.c.

| struct chip_operations northbridge_intel_sandybridge_ops |

Definition at line 429 of file northbridge.c.

|

static |

Definition at line 411 of file northbridge.c.

|

static |

Definition at line 41 of file northbridge.c.

Referenced by enable_dev().

|

static |

Definition at line 22 of file northbridge.c.

Referenced by add_fixed_resources(), mc_read_resources(), and mch_domain_read_resources().

|

static |

Definition at line 23 of file northbridge.c.

Referenced by add_fixed_resources(), mc_read_resources(), and mch_domain_read_resources().