|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

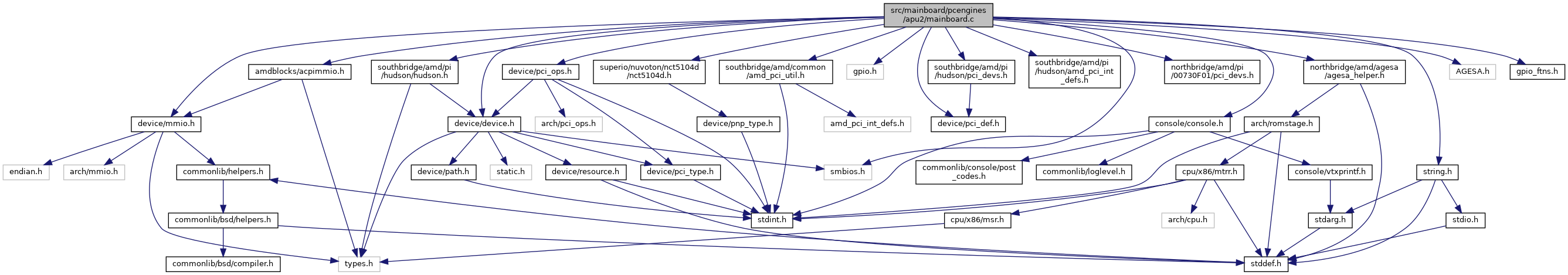

#include <amdblocks/acpimmio.h>#include <device/mmio.h>#include <device/pci_ops.h>#include <console/console.h>#include <device/device.h>#include <device/pci_def.h>#include <gpio.h>#include <southbridge/amd/pi/hudson/hudson.h>#include <southbridge/amd/pi/hudson/pci_devs.h>#include <southbridge/amd/pi/hudson/amd_pci_int_defs.h>#include <northbridge/amd/agesa/agesa_helper.h>#include <northbridge/amd/pi/00730F01/pci_devs.h>#include <southbridge/amd/common/amd_pci_util.h>#include <superio/nuvoton/nct5104d/nct5104d.h>#include <smbios.h>#include <string.h>#include <AGESA.h>#include "gpio_ftns.h"

Go to the source code of this file.

Macros | |

| #define | SPD_SIZE 128 |

| #define | PM_RTC_CONTROL 0x56 |

| #define | PM_S_STATE_CONTROL 0xBA |

| #define | SIO_PORT 0x2e |

Functions | |

| static void | pirq_setup (void) |

| static void | config_gpio_mux (void) |

| static void | mainboard_enable (struct device *dev) |

| static void | mainboard_final (void *chip_info) |

| const char * | smbios_mainboard_serial_number (void) |

| const char * | smbios_system_sku (void) |

Variables | |

| static const u8 | mainboard_picr_data [FCH_INT_TABLE_SIZE] |

| static const u8 | mainboard_intr_data [FCH_INT_TABLE_SIZE] |

| static const struct pirq_struct | mainboard_pirq_data [] |

| struct chip_operations | mainboard_ops |

| #define PM_RTC_CONTROL 0x56 |

Definition at line 23 of file mainboard.c.

| #define PM_S_STATE_CONTROL 0xBA |

Definition at line 24 of file mainboard.c.

| #define SIO_PORT 0x2e |

Definition at line 125 of file mainboard.c.

| #define SPD_SIZE 128 |

Definition at line 22 of file mainboard.c.

Definition at line 127 of file mainboard.c.

References CONFIG, dev_find_slot_pnp(), device::enabled, NCT5104D_GPIO0, NCT5104D_GPIO1, NCT5104D_SP3, NCT5104D_SP4, and SIO_PORT.

Referenced by mainboard_enable().

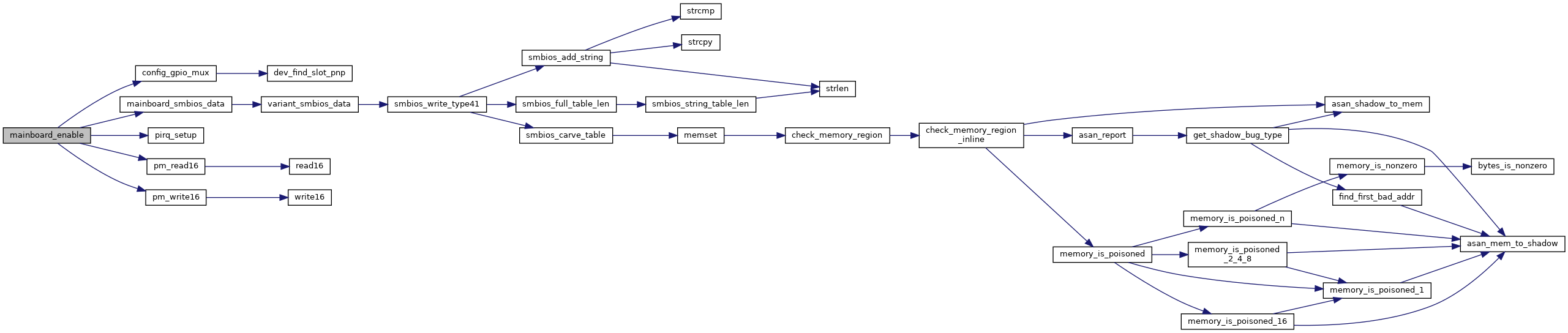

Definition at line 226 of file mainboard.c.

References BIOS_INFO, config_gpio_mux(), mainboard_smbios_data(), device::ops, pirq_setup(), pm_read16(), PM_RTC_CONTROL, PM_S_STATE_CONTROL, pm_write16(), and printk.

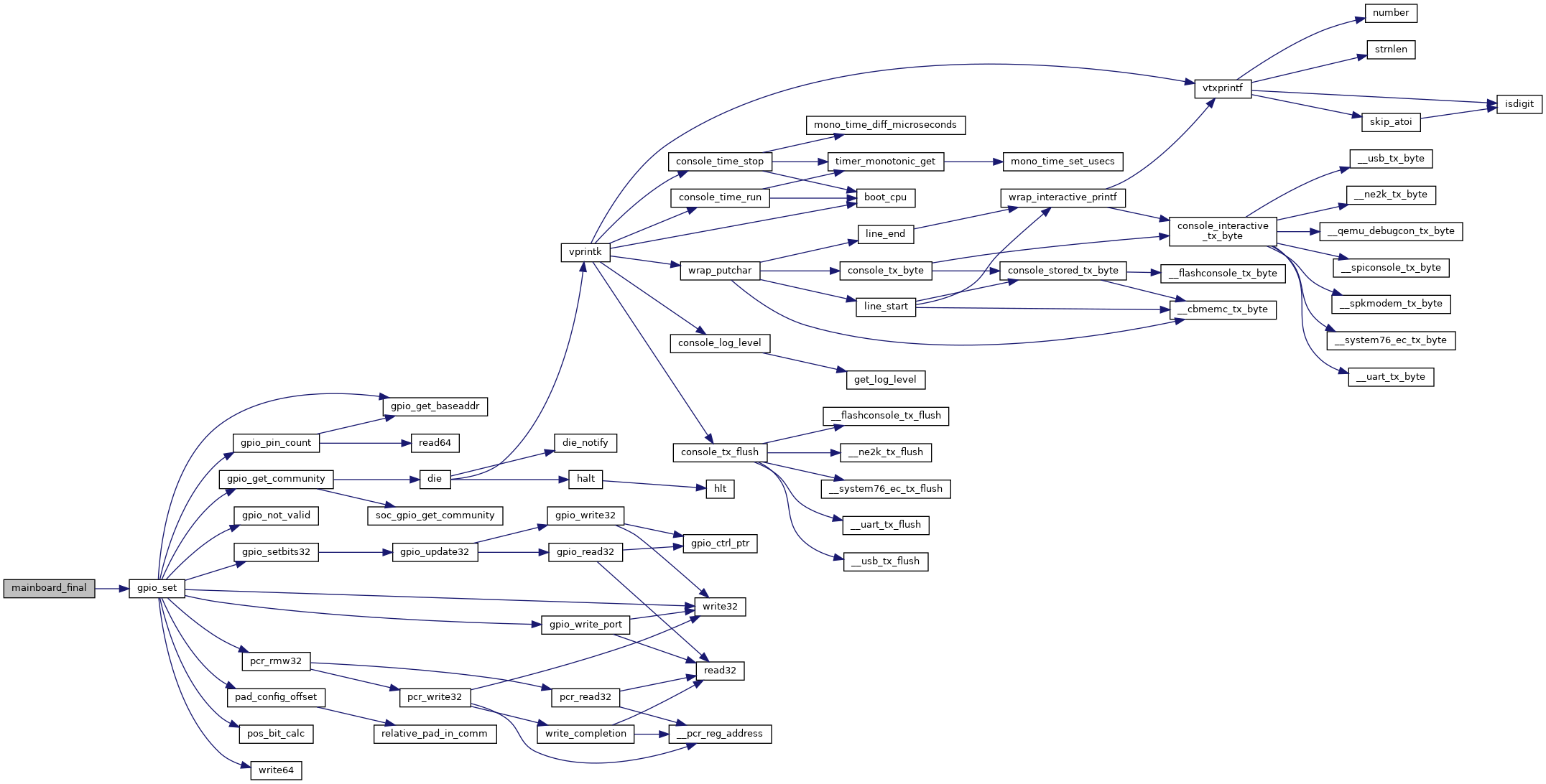

Definition at line 250 of file mainboard.c.

References GPIO_58, GPIO_59, and gpio_set().

Definition at line 114 of file mainboard.c.

References ARRAY_SIZE, intr_data_ptr, mainboard_intr_data, mainboard_picr_data, mainboard_pirq_data, picr_data_ptr, pirq_data_ptr, and pirq_data_size.

Referenced by mainboard_enable().

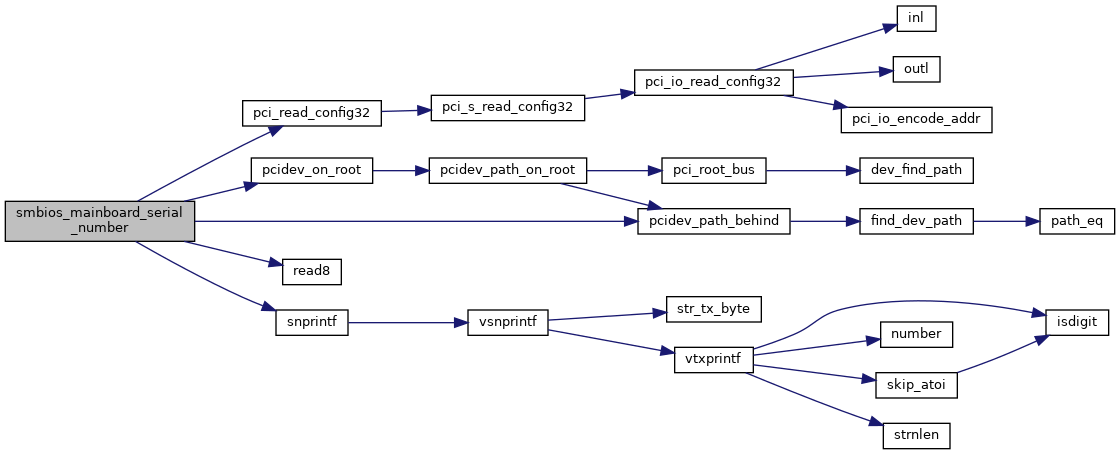

| const char* smbios_mainboard_serial_number | ( | void | ) |

Definition at line 263 of file mainboard.c.

References device::link_list, PCI_BASE_ADDRESS_0, PCI_DEVFN, pci_read_config32(), pcidev_on_root(), pcidev_path_behind(), read8(), serial, and snprintf().

| const char* smbios_system_sku | ( | void | ) |

Definition at line 300 of file mainboard.c.

|

static |

Definition at line 60 of file mainboard.c.

Referenced by pirq_setup().

| struct chip_operations mainboard_ops |

Definition at line 300 of file mainboard.c.

|

static |

Definition at line 37 of file mainboard.c.

Referenced by pirq_setup().

|

static |