|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

Go to the source code of this file.

Macros | |

| #define | DEFAULT_GPIOBASE 0x0480 |

| #define | DEFAULT_PMBASE 0x0500 |

| #define | DEBUG_PERIODIC_SMIS 0 |

| #define | MAINBOARD_POWER_OFF 0 |

| #define | MAINBOARD_POWER_ON 1 |

| #define | MAINBOARD_POWER_KEEP 2 |

| #define | PSTS 0x06 |

| #define | SMLT 0x1b |

| #define | SECSTS 0x1e |

| #define | INTR 0x3c |

| #define | ICH_PCIE_DEV_SLOT 28 |

| #define | SERIRQ_CNTL 0x64 |

| #define | GEN_PMCON_1 0xa0 |

| #define | GEN_PMCON_2 0xa2 |

| #define | GEN_PMCON_3 0xa4 |

| #define | GPIO_ROUT 0xb8 |

| #define | GPI_DISABLE 0x00 |

| #define | GPI_IS_SMI 0x01 |

| #define | GPI_IS_SCI 0x02 |

| #define | GPI_IS_NMI 0x03 |

| #define | FDVCT 0xe4 |

| #define | PCIE_4_PORTS_MAX (1 << 7) |

| #define | AHCI_UNSUPPORTED (1 << 3) |

| #define | RTC_BATTERY_DEAD (1 << 2) |

| #define | RTC_POWER_FAILED (1 << 1) |

| #define | SLEEP_AFTER_POWER_FAIL (1 << 0) |

| #define | ACPI_CNTL 0x44 |

| #define | ACPI_EN (1 << 7) |

| #define | BIOS_CNTL 0xDC |

| #define | GPIO_BASE 0x48 /* LPC GPIO Base Address Register */ |

| #define | GPIO_CNTL 0x4C /* LPC GPIO Control Register */ |

| #define | GPIO_EN (1 << 4) |

| #define | PIRQA_ROUT 0x60 |

| #define | PIRQB_ROUT 0x61 |

| #define | PIRQC_ROUT 0x62 |

| #define | PIRQD_ROUT 0x63 |

| #define | PIRQE_ROUT 0x68 |

| #define | PIRQF_ROUT 0x69 |

| #define | PIRQG_ROUT 0x6A |

| #define | PIRQH_ROUT 0x6B |

| #define | LPC_IO_DEC 0x80 /* IO Decode Ranges Register */ |

| #define | LPC_EN 0x82 /* LPC IF Enables Register */ |

| #define | CNF2_LPC_EN (1 << 13) /* 0x4e/0x4f */ |

| #define | CNF1_LPC_EN (1 << 12) /* 0x2e/0x2f */ |

| #define | MC_LPC_EN (1 << 11) /* 0x62/0x66 */ |

| #define | KBC_LPC_EN (1 << 10) /* 0x60/0x64 */ |

| #define | GAMEH_LPC_EN (1 << 9) /* 0x208/0x20f */ |

| #define | GAMEL_LPC_EN (1 << 8) /* 0x200/0x207 */ |

| #define | FDD_LPC_EN (1 << 3) /* LPC_IO_DEC[12] */ |

| #define | LPT_LPC_EN (1 << 2) /* LPC_IO_DEC[9:8] */ |

| #define | COMB_LPC_EN (1 << 1) /* LPC_IO_DEC[6:4] */ |

| #define | COMA_LPC_EN (1 << 0) /* LPC_IO_DEC[2:0] */ |

| #define | GEN1_DEC 0x84 |

| #define | GEN2_DEC 0x88 |

| #define | GEN3_DEC 0x8c |

| #define | GEN4_DEC 0x90 |

| #define | INTR_LN 0x3c |

| #define | IDE_TIM_PRI 0x40 /* IDE timings, primary */ |

| #define | IDE_DECODE_ENABLE (1 << 15) |

| #define | IDE_SITRE (1 << 14) |

| #define | IDE_ISP_5_CLOCKS (0 << 12) |

| #define | IDE_ISP_4_CLOCKS (1 << 12) |

| #define | IDE_ISP_3_CLOCKS (2 << 12) |

| #define | IDE_RCT_4_CLOCKS (0 << 8) |

| #define | IDE_RCT_3_CLOCKS (1 << 8) |

| #define | IDE_RCT_2_CLOCKS (2 << 8) |

| #define | IDE_RCT_1_CLOCKS (3 << 8) |

| #define | IDE_DTE1 (1 << 7) |

| #define | IDE_PPE1 (1 << 6) |

| #define | IDE_IE1 (1 << 5) |

| #define | IDE_TIME1 (1 << 4) |

| #define | IDE_DTE0 (1 << 3) |

| #define | IDE_PPE0 (1 << 2) |

| #define | IDE_IE0 (1 << 1) |

| #define | IDE_TIME0 (1 << 0) |

| #define | IDE_TIM_SEC 0x42 /* IDE timings, secondary */ |

| #define | IDE_SDMA_CNT 0x48 /* Synchronous DMA control */ |

| #define | IDE_SSDE1 (1 << 3) |

| #define | IDE_SSDE0 (1 << 2) |

| #define | IDE_PSDE1 (1 << 1) |

| #define | IDE_PSDE0 (1 << 0) |

| #define | IDE_SDMA_TIM 0x4a |

| #define | IDE_CONFIG 0x54 /* IDE I/O Configuration Register */ |

| #define | SIG_MODE_SEC_NORMAL (0 << 18) |

| #define | SIG_MODE_SEC_TRISTATE (1 << 18) |

| #define | SIG_MODE_SEC_DRIVELOW (2 << 18) |

| #define | SIG_MODE_PRI_NORMAL (0 << 16) |

| #define | SIG_MODE_PRI_TRISTATE (1 << 16) |

| #define | SIG_MODE_PRI_DRIVELOW (2 << 16) |

| #define | FAST_SCB1 (1 << 15) |

| #define | FAST_SCB0 (1 << 14) |

| #define | FAST_PCB1 (1 << 13) |

| #define | FAST_PCB0 (1 << 12) |

| #define | SCB1 (1 << 3) |

| #define | SCB0 (1 << 2) |

| #define | PCB1 (1 << 1) |

| #define | PCB0 (1 << 0) |

| #define | SMB_BASE 0x20 |

| #define | HOSTC 0x40 |

| #define | I2C_EN (1 << 2) |

| #define | SMB_SMI_EN (1 << 1) |

| #define | HST_EN (1 << 0) |

| #define | GPIOBASE 0x48 |

| #define | PMBASE 0x40 |

| #define | VCH 0x0000 /* 32bit */ |

| #define | VCAP1 0x0004 /* 32bit */ |

| #define | VCAP2 0x0008 /* 32bit */ |

| #define | PVC 0x000c /* 16bit */ |

| #define | PVS 0x000e /* 16bit */ |

| #define | V0CAP 0x0010 /* 32bit */ |

| #define | V0CTL 0x0014 /* 32bit */ |

| #define | V0STS 0x001a /* 16bit */ |

| #define | V1CAP 0x001c /* 32bit */ |

| #define | V1CTL 0x0020 /* 32bit */ |

| #define | V1STS 0x0026 /* 16bit */ |

| #define | RCTCL 0x0100 /* 32bit */ |

| #define | ESD 0x0104 /* 32bit */ |

| #define | ULD 0x0110 /* 32bit */ |

| #define | ULBA 0x0118 /* 64bit */ |

| #define | RP1D 0x0120 /* 32bit */ |

| #define | RP1BA 0x0128 /* 64bit */ |

| #define | RP2D 0x0130 /* 32bit */ |

| #define | RP2BA 0x0138 /* 64bit */ |

| #define | RP3D 0x0140 /* 32bit */ |

| #define | RP3BA 0x0148 /* 64bit */ |

| #define | RP4D 0x0150 /* 32bit */ |

| #define | RP4BA 0x0158 /* 64bit */ |

| #define | HDD 0x0160 /* 32bit */ |

| #define | HDBA 0x0168 /* 64bit */ |

| #define | RP5D 0x0170 /* 32bit */ |

| #define | RP5BA 0x0178 /* 64bit */ |

| #define | RP6D 0x0180 /* 32bit */ |

| #define | RP6BA 0x0188 /* 64bit */ |

| #define | ILCL 0x01a0 /* 32bit */ |

| #define | LCAP 0x01a4 /* 32bit */ |

| #define | LCTL 0x01a8 /* 16bit */ |

| #define | LSTS 0x01aa /* 16bit */ |

| #define | RPC 0x0224 /* 32bit */ |

| #define | RPFN 0x0238 /* 32bit */ |

| #define | RPFN_FNGET(reg, port) (((reg) >> ((port) * 4)) & 7) |

| #define | RPFN_FNSET(port, func) (((func) & 7) << ((port) * 4)) |

| #define | RPFN_FNMASK(port) (7 << ((port) * 4)) |

| #define | TRSR 0x1e00 /* 8bit */ |

| #define | TRCR 0x1e10 /* 64bit */ |

| #define | TWDR 0x1e18 /* 64bit */ |

| #define | IOTR0 0x1e80 /* 64bit */ |

| #define | IOTR1 0x1e88 /* 64bit */ |

| #define | IOTR2 0x1e90 /* 64bit */ |

| #define | IOTR3 0x1e98 /* 64bit */ |

| #define | TCTL 0x3000 /* 8bit */ |

| #define | D31IP 0x3100 /* 32bit */ |

| #define | D30IP 0x3104 /* 32bit */ |

| #define | D29IP 0x3108 /* 32bit */ |

| #define | D28IP 0x310c /* 32bit */ |

| #define | D27IP 0x3110 /* 32bit */ |

| #define | D31IR 0x3140 /* 16bit */ |

| #define | D30IR 0x3142 /* 16bit */ |

| #define | D29IR 0x3144 /* 16bit */ |

| #define | D28IR 0x3146 /* 16bit */ |

| #define | D27IR 0x3148 /* 16bit */ |

| #define | OIC 0x31ff /* 8bit */ |

| #define | RC 0x3400 /* 32bit */ |

| #define | HPTC 0x3404 /* 32bit */ |

| #define | GCS 0x3410 /* 32bit */ |

| #define | BUC 0x3414 /* 32bit */ |

| #define | FD 0x3418 /* 32bit */ |

| #define | CG 0x341c /* 32bit */ |

| #define | ICH_DISABLE_PCIE(x) (1 << (16 + (x))) |

| #define | FD_EHCI (1 << 15) |

| #define | FD_LPCB (1 << 14) |

| #define | ICH_DISABLE_UHCI(x) (1 << (8 + (x))) |

| #define | FD_INTLAN (1 << 7) |

| #define | FD_ACMOD (1 << 6) |

| #define | FD_ACAUD (1 << 5) |

| #define | FD_HDAUD (1 << 4) |

| #define | FD_SMBUS (1 << 3) |

| #define | FD_SATA (1 << 2) |

| #define | FD_PATA (1 << 1) |

| #define | PM1_STS 0x00 |

| #define | WAK_STS (1 << 15) |

| #define | PCIEXPWAK_STS (1 << 14) |

| #define | PRBTNOR_STS (1 << 11) |

| #define | RTC_STS (1 << 10) |

| #define | PWRBTN_STS (1 << 8) |

| #define | GBL_STS (1 << 5) |

| #define | BM_STS (1 << 4) |

| #define | TMROF_STS (1 << 0) |

| #define | PM1_EN 0x02 |

| #define | PCIEXPWAK_DIS (1 << 14) |

| #define | RTC_EN (1 << 10) |

| #define | PWRBTN_EN (1 << 8) |

| #define | GBL_EN (1 << 5) |

| #define | TMROF_EN (1 << 0) |

| #define | PM1_CNT 0x04 |

| #define | GBL_RLS (1 << 2) |

| #define | BM_RLD (1 << 1) |

| #define | SCI_EN (1 << 0) |

| #define | PM1_TMR 0x08 |

| #define | PROC_CNT 0x10 |

| #define | LV2 0x14 |

| #define | LV3 0x15 |

| #define | LV4 0x16 |

| #define | PM2_CNT 0x20 |

| #define | GPE0_STS 0x28 |

| #define | USB4_STS (1 << 14) |

| #define | PME_B0_STS (1 << 13) |

| #define | USB3_STS (1 << 12) |

| #define | PME_STS (1 << 11) |

| #define | BATLOW_STS (1 << 10) |

| #define | PCI_EXP_STS (1 << 9) |

| #define | RI_STS (1 << 8) |

| #define | SMB_WAK_STS (1 << 7) |

| #define | TCOSCI_STS (1 << 6) |

| #define | AC97_STS (1 << 5) |

| #define | USB2_STS (1 << 4) |

| #define | USB1_STS (1 << 3) |

| #define | SWGPE_STS (1 << 2) |

| #define | HOT_PLUG_STS (1 << 1) |

| #define | THRM_STS (1 << 0) |

| #define | GPE0_EN 0x2c |

| #define | PME_B0_EN (1 << 13) |

| #define | PME_EN (1 << 11) |

| #define | SMI_EN 0x30 |

| #define | EL_SMI_EN (1 << 25) |

| #define | INTEL_USB2_EN (1 << 18) |

| #define | LEGACY_USB2_EN (1 << 17) |

| #define | PERIODIC_EN (1 << 14) |

| #define | TCO_EN (1 << 13) |

| #define | MCSMI_EN (1 << 11) |

| #define | BIOS_RLS (1 << 7) |

| #define | SWSMI_TMR_EN (1 << 6) |

| #define | APMC_EN (1 << 5) |

| #define | SLP_SMI_EN (1 << 4) |

| #define | LEGACY_USB_EN (1 << 3) |

| #define | BIOS_EN (1 << 2) |

| #define | EOS (1 << 1) |

| #define | GBL_SMI_EN (1 << 0) |

| #define | SMI_STS 0x34 |

| #define | ALT_GP_SMI_EN 0x38 |

| #define | ALT_GP_SMI_STS 0x3a |

| #define | GPE_CNTL 0x42 |

| #define | DEVACT_STS 0x44 |

| #define | SS_CNT 0x50 |

| #define | C3_RES 0x54 |

| #define | TCO1_CNT 0x68 |

Functions | |

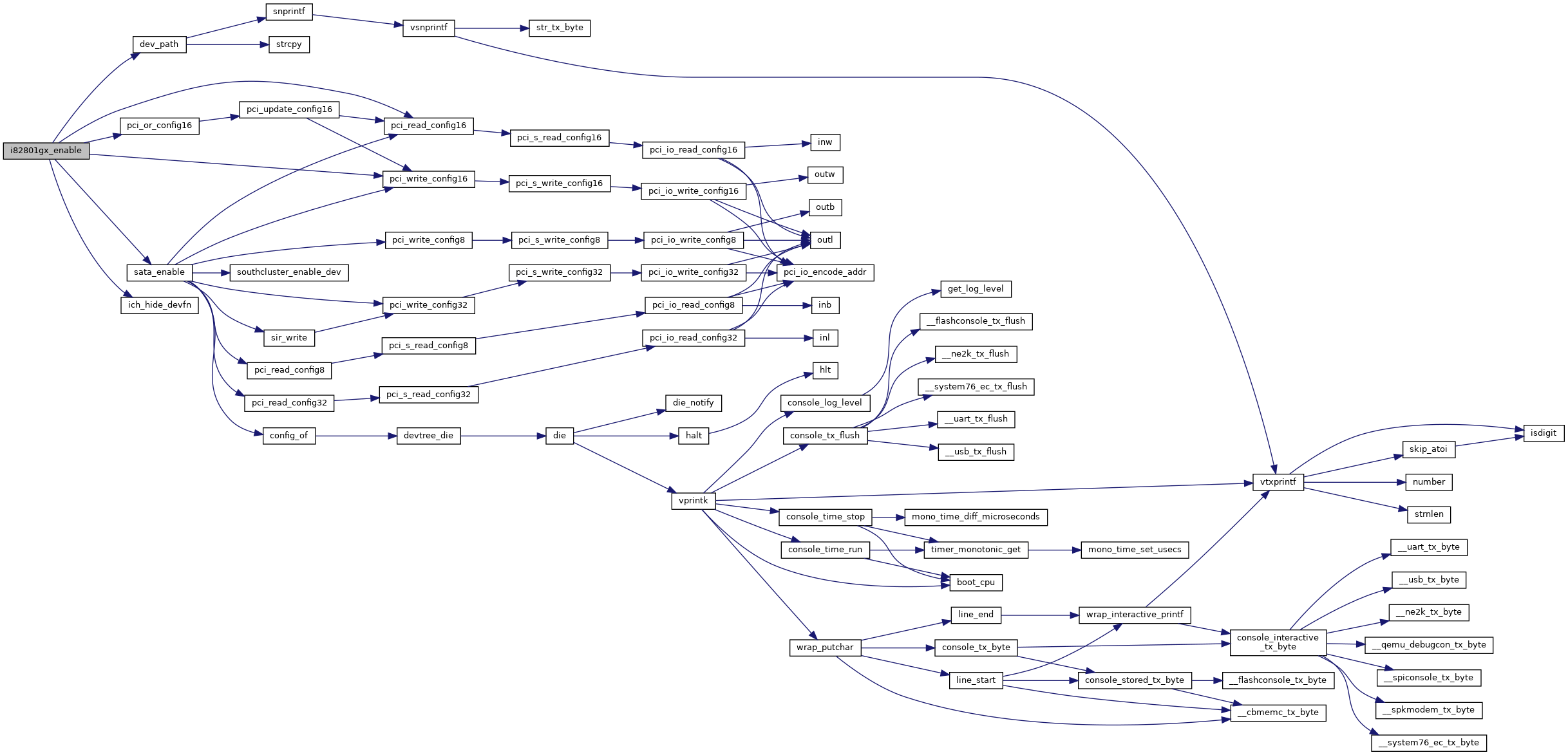

| void | i82801gx_enable (struct device *dev) |

| void | i82801gx_lpc_setup (void) |

| void | i82801gx_setup_bars (void) |

| void | i82801gx_early_init (void) |

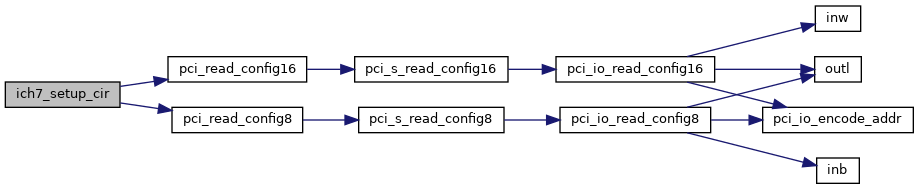

| void | ich7_setup_cir (void) |

| #define AC97_STS (1 << 5) |

Definition at line 292 of file i82801gx.h.

| #define ACPI_CNTL 0x44 |

Definition at line 59 of file i82801gx.h.

| #define ACPI_EN (1 << 7) |

Definition at line 60 of file i82801gx.h.

| #define AHCI_UNSUPPORTED (1 << 3) |

Definition at line 52 of file i82801gx.h.

| #define ALT_GP_SMI_EN 0x38 |

Definition at line 317 of file i82801gx.h.

| #define ALT_GP_SMI_STS 0x3a |

Definition at line 318 of file i82801gx.h.

| #define APMC_EN (1 << 5) |

Definition at line 310 of file i82801gx.h.

| #define BATLOW_STS (1 << 10) |

Definition at line 287 of file i82801gx.h.

| #define BIOS_CNTL 0xDC |

Definition at line 61 of file i82801gx.h.

| #define BIOS_EN (1 << 2) |

Definition at line 313 of file i82801gx.h.

| #define BIOS_RLS (1 << 7) |

Definition at line 308 of file i82801gx.h.

| #define BM_RLD (1 << 1) |

Definition at line 274 of file i82801gx.h.

| #define BM_STS (1 << 4) |

Definition at line 264 of file i82801gx.h.

| #define BUC 0x3414 /* 32bit */ |

Definition at line 229 of file i82801gx.h.

| #define C3_RES 0x54 |

Definition at line 322 of file i82801gx.h.

| #define CG 0x341c /* 32bit */ |

Definition at line 231 of file i82801gx.h.

| #define CNF1_LPC_EN (1 << 12) /* 0x2e/0x2f */ |

Definition at line 78 of file i82801gx.h.

| #define CNF2_LPC_EN (1 << 13) /* 0x4e/0x4f */ |

Definition at line 77 of file i82801gx.h.

| #define COMA_LPC_EN (1 << 0) /* LPC_IO_DEC[2:0] */ |

Definition at line 86 of file i82801gx.h.

| #define COMB_LPC_EN (1 << 1) /* LPC_IO_DEC[6:4] */ |

Definition at line 85 of file i82801gx.h.

| #define D27IP 0x3110 /* 32bit */ |

Definition at line 218 of file i82801gx.h.

| #define D27IR 0x3148 /* 16bit */ |

Definition at line 223 of file i82801gx.h.

| #define D28IP 0x310c /* 32bit */ |

Definition at line 217 of file i82801gx.h.

| #define D28IR 0x3146 /* 16bit */ |

Definition at line 222 of file i82801gx.h.

| #define D29IP 0x3108 /* 32bit */ |

Definition at line 216 of file i82801gx.h.

| #define D29IR 0x3144 /* 16bit */ |

Definition at line 221 of file i82801gx.h.

| #define D30IP 0x3104 /* 32bit */ |

Definition at line 215 of file i82801gx.h.

| #define D30IR 0x3142 /* 16bit */ |

Definition at line 220 of file i82801gx.h.

| #define D31IP 0x3100 /* 32bit */ |

Definition at line 214 of file i82801gx.h.

| #define D31IR 0x3140 /* 16bit */ |

Definition at line 219 of file i82801gx.h.

| #define DEBUG_PERIODIC_SMIS 0 |

Definition at line 13 of file i82801gx.h.

| #define DEFAULT_GPIOBASE 0x0480 |

Definition at line 7 of file i82801gx.h.

| #define DEFAULT_PMBASE 0x0500 |

Definition at line 8 of file i82801gx.h.

| #define DEVACT_STS 0x44 |

Definition at line 320 of file i82801gx.h.

| #define EL_SMI_EN (1 << 25) |

Definition at line 302 of file i82801gx.h.

| #define EOS (1 << 1) |

Definition at line 314 of file i82801gx.h.

| #define ESD 0x0104 /* 32bit */ |

Definition at line 169 of file i82801gx.h.

| #define FAST_PCB0 (1 << 12) |

Definition at line 133 of file i82801gx.h.

| #define FAST_PCB1 (1 << 13) |

Definition at line 132 of file i82801gx.h.

| #define FAST_SCB0 (1 << 14) |

Definition at line 131 of file i82801gx.h.

| #define FAST_SCB1 (1 << 15) |

Definition at line 130 of file i82801gx.h.

| #define FD 0x3418 /* 32bit */ |

Definition at line 230 of file i82801gx.h.

| #define FD_ACAUD (1 << 5) |

Definition at line 250 of file i82801gx.h.

| #define FD_ACMOD (1 << 6) |

Definition at line 249 of file i82801gx.h.

| #define FD_EHCI (1 << 15) |

Definition at line 240 of file i82801gx.h.

| #define FD_HDAUD (1 << 4) |

Definition at line 251 of file i82801gx.h.

| #define FD_INTLAN (1 << 7) |

Definition at line 248 of file i82801gx.h.

| #define FD_LPCB (1 << 14) |

Definition at line 241 of file i82801gx.h.

| #define FD_PATA (1 << 1) |

Definition at line 254 of file i82801gx.h.

| #define FD_SATA (1 << 2) |

Definition at line 253 of file i82801gx.h.

| #define FD_SMBUS (1 << 3) |

Definition at line 252 of file i82801gx.h.

| #define FDD_LPC_EN (1 << 3) /* LPC_IO_DEC[12] */ |

Definition at line 83 of file i82801gx.h.

| #define FDVCT 0xe4 |

Definition at line 50 of file i82801gx.h.

| #define GAMEH_LPC_EN (1 << 9) /* 0x208/0x20f */ |

Definition at line 81 of file i82801gx.h.

| #define GAMEL_LPC_EN (1 << 8) /* 0x200/0x207 */ |

Definition at line 82 of file i82801gx.h.

| #define GBL_EN (1 << 5) |

Definition at line 270 of file i82801gx.h.

| #define GBL_RLS (1 << 2) |

Definition at line 273 of file i82801gx.h.

| #define GBL_SMI_EN (1 << 0) |

Definition at line 315 of file i82801gx.h.

| #define GBL_STS (1 << 5) |

Definition at line 263 of file i82801gx.h.

| #define GCS 0x3410 /* 32bit */ |

Definition at line 228 of file i82801gx.h.

| #define GEN1_DEC 0x84 |

Definition at line 88 of file i82801gx.h.

| #define GEN2_DEC 0x88 |

Definition at line 89 of file i82801gx.h.

| #define GEN3_DEC 0x8c |

Definition at line 90 of file i82801gx.h.

| #define GEN4_DEC 0x90 |

Definition at line 91 of file i82801gx.h.

| #define GEN_PMCON_1 0xa0 |

Definition at line 40 of file i82801gx.h.

| #define GEN_PMCON_2 0xa2 |

Definition at line 41 of file i82801gx.h.

| #define GEN_PMCON_3 0xa4 |

Definition at line 42 of file i82801gx.h.

| #define GPE0_EN 0x2c |

Definition at line 298 of file i82801gx.h.

| #define GPE0_STS 0x28 |

Definition at line 282 of file i82801gx.h.

| #define GPE_CNTL 0x42 |

Definition at line 319 of file i82801gx.h.

| #define GPI_DISABLE 0x00 |

Definition at line 45 of file i82801gx.h.

| #define GPI_IS_NMI 0x03 |

Definition at line 48 of file i82801gx.h.

| #define GPI_IS_SCI 0x02 |

Definition at line 47 of file i82801gx.h.

| #define GPI_IS_SMI 0x01 |

Definition at line 46 of file i82801gx.h.

Definition at line 62 of file i82801gx.h.

Definition at line 63 of file i82801gx.h.

| #define GPIO_EN (1 << 4) |

Definition at line 64 of file i82801gx.h.

| #define GPIO_ROUT 0xb8 |

Definition at line 44 of file i82801gx.h.

| #define GPIOBASE 0x48 |

Definition at line 150 of file i82801gx.h.

| #define HDBA 0x0168 /* 64bit */ |

Definition at line 182 of file i82801gx.h.

| #define HDD 0x0160 /* 32bit */ |

Definition at line 181 of file i82801gx.h.

| #define HOSTC 0x40 |

Definition at line 141 of file i82801gx.h.

| #define HOT_PLUG_STS (1 << 1) |

Definition at line 296 of file i82801gx.h.

| #define HPTC 0x3404 /* 32bit */ |

Definition at line 227 of file i82801gx.h.

| #define HST_EN (1 << 0) |

Definition at line 146 of file i82801gx.h.

| #define I2C_EN (1 << 2) |

Definition at line 144 of file i82801gx.h.

Definition at line 239 of file i82801gx.h.

Definition at line 246 of file i82801gx.h.

| #define ICH_PCIE_DEV_SLOT 28 |

Definition at line 34 of file i82801gx.h.

| #define IDE_CONFIG 0x54 /* IDE I/O Configuration Register */ |

Definition at line 123 of file i82801gx.h.

| #define IDE_DECODE_ENABLE (1 << 15) |

Definition at line 96 of file i82801gx.h.

| #define IDE_DTE0 (1 << 3) |

Definition at line 109 of file i82801gx.h.

| #define IDE_DTE1 (1 << 7) |

Definition at line 105 of file i82801gx.h.

| #define IDE_IE0 (1 << 1) |

Definition at line 111 of file i82801gx.h.

| #define IDE_IE1 (1 << 5) |

Definition at line 107 of file i82801gx.h.

| #define IDE_ISP_3_CLOCKS (2 << 12) |

Definition at line 100 of file i82801gx.h.

| #define IDE_ISP_4_CLOCKS (1 << 12) |

Definition at line 99 of file i82801gx.h.

| #define IDE_ISP_5_CLOCKS (0 << 12) |

Definition at line 98 of file i82801gx.h.

| #define IDE_PPE0 (1 << 2) |

Definition at line 110 of file i82801gx.h.

| #define IDE_PPE1 (1 << 6) |

Definition at line 106 of file i82801gx.h.

| #define IDE_PSDE0 (1 << 0) |

Definition at line 119 of file i82801gx.h.

| #define IDE_PSDE1 (1 << 1) |

Definition at line 118 of file i82801gx.h.

| #define IDE_RCT_1_CLOCKS (3 << 8) |

Definition at line 104 of file i82801gx.h.

| #define IDE_RCT_2_CLOCKS (2 << 8) |

Definition at line 103 of file i82801gx.h.

| #define IDE_RCT_3_CLOCKS (1 << 8) |

Definition at line 102 of file i82801gx.h.

| #define IDE_RCT_4_CLOCKS (0 << 8) |

Definition at line 101 of file i82801gx.h.

| #define IDE_SDMA_CNT 0x48 /* Synchronous DMA control */ |

Definition at line 115 of file i82801gx.h.

| #define IDE_SDMA_TIM 0x4a |

Definition at line 121 of file i82801gx.h.

| #define IDE_SITRE (1 << 14) |

Definition at line 97 of file i82801gx.h.

| #define IDE_SSDE0 (1 << 2) |

Definition at line 117 of file i82801gx.h.

| #define IDE_SSDE1 (1 << 3) |

Definition at line 116 of file i82801gx.h.

| #define IDE_TIM_PRI 0x40 /* IDE timings, primary */ |

Definition at line 95 of file i82801gx.h.

| #define IDE_TIM_SEC 0x42 /* IDE timings, secondary */ |

Definition at line 113 of file i82801gx.h.

| #define IDE_TIME0 (1 << 0) |

Definition at line 112 of file i82801gx.h.

| #define IDE_TIME1 (1 << 4) |

Definition at line 108 of file i82801gx.h.

| #define ILCL 0x01a0 /* 32bit */ |

Definition at line 188 of file i82801gx.h.

| #define INTEL_USB2_EN (1 << 18) |

Definition at line 303 of file i82801gx.h.

| #define INTR 0x3c |

Definition at line 32 of file i82801gx.h.

| #define INTR_LN 0x3c |

Definition at line 94 of file i82801gx.h.

| #define IOTR0 0x1e80 /* 64bit */ |

Definition at line 207 of file i82801gx.h.

| #define IOTR1 0x1e88 /* 64bit */ |

Definition at line 208 of file i82801gx.h.

| #define IOTR2 0x1e90 /* 64bit */ |

Definition at line 209 of file i82801gx.h.

| #define IOTR3 0x1e98 /* 64bit */ |

Definition at line 210 of file i82801gx.h.

| #define KBC_LPC_EN (1 << 10) /* 0x60/0x64 */ |

Definition at line 80 of file i82801gx.h.

| #define LCAP 0x01a4 /* 32bit */ |

Definition at line 189 of file i82801gx.h.

| #define LCTL 0x01a8 /* 16bit */ |

Definition at line 190 of file i82801gx.h.

| #define LEGACY_USB2_EN (1 << 17) |

Definition at line 304 of file i82801gx.h.

| #define LEGACY_USB_EN (1 << 3) |

Definition at line 312 of file i82801gx.h.

| #define LPC_EN 0x82 /* LPC IF Enables Register */ |

Definition at line 76 of file i82801gx.h.

| #define LPC_IO_DEC 0x80 /* IO Decode Ranges Register */ |

Definition at line 75 of file i82801gx.h.

| #define LPT_LPC_EN (1 << 2) /* LPC_IO_DEC[9:8] */ |

Definition at line 84 of file i82801gx.h.

| #define LSTS 0x01aa /* 16bit */ |

Definition at line 191 of file i82801gx.h.

| #define LV2 0x14 |

Definition at line 278 of file i82801gx.h.

| #define LV3 0x15 |

Definition at line 279 of file i82801gx.h.

| #define LV4 0x16 |

Definition at line 280 of file i82801gx.h.

| #define MAINBOARD_POWER_KEEP 2 |

Definition at line 26 of file i82801gx.h.

| #define MAINBOARD_POWER_OFF 0 |

Definition at line 24 of file i82801gx.h.

| #define MAINBOARD_POWER_ON 1 |

Definition at line 25 of file i82801gx.h.

| #define MC_LPC_EN (1 << 11) /* 0x62/0x66 */ |

Definition at line 79 of file i82801gx.h.

| #define MCSMI_EN (1 << 11) |

Definition at line 307 of file i82801gx.h.

| #define OIC 0x31ff /* 8bit */ |

Definition at line 224 of file i82801gx.h.

| #define PCB0 (1 << 0) |

Definition at line 137 of file i82801gx.h.

| #define PCB1 (1 << 1) |

Definition at line 136 of file i82801gx.h.

| #define PCI_EXP_STS (1 << 9) |

Definition at line 288 of file i82801gx.h.

| #define PCIE_4_PORTS_MAX (1 << 7) |

Definition at line 51 of file i82801gx.h.

| #define PCIEXPWAK_DIS (1 << 14) |

Definition at line 267 of file i82801gx.h.

| #define PCIEXPWAK_STS (1 << 14) |

Definition at line 259 of file i82801gx.h.

| #define PERIODIC_EN (1 << 14) |

Definition at line 305 of file i82801gx.h.

| #define PIRQA_ROUT 0x60 |

Definition at line 66 of file i82801gx.h.

| #define PIRQB_ROUT 0x61 |

Definition at line 67 of file i82801gx.h.

| #define PIRQC_ROUT 0x62 |

Definition at line 68 of file i82801gx.h.

| #define PIRQD_ROUT 0x63 |

Definition at line 69 of file i82801gx.h.

| #define PIRQE_ROUT 0x68 |

Definition at line 70 of file i82801gx.h.

| #define PIRQF_ROUT 0x69 |

Definition at line 71 of file i82801gx.h.

| #define PIRQG_ROUT 0x6A |

Definition at line 72 of file i82801gx.h.

| #define PIRQH_ROUT 0x6B |

Definition at line 73 of file i82801gx.h.

| #define PM1_CNT 0x04 |

Definition at line 272 of file i82801gx.h.

| #define PM1_EN 0x02 |

Definition at line 266 of file i82801gx.h.

| #define PM1_STS 0x00 |

Definition at line 257 of file i82801gx.h.

| #define PM1_TMR 0x08 |

Definition at line 276 of file i82801gx.h.

| #define PM2_CNT 0x20 |

Definition at line 281 of file i82801gx.h.

| #define PMBASE 0x40 |

Definition at line 152 of file i82801gx.h.

| #define PME_B0_EN (1 << 13) |

Definition at line 299 of file i82801gx.h.

| #define PME_B0_STS (1 << 13) |

Definition at line 284 of file i82801gx.h.

| #define PME_EN (1 << 11) |

Definition at line 300 of file i82801gx.h.

| #define PME_STS (1 << 11) |

Definition at line 286 of file i82801gx.h.

| #define PRBTNOR_STS (1 << 11) |

Definition at line 260 of file i82801gx.h.

| #define PROC_CNT 0x10 |

Definition at line 277 of file i82801gx.h.

| #define PSTS 0x06 |

Definition at line 29 of file i82801gx.h.

| #define PVC 0x000c /* 16bit */ |

Definition at line 157 of file i82801gx.h.

| #define PVS 0x000e /* 16bit */ |

Definition at line 158 of file i82801gx.h.

| #define PWRBTN_EN (1 << 8) |

Definition at line 269 of file i82801gx.h.

| #define PWRBTN_STS (1 << 8) |

Definition at line 262 of file i82801gx.h.

| #define RC 0x3400 /* 32bit */ |

Definition at line 226 of file i82801gx.h.

| #define RCTCL 0x0100 /* 32bit */ |

Definition at line 168 of file i82801gx.h.

| #define RI_STS (1 << 8) |

Definition at line 289 of file i82801gx.h.

| #define RP1BA 0x0128 /* 64bit */ |

Definition at line 174 of file i82801gx.h.

| #define RP1D 0x0120 /* 32bit */ |

Definition at line 173 of file i82801gx.h.

| #define RP2BA 0x0138 /* 64bit */ |

Definition at line 176 of file i82801gx.h.

| #define RP2D 0x0130 /* 32bit */ |

Definition at line 175 of file i82801gx.h.

| #define RP3BA 0x0148 /* 64bit */ |

Definition at line 178 of file i82801gx.h.

| #define RP3D 0x0140 /* 32bit */ |

Definition at line 177 of file i82801gx.h.

| #define RP4BA 0x0158 /* 64bit */ |

Definition at line 180 of file i82801gx.h.

| #define RP4D 0x0150 /* 32bit */ |

Definition at line 179 of file i82801gx.h.

| #define RP5BA 0x0178 /* 64bit */ |

Definition at line 184 of file i82801gx.h.

| #define RP5D 0x0170 /* 32bit */ |

Definition at line 183 of file i82801gx.h.

| #define RP6BA 0x0188 /* 64bit */ |

Definition at line 186 of file i82801gx.h.

| #define RP6D 0x0180 /* 32bit */ |

Definition at line 185 of file i82801gx.h.

| #define RPC 0x0224 /* 32bit */ |

Definition at line 193 of file i82801gx.h.

| #define RPFN 0x0238 /* 32bit */ |

Definition at line 194 of file i82801gx.h.

Definition at line 197 of file i82801gx.h.

Definition at line 201 of file i82801gx.h.

Definition at line 199 of file i82801gx.h.

| #define RTC_BATTERY_DEAD (1 << 2) |

Definition at line 55 of file i82801gx.h.

| #define RTC_EN (1 << 10) |

Definition at line 268 of file i82801gx.h.

| #define RTC_POWER_FAILED (1 << 1) |

Definition at line 56 of file i82801gx.h.

| #define RTC_STS (1 << 10) |

Definition at line 261 of file i82801gx.h.

| #define SCB0 (1 << 2) |

Definition at line 135 of file i82801gx.h.

| #define SCB1 (1 << 3) |

Definition at line 134 of file i82801gx.h.

| #define SCI_EN (1 << 0) |

Definition at line 275 of file i82801gx.h.

| #define SECSTS 0x1e |

Definition at line 31 of file i82801gx.h.

| #define SERIRQ_CNTL 0x64 |

Definition at line 38 of file i82801gx.h.

| #define SIG_MODE_PRI_DRIVELOW (2 << 16) |

Definition at line 129 of file i82801gx.h.

| #define SIG_MODE_PRI_NORMAL (0 << 16) |

Definition at line 127 of file i82801gx.h.

| #define SIG_MODE_PRI_TRISTATE (1 << 16) |

Definition at line 128 of file i82801gx.h.

| #define SIG_MODE_SEC_DRIVELOW (2 << 18) |

Definition at line 126 of file i82801gx.h.

| #define SIG_MODE_SEC_NORMAL (0 << 18) |

Definition at line 124 of file i82801gx.h.

| #define SIG_MODE_SEC_TRISTATE (1 << 18) |

Definition at line 125 of file i82801gx.h.

| #define SLEEP_AFTER_POWER_FAIL (1 << 0) |

Definition at line 57 of file i82801gx.h.

| #define SLP_SMI_EN (1 << 4) |

Definition at line 311 of file i82801gx.h.

| #define SMB_BASE 0x20 |

Definition at line 140 of file i82801gx.h.

| #define SMB_SMI_EN (1 << 1) |

Definition at line 145 of file i82801gx.h.

| #define SMB_WAK_STS (1 << 7) |

Definition at line 290 of file i82801gx.h.

| #define SMI_EN 0x30 |

Definition at line 301 of file i82801gx.h.

| #define SMI_STS 0x34 |

Definition at line 316 of file i82801gx.h.

| #define SMLT 0x1b |

Definition at line 30 of file i82801gx.h.

| #define SS_CNT 0x50 |

Definition at line 321 of file i82801gx.h.

| #define SWGPE_STS (1 << 2) |

Definition at line 295 of file i82801gx.h.

| #define SWSMI_TMR_EN (1 << 6) |

Definition at line 309 of file i82801gx.h.

| #define TCO1_CNT 0x68 |

Definition at line 323 of file i82801gx.h.

| #define TCO_EN (1 << 13) |

Definition at line 306 of file i82801gx.h.

| #define TCOSCI_STS (1 << 6) |

Definition at line 291 of file i82801gx.h.

| #define TCTL 0x3000 /* 8bit */ |

Definition at line 212 of file i82801gx.h.

| #define THRM_STS (1 << 0) |

Definition at line 297 of file i82801gx.h.

| #define TMROF_EN (1 << 0) |

Definition at line 271 of file i82801gx.h.

| #define TMROF_STS (1 << 0) |

Definition at line 265 of file i82801gx.h.

| #define TRCR 0x1e10 /* 64bit */ |

Definition at line 204 of file i82801gx.h.

| #define TRSR 0x1e00 /* 8bit */ |

Definition at line 203 of file i82801gx.h.

| #define TWDR 0x1e18 /* 64bit */ |

Definition at line 205 of file i82801gx.h.

| #define ULBA 0x0118 /* 64bit */ |

Definition at line 171 of file i82801gx.h.

| #define ULD 0x0110 /* 32bit */ |

Definition at line 170 of file i82801gx.h.

| #define USB1_STS (1 << 3) |

Definition at line 294 of file i82801gx.h.

| #define USB2_STS (1 << 4) |

Definition at line 293 of file i82801gx.h.

| #define USB3_STS (1 << 12) |

Definition at line 285 of file i82801gx.h.

| #define USB4_STS (1 << 14) |

Definition at line 283 of file i82801gx.h.

| #define V0CAP 0x0010 /* 32bit */ |

Definition at line 160 of file i82801gx.h.

| #define V0CTL 0x0014 /* 32bit */ |

Definition at line 161 of file i82801gx.h.

| #define V0STS 0x001a /* 16bit */ |

Definition at line 162 of file i82801gx.h.

| #define V1CAP 0x001c /* 32bit */ |

Definition at line 164 of file i82801gx.h.

| #define V1CTL 0x0020 /* 32bit */ |

Definition at line 165 of file i82801gx.h.

| #define V1STS 0x0026 /* 16bit */ |

Definition at line 166 of file i82801gx.h.

| #define VCAP1 0x0004 /* 32bit */ |

Definition at line 155 of file i82801gx.h.

| #define VCAP2 0x0008 /* 32bit */ |

Definition at line 156 of file i82801gx.h.

| #define VCH 0x0000 /* 32bit */ |

Definition at line 154 of file i82801gx.h.

| #define WAK_STS (1 << 15) |

Definition at line 258 of file i82801gx.h.

Definition at line 54 of file i82801gx.c.

References BIOS_DEBUG, dev_path(), pci_path::devfn, device::enabled, ich_hide_devfn(), device::path, device_path::pci, PCI_COMMAND, PCI_COMMAND_IO, PCI_COMMAND_MASTER, PCI_COMMAND_MEMORY, PCI_COMMAND_SERR, PCI_DEVFN, pci_or_config16(), pci_read_config16(), pci_write_config16(), printk, and sata_enable().

Referenced by root_port_commit_config().

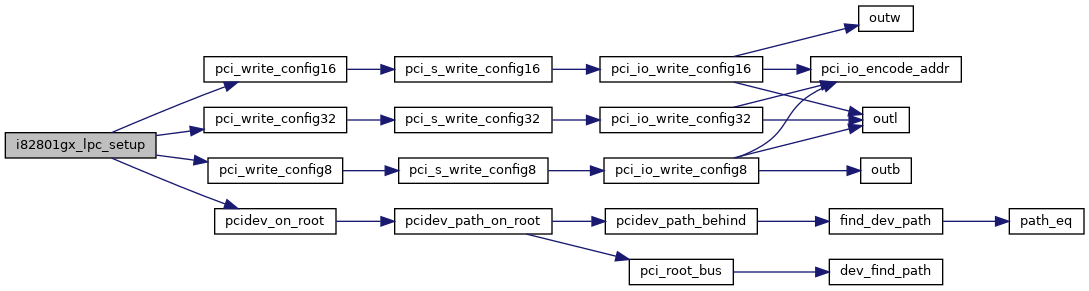

Definition at line 11 of file early_init.c.

References device::chip_info, CNF1_LPC_EN, CNF2_LPC_EN, COMA_LPC_EN, COMB_LPC_EN, config, FDD_LPC_EN, GAMEH_LPC_EN, GAMEL_LPC_EN, GEN1_DEC, GEN2_DEC, GEN3_DEC, GEN4_DEC, KBC_LPC_EN, LPC_EN, LPC_IO_DEC, LPT_LPC_EN, MC_LPC_EN, PCI_DEV, pci_write_config16(), pci_write_config32(), pci_write_config8(), pcidev_on_root(), and SERIRQ_CNTL.

Referenced by bootblock_early_southbridge_init().

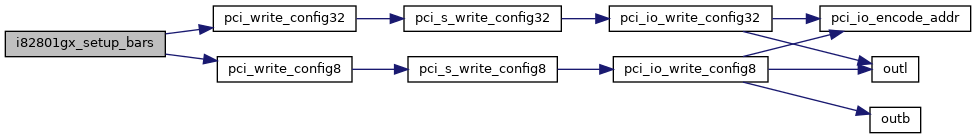

Definition at line 47 of file early_init.c.

References ACPI_CNTL, ACPI_EN, DEFAULT_GPIOBASE, DEFAULT_PMBASE, GPIO_CNTL, GPIO_EN, GPIOBASE, PCI_DEV, pci_write_config32(), pci_write_config8(), PMBASE, and RCBA.

Referenced by bootblock_early_southbridge_init(), and bootblock_mainboard_early_init().

Definition at line 8 of file early_cir.c.

References GCS, PCI_DEV, PCI_DEVICE_ID, pci_read_config16(), pci_read_config8(), PCI_REVISION_ID, RCBA16, RCBA32, RCBA32_AND_OR, and RCBA8.