|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

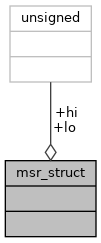

#include <msr.h>

Data Fields | |

| unsigned int | lo |

| unsigned int | hi |

| unsigned int msr_struct::hi |

Definition at line 112 of file msr.h.

Referenced by acpi_fill_root_complex_tom(), add_simple_resources(), amd_topmem2(), apply_microcode_patch(), bsp_setup_msr_save_state(), calculate_l2_latency(), commit_fixed_mtrrs(), configure_c_states(), configure_emttm_tables(), configure_mca(), configure_misc(), configure_p_states(), configure_thermal_core(), cpu_burst_mode(), cpu_config_tdp_levels(), cpu_get_burst_mode_state(), cpu_get_min_ratio(), cpu_set_p_state_to_max_non_turbo_ratio(), cpu_set_p_state_to_min_clock_ratio(), cpu_set_p_state_to_nominal_tdp_ratio(), cpu_set_p_state_to_turbo_ratio(), disable_turbo(), display_mtrrcap(), dnv_configure_mca(), domain_read_resources(), early_cache_setup(), enable_cache_region(), enable_lapic(), enable_pci_mmconf(), enable_pm_timer_emulation(), enable_turbo(), fill_in_msr(), find_cbfs_microcode(), generate_P_state_entries(), get_fsb_tsc(), get_platform_id(), get_pstate_info(), initialize_vr_config(), intel_microcode_load_unlocked(), intel_txt_prepare_txt_env(), ipmi_set_ppin(), is_prmrr_set(), mca_addrv(), mca_cecc(), mca_check_all_banks(), mca_defd(), mca_en(), mca_idv(), mca_miscv(), mca_over(), mca_pcc(), mca_poison(), mca_print_error(), mca_sublink(), mca_uc(), mca_uecc(), mca_valid(), msr_read(), msr_unset_and_set(), northbridge_fill_ssdt_generator(), northbridge_init(), paging_set_pat(), per_cpu_smm_trigger(), psp_notify_smm(), read_microcode_rev(), reg_script_read_msr(), reg_script_write_msr(), relocation_handler(), restore_mtrr(), save_msr(), set_cstate_io_addr(), set_feature_ctrl_vmx_arg(), set_flex_ratio_to_tdp_nominal(), set_l2_ecc(), set_max_freq(), set_max_ratio(), set_max_turbo_freq(), set_power_limits(), set_range_uc(), set_var_mtrr(), signal_l2(), smm_init(), soc_get_uncore_prmmr_base_and_mask(), soc_power_states_generation(), speedstep_get_limits(), stm_setup(), test_l2_address_alias(), timestamp_get(), tsc_freq_mhz(), update_save_state(), update_turbo_state(), write_resume_eip(), wrmsr(), wrmsr_amd(), x2apic_send_ipi(), x2apic_write(), and xeon_configure_mca().

| unsigned int msr_struct::lo |

Definition at line 111 of file msr.h.

Referenced by acpi_fill_root_complex_tom(), activate_sgx(), add_simple_resources(), amd_initmmio(), amd_topmem(), amd_topmem2(), apply_microcode_patch(), backup_mtrr(), bsp_setup_msr_save_state(), bus_freq_khz(), calculate_l2_cache_size(), calculate_l2_latency(), calculate_l2_physical_address_range(), car_stage_entry(), cbmem_top_chipset(), clear_tvalid(), clear_var_mtrr(), commit_fixed_mtrrs(), configure_c_states(), configure_emttm_tables(), configure_mca(), configure_misc(), configure_p_states(), configure_pic_thermal_sensors(), configure_tcc_thermal_target(), configure_thermal_core(), configure_thermal_target(), cpu_bus_freq_khz(), cpu_flex_override(), cpu_get_max_non_turbo_ratio(), cpu_get_max_ratio(), cpu_get_max_turbo_ratio(), cpu_get_power_max(), cpu_get_tdp_nominal_ratio(), cpu_read_topology(), cpu_set_eist(), cpu_set_p_state_to_max_non_turbo_ratio(), cpu_set_p_state_to_min_clock_ratio(), cpu_set_p_state_to_nominal_tdp_ratio(), cpu_set_p_state_to_turbo_ratio(), cpu_soc_is_in_untrusted_mode(), disable_cache_region(), disable_lapic(), display_mtrrcap(), dnv_configure_mca(), domain_read_resources(), early_cache_setup(), early_quickpath_init(), early_thermal_init(), enable_cache_region(), enable_energy_perf_pref(), enable_fixed_mtrr(), enable_getsec_or_reset(), enable_lapic(), enable_pci_mmconf(), enable_pm_timer_emulation(), enable_sgx(), enable_var_mtrr(), fill_fspm_cpu_params(), fill_in_msr(), fill_in_pattrs(), fixed_mtrrs_expose_amd_rwdram(), fixed_mtrrs_hide_amd_rwdram(), flush_l1d_to_l2(), generate_cpu_entries(), generate_P_state_entries(), generate_p_state_entries(), get_cpu_count(), get_cpu_tdp(), get_free_var_mtrr(), get_fsb_tsc(), get_logical_cores_per_package(), get_pstate_core_freq(), get_pstate_core_power(), get_pstate_info(), get_sku_tdp_config(), get_valid_prmrr_size(), get_var_mtrr_count(), getsec_enabled(), init_pm(), initialize_vr_config(), intel_microcode_load_unlocked(), intel_txt_prepare_txt_env(), ipmi_set_ppin(), is_prmrr_approved(), is_prmrr_set(), is_x2apic_mode(), lapic_update32(), lock_sgx(), mainboard_enable(), max_cache_used(), mca_check_all_banks(), mca_clear_status(), mca_err_code(), mca_err_extcode(), mca_get_bank_count(), mca_print_error(), msr_get_fsb(), msr_read(), msr_unset_and_set(), msr_write(), northbridge_fill_ssdt_generator(), northbridge_init(), p6_configure_l2_cache(), paging_set_nxe(), paging_set_pat(), per_core_finalize(), per_cpu_smm_trigger(), platform_fsp_memory_init_params_cb(), prmrr_core_configure(), psp_notify_smm(), read_cpu_topology(), read_l2(), read_microcode_rev(), read_msr_ppin(), reg_script_read_msr(), reg_script_write_msr(), relocation_handler(), restore_mtrr(), save_msr(), set_aesni_lock(), set_cstate_io_addr(), set_feature_ctrl_lock(), set_feature_ctrl_vmx_arg(), set_flex_ratio_to_tdp_nominal(), set_insmm_sts(), set_l2_ecc(), set_max_freq(), set_max_ratio(), set_max_turbo_freq(), set_perf_control_msr(), set_power_limits(), set_range_uc(), set_var_mtrr(), signal_l2(), smbios_cpu_get_current_speed_mhz(), smbios_cpu_get_max_speed_mhz(), smm_init(), smm_relocation_handler(), soc_get_mbox_address(), soc_get_psp_base_address(), soc_get_uncore_prmmr_base_and_mask(), soc_memory_init_params(), soc_power_states_generation(), soc_skip_ucode_update(), speedstep_get_limits(), stm_setup(), test_l2_address_alias(), timestamp_get(), tsc_freq_mhz(), udelay(), update_save_state(), write_prmrr(), write_smrr(), write_smrr_alt(), write_uncore_prmrr(), wrmsr(), wrmsr_amd(), x2apic_read(), x2apic_send_ipi(), x2apic_write(), x86_mtrr_check(), and xeon_configure_mca().