|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

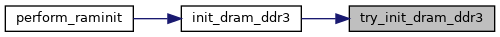

#include <commonlib/clamp.h>#include <console/console.h>#include <console/usb.h>#include <cpu/intel/model_206ax/model_206ax.h>#include <delay.h>#include <device/device.h>#include <device/pci_def.h>#include <device/pci_ops.h>#include <northbridge/intel/sandybridge/chip.h>#include <stdbool.h>#include <stdint.h>#include "raminit_native.h"#include "raminit_common.h"#include "raminit_tables.h"

Go to the source code of this file.

Macros | |

| #define | SNB_MIN_DCLK_133_MULT 3 |

| #define | SNB_MAX_DCLK_133_MULT 8 |

| #define | IVB_MIN_DCLK_133_MULT 3 |

| #define | IVB_MAX_DCLK_133_MULT 10 |

| #define | IVB_MIN_DCLK_100_MULT 7 |

| #define | IVB_MAX_DCLK_100_MULT 12 |

| #define | DEFAULT_TCK TCK_800MHZ |

Functions | |

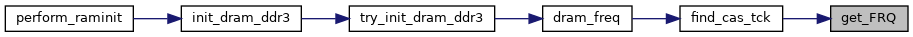

| static u32 | get_FRQ (const ramctr_timing *ctrl) |

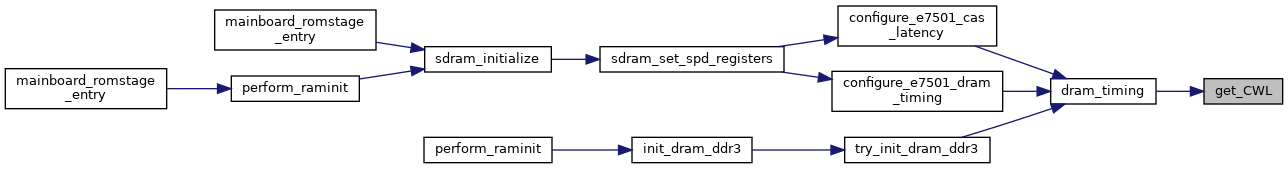

| static u8 | get_CWL (u32 tCK) |

| static u32 | get_REFI (u32 FRQ, u8 base_freq) |

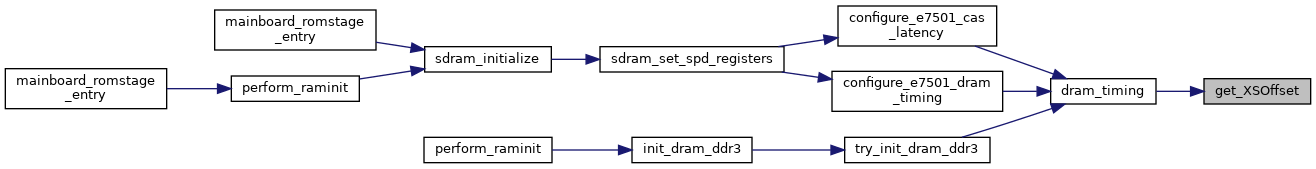

| static u8 | get_XSOffset (u32 FRQ, u8 base_freq) |

| static u8 | get_MOD (u32 FRQ, u8 base_freq) |

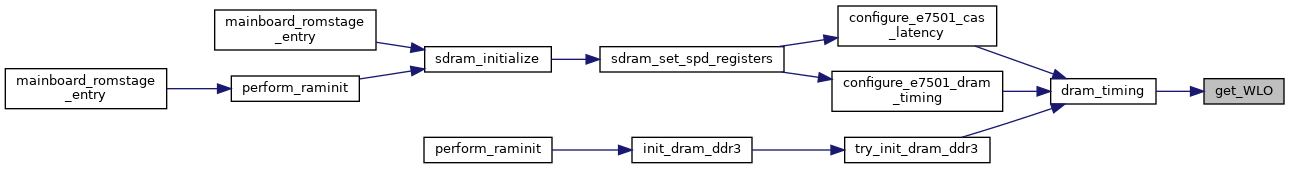

| static u8 | get_WLO (u32 FRQ, u8 base_freq) |

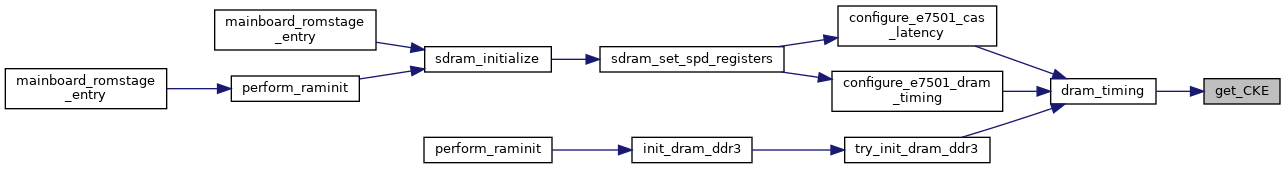

| static u8 | get_CKE (u32 FRQ, u8 base_freq) |

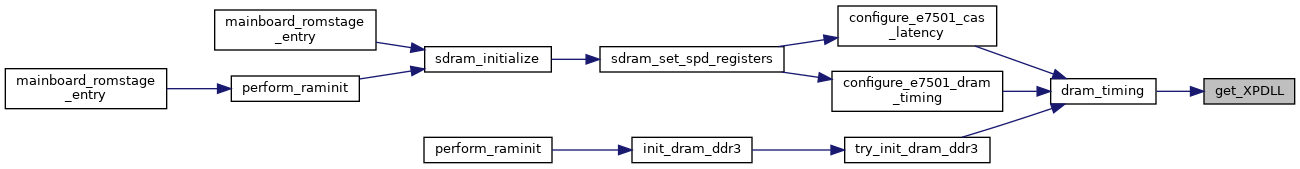

| static u8 | get_XPDLL (u32 FRQ, u8 base_freq) |

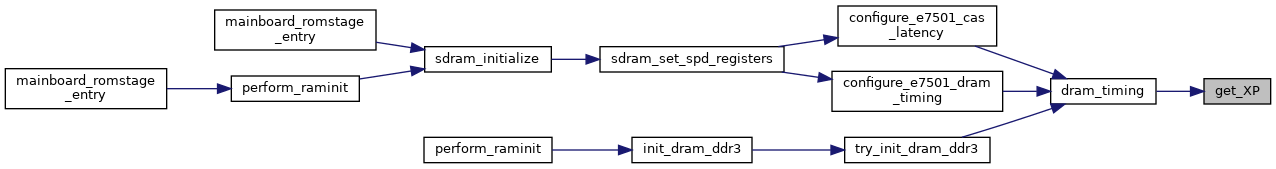

| static u8 | get_XP (u32 FRQ, u8 base_freq) |

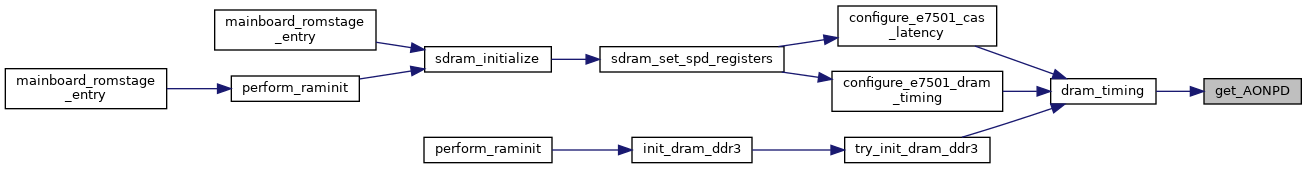

| static u8 | get_AONPD (u32 FRQ, u8 base_freq) |

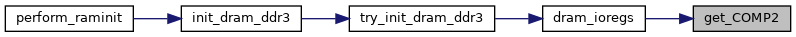

| static u32 | get_COMP2 (const ramctr_timing *ctrl) |

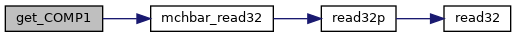

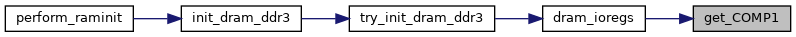

| static u32 | get_COMP1 (ramctr_timing *ctrl, const int channel) |

| static void | normalize_tclk (ramctr_timing *ctrl, bool ref_100mhz_support) |

| static unsigned int | get_mem_min_tck (void) |

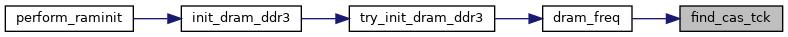

| static void | find_cas_tck (ramctr_timing *ctrl) |

| static void | dram_timing (ramctr_timing *ctrl) |

| static void | dram_freq (ramctr_timing *ctrl) |

| static void | dram_ioregs (ramctr_timing *ctrl) |

| int | try_init_dram_ddr3 (ramctr_timing *ctrl, int fast_boot, int s3resume, int me_uma_size) |

| #define DEFAULT_TCK TCK_800MHZ |

Definition at line 264 of file raminit_native.c.

| #define IVB_MAX_DCLK_100_MULT 12 |

Definition at line 24 of file raminit_native.c.

| #define IVB_MAX_DCLK_133_MULT 10 |

Definition at line 22 of file raminit_native.c.

| #define IVB_MIN_DCLK_100_MULT 7 |

Definition at line 23 of file raminit_native.c.

| #define IVB_MIN_DCLK_133_MULT 3 |

Definition at line 21 of file raminit_native.c.

| #define SNB_MAX_DCLK_133_MULT 8 |

Definition at line 20 of file raminit_native.c.

| #define SNB_MIN_DCLK_133_MULT 3 |

Definition at line 19 of file raminit_native.c.

|

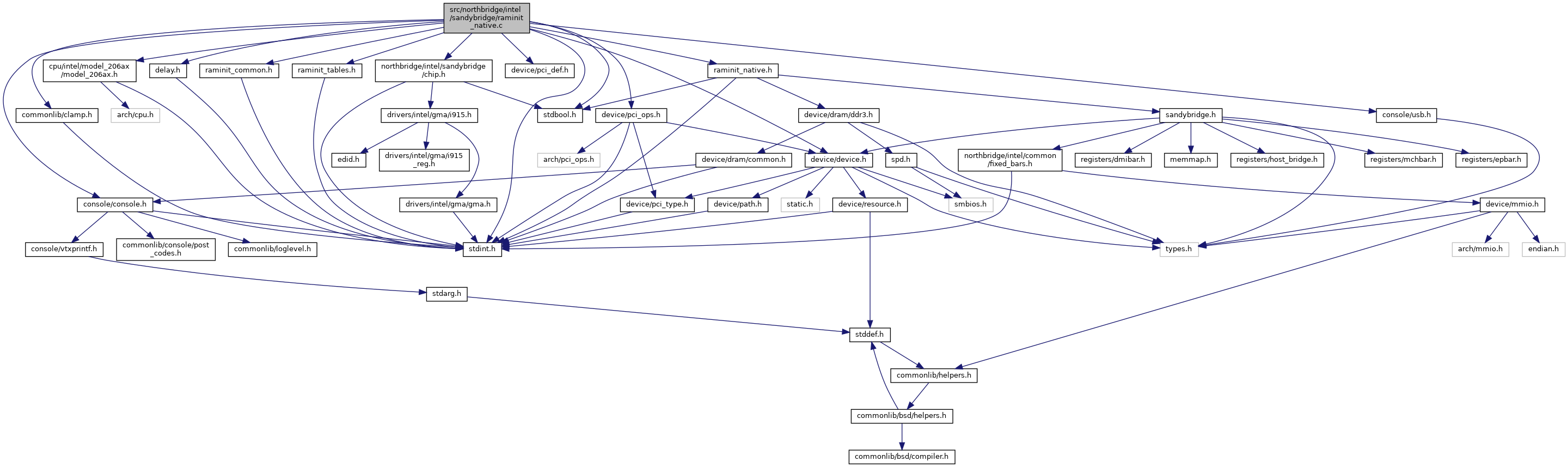

static |

Definition at line 537 of file raminit_native.c.

References ramctr_timing_st::base_freq, BIOS_DEBUG, BIOS_ERR, find_cas_tck(), ramctr_timing_st::FRQ, MC_BIOS_DATA, MC_BIOS_REQ, mchbar_read32(), mchbar_write32(), printk, ramctr_timing_st::tCK, TCK_400MHZ, and udelay().

Referenced by try_init_dram_ddr3().

|

static |

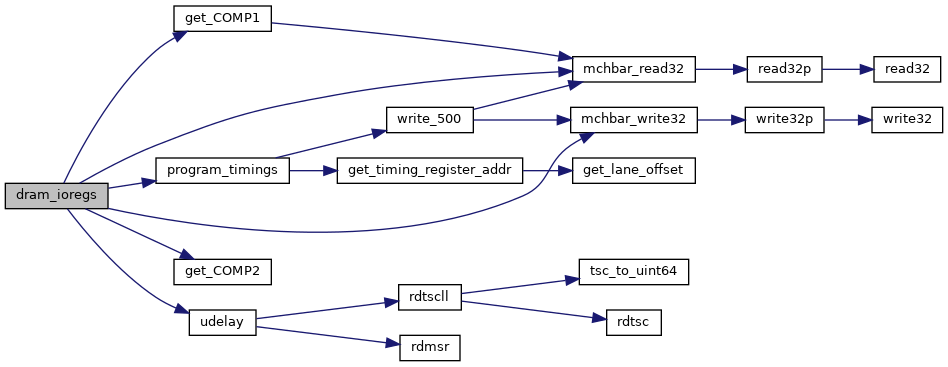

Definition at line 591 of file raminit_native.c.

References CRCOMPOFST1_ch, CRCOMPOFST2, FOR_ALL_CHANNELS, FOR_ALL_POPULATED_CHANNELS, GDCRCLKRANKSUSED_ch, GDCRCTLRANKSUSED_ch, get_COMP1(), get_COMP2(), M_COMP, mchbar_read32(), mchbar_setbits32, mchbar_write32(), printram, program_timings(), ramctr_timing_st::rankmap, RCOMP_TIMER, and udelay().

Referenced by try_init_dram_ddr3().

|

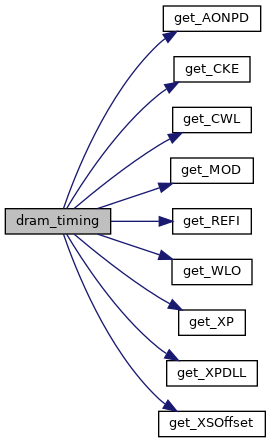

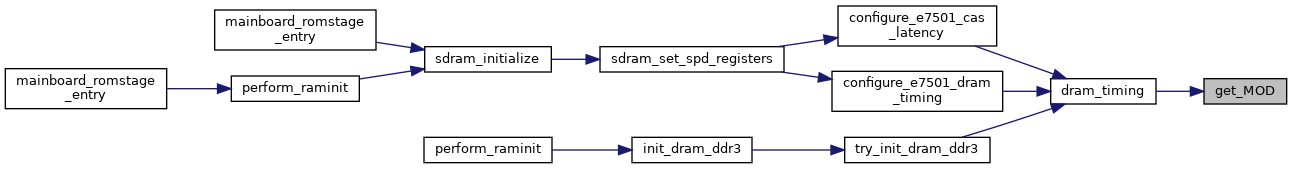

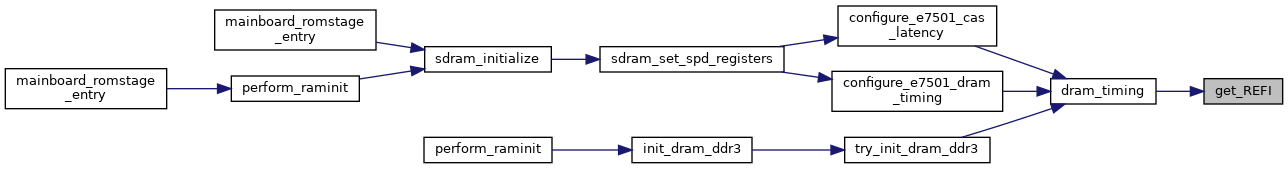

static |

Definition at line 385 of file raminit_native.c.

References ramctr_timing_st::base_freq, BIOS_DEBUG, ramctr_timing_st::CWL, DIV_ROUND_UP, ramctr_timing_st::edge_offset, ramctr_timing_st::FRQ, get_AONPD(), get_CKE(), get_CWL(), get_MOD(), get_REFI(), get_WLO(), get_XP(), get_XPDLL(), get_XSOffset(), ramctr_timing_st::mdll_wake_delay, ramctr_timing_st::pi_code_offset, ramctr_timing_st::pi_coding_threshold, printk, ramctr_timing_st::tAONPD, ramctr_timing_st::tCK, TCK_1000MHZ, TCK_1066MHZ, TCK_1100MHZ, TCK_1200MHZ, TCK_533MHZ, TCK_666MHZ, TCK_700MHZ, TCK_800MHZ, TCK_900MHZ, TCK_933MHZ, ramctr_timing_st::tCKE, ramctr_timing_st::tCWL, ramctr_timing_st::tFAW, ramctr_timing_st::tMOD, ramctr_timing_st::tRAS, ramctr_timing_st::tRCD, ramctr_timing_st::tREFI, ramctr_timing_st::tRFC, ramctr_timing_st::tRP, ramctr_timing_st::tRRD, ramctr_timing_st::tRTP, ramctr_timing_st::tWLO, ramctr_timing_st::tWR, ramctr_timing_st::tWTR, ramctr_timing_st::tx_dq_offset, ramctr_timing_st::tXP, ramctr_timing_st::tXPDLL, and ramctr_timing_st::tXSOffset.

Referenced by configure_e7501_cas_latency(), configure_e7501_dram_timing(), and try_init_dram_ddr3().

|

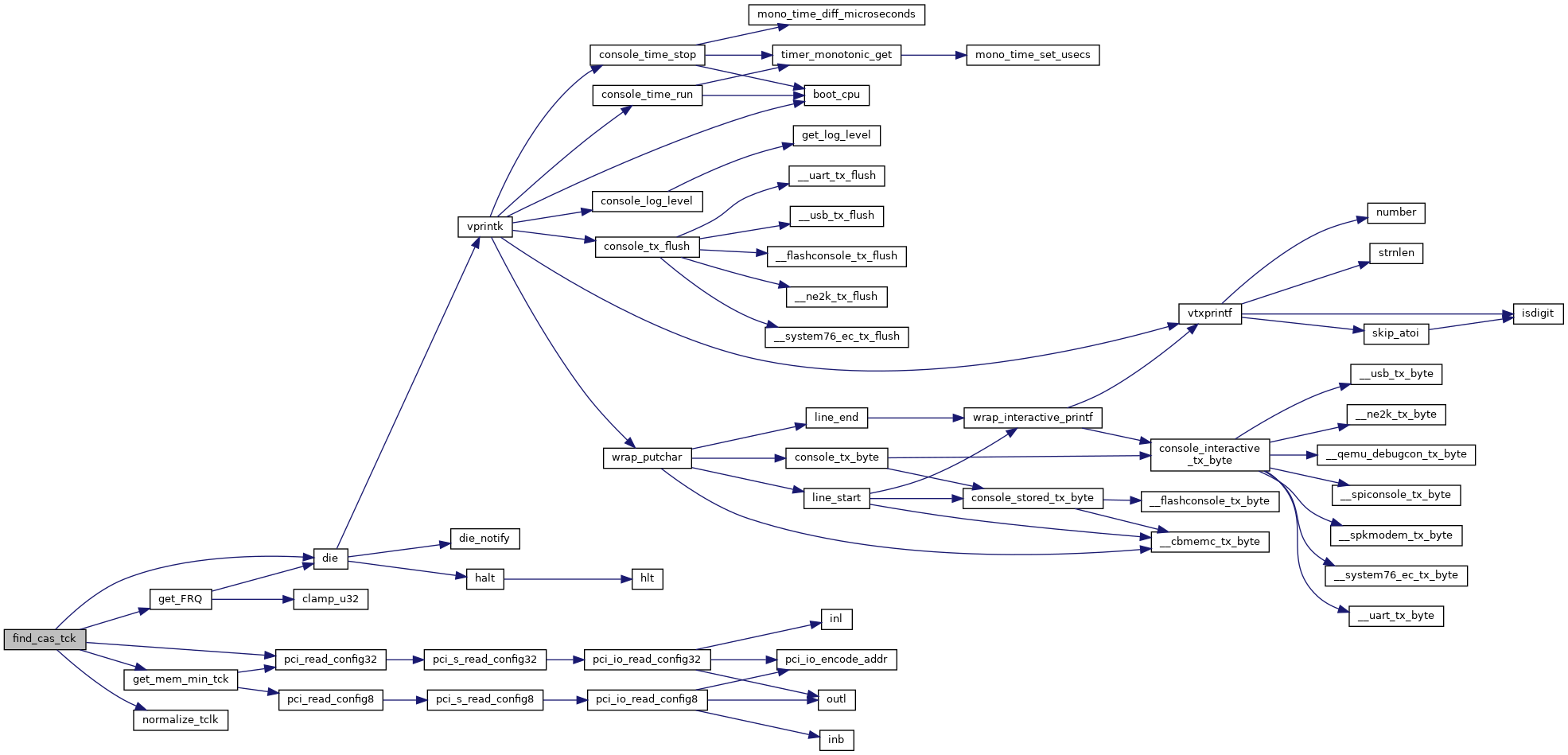

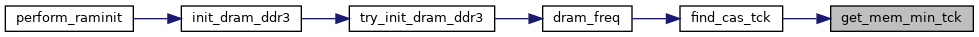

static |

Definition at line 336 of file raminit_native.c.

References BIOS_DEBUG, CAPID0_B, ramctr_timing_st::CAS, ramctr_timing_st::cas_supported, die(), DIV_ROUND_UP, ramctr_timing_st::FRQ, get_FRQ(), get_mem_min_tck(), HOST_BRIDGE, MAX_CAS, MIN_CAS, normalize_tclk(), NS2MHZ_DIV256, pci_read_config32(), printk, ramctr_timing_st::tAA, ramctr_timing_st::tCK, and val.

Referenced by dram_freq().

Definition at line 152 of file raminit_native.c.

References frq_aonpd_map.

Referenced by dram_timing().

Definition at line 122 of file raminit_native.c.

References frq_cke_map.

Referenced by dram_timing().

|

static |

Definition at line 181 of file raminit_native.c.

References comp_ofst_1_reg::clk_drv_up, comp_ofst_1_reg::clk_odt_up, ramctr_timing_st::cpu, CRCOMPOFST1_ch, comp_ofst_1_reg::ctl_drv_up, comp_ofst_1_reg::dq_drv_up, comp_ofst_1_reg::dq_odt_down, IS_IVY_CPU, IS_SANDY_CPU, IS_SANDY_CPU_D2, mchbar_read32(), and comp_ofst_1_reg::raw.

Referenced by dram_ioregs().

|

static |

Definition at line 162 of file raminit_native.c.

References ramctr_timing_st::cpu, IS_IVY_CPU, ramctr_timing_st::tCK, TCK_1066MHZ, TCK_533MHZ, TCK_666MHZ, TCK_800MHZ, and TCK_933MHZ.

Referenced by dram_ioregs().

Definition at line 47 of file raminit_native.c.

References TCK_1000MHZ, TCK_1066MHZ, TCK_1100MHZ, TCK_1200MHZ, TCK_1333MHZ, TCK_533MHZ, TCK_666MHZ, TCK_700MHZ, TCK_800MHZ, TCK_900MHZ, and TCK_933MHZ.

Referenced by dram_timing().

|

static |

Definition at line 27 of file raminit_native.c.

References ramctr_timing_st::base_freq, clamp_u32(), ramctr_timing_st::cpu, die(), IS_IVY_CPU, IS_SANDY_CPU, IVB_MAX_DCLK_100_MULT, IVB_MAX_DCLK_133_MULT, IVB_MIN_DCLK_100_MULT, IVB_MIN_DCLK_133_MULT, SNB_MAX_DCLK_133_MULT, SNB_MIN_DCLK_133_MULT, and ramctr_timing_st::tCK.

Referenced by find_cas_tck().

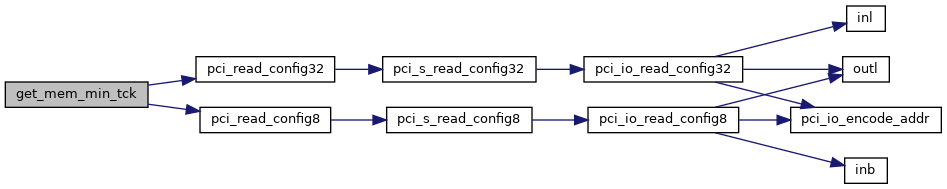

Definition at line 266 of file raminit_native.c.

References BASE_REV_MASK, BASE_REV_SNB, CAPID0_A, CAPID0_B, CONFIG, config_of_soc, DEFAULT_TCK, HOST_BRIDGE, northbridge_intel_sandybridge_config::max_mem_clock_mhz, NULL, PCI_DEVICE_ID, pci_read_config32(), pci_read_config8(), TCK_1066MHZ, TCK_1200MHZ, TCK_1333MHZ, TCK_400MHZ, TCK_533MHZ, TCK_666MHZ, TCK_800MHZ, and TCK_933MHZ.

Referenced by find_cas_tck().

Definition at line 102 of file raminit_native.c.

References frq_mod_map.

Referenced by dram_timing().

Definition at line 82 of file raminit_native.c.

References frq_refi_map.

Referenced by dram_timing().

Definition at line 112 of file raminit_native.c.

References frq_wlo_map.

Referenced by dram_timing().

Definition at line 142 of file raminit_native.c.

References frq_xp_map.

Referenced by dram_timing().

Definition at line 132 of file raminit_native.c.

References frq_xpdll_map.

Referenced by dram_timing().

Definition at line 92 of file raminit_native.c.

References frq_xs_map.

Referenced by dram_timing().

|

static |

Definition at line 217 of file raminit_native.c.

References ramctr_timing_st::base_freq, ramctr_timing_st::tCK, TCK_1000MHZ, TCK_1066MHZ, TCK_1100MHZ, TCK_1200MHZ, TCK_400MHZ, TCK_533MHZ, TCK_666MHZ, TCK_700MHZ, TCK_800MHZ, TCK_900MHZ, and TCK_933MHZ.

Referenced by find_cas_tck().

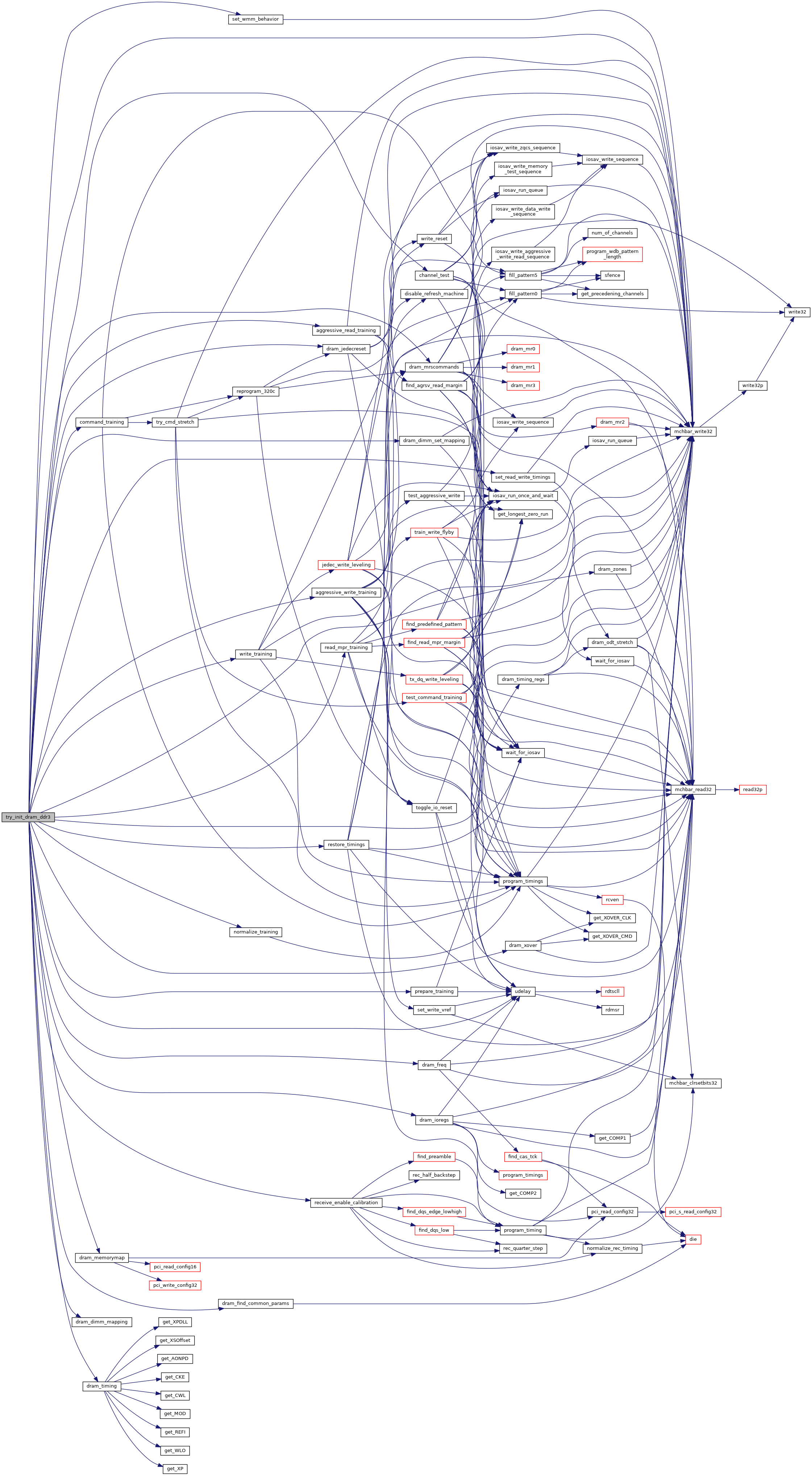

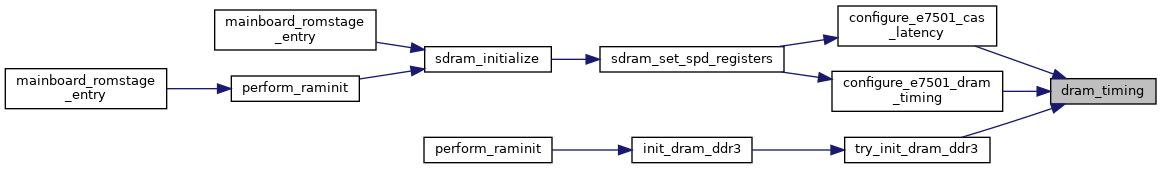

| int try_init_dram_ddr3 | ( | ramctr_timing * | ctrl, |

| int | fast_boot, | ||

| int | s3resume, | ||

| int | me_uma_size | ||

| ) |

Definition at line 633 of file raminit_native.c.

References aggressive_read_training(), aggressive_write_training(), BIOS_DEBUG, channel_test(), command_training(), ramctr_timing_st::cpu, dram_dimm_mapping(), dram_dimm_set_mapping(), dram_find_common_params(), dram_freq(), dram_ioregs(), dram_jedecreset(), dram_memorymap(), dram_mrscommands(), dram_timing(), dram_timing_regs(), dram_xover(), dram_zones(), IS_SANDY_CPU, MC_INIT_STATE_G, mchbar_clrbits32, mchbar_write32(), MRC_REVISION, normalize_training(), PM_THML_STAT, prepare_training(), printk, printram, read_mpr_training(), receive_enable_calibration(), restore_timings(), SCHED_CBIT, set_read_write_timings(), set_wmm_behavior(), udelay(), and write_training().

Referenced by init_dram_ddr3().