|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

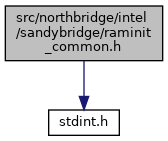

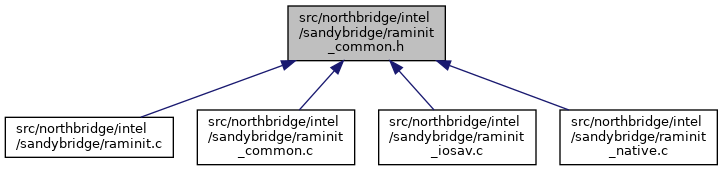

#include <stdint.h>

Go to the source code of this file.

Data Structures | |

| struct | iosav_ssq |

| union | gdcr_rx_reg |

| union | gdcr_tx_reg |

| union | gdcr_cmd_pi_coding_reg |

| union | gdcr_training_mod_reg |

| union | comp_ofst_1_reg |

| union | tc_dbp_reg |

| union | tc_rap_reg |

| union | tc_rwp_reg |

| union | tc_othp_reg |

| union | tc_dtp_reg |

| union | tc_rfp_reg |

| union | tc_rftp_reg |

| union | tc_srftp_reg |

| struct | odtmap_st |

| struct | dimm_info_st |

| struct | ram_rank_timings |

| struct | ram_rank_timings::ram_lane_timings |

| struct | ramctr_timing_st |

Macros | |

| #define | BASEFREQ 133 |

| #define | tDLLK 512 |

| #define | NUM_CHANNELS 2 |

| #define | NUM_SLOTRANKS 4 |

| #define | NUM_SLOTS 2 |

| #define | NUM_LANES 9 |

| #define | IOSAV_MRS (0xf000) |

| #define | IOSAV_PRE (0xf002) |

| #define | IOSAV_ZQCS (0xf003) |

| #define | IOSAV_ACT (0xf006) |

| #define | IOSAV_RD (0xf105) |

| #define | IOSAV_NOP_ALT (0xf107) |

| #define | IOSAV_WR (0xf201) |

| #define | IOSAV_NOP (0xf207) |

| #define | SSQ_NA 0 /* Non-data */ |

| #define | SSQ_RD 1 /* Read */ |

| #define | SSQ_WR 2 /* Write */ |

| #define | SSQ_RW 3 /* Read and write */ |

| #define | NUM_PATTERNS 4 |

| #define | MRC_CACHE_VERSION 5 |

| #define | SOUTHBRIDGE PCI_DEV(0, 0x1f, 0) |

| #define | FOR_ALL_LANES for (lane = 0; lane < ctrl->lanes; lane++) |

| #define | FOR_ALL_CHANNELS for (channel = 0; channel < NUM_CHANNELS; channel++) |

| #define | FOR_ALL_POPULATED_RANKS for (slotrank = 0; slotrank < NUM_SLOTRANKS; slotrank++) if (ctrl->rankmap[channel] & (1 << slotrank)) |

| #define | FOR_ALL_POPULATED_CHANNELS for (channel = 0; channel < NUM_CHANNELS; channel++) if (ctrl->rankmap[channel]) |

| #define | MAX_EDGE_TIMING 71 |

| #define | MAX_TX_DQ 127 |

| #define | MAX_TX_DQS 511 |

| #define | MAX_RCVEN 127 |

| #define | MAX_CAS 18 |

| #define | MIN_CAS 4 |

| #define | QCLK_PI 64 |

| #define | MAKE_ERR ((channel << 16) | (slotrank << 8) | 1) |

| #define | GET_ERR_CHANNEL(x) (x >> 16) |

Typedefs | |

| typedef struct ramctr_timing_st | ramctr_timing |

| typedef struct odtmap_st | odtmap |

| typedef struct dimm_info_st | dimm_info |

Enumerations | |

| enum | power_down_mode { PDM_NONE = 0 , PDM_APD = 1 , PDM_PPD = 2 , PDM_APD_PPD = 3 , PDM_DLL_OFF = 6 , PDM_APD_DLL_OFF = 7 } |

| #define BASEFREQ 133 |

Definition at line 8 of file raminit_common.h.

| #define FOR_ALL_CHANNELS for (channel = 0; channel < NUM_CHANNELS; channel++) |

Definition at line 425 of file raminit_common.h.

| #define FOR_ALL_LANES for (lane = 0; lane < ctrl->lanes; lane++) |

Definition at line 424 of file raminit_common.h.

| #define FOR_ALL_POPULATED_CHANNELS for (channel = 0; channel < NUM_CHANNELS; channel++) if (ctrl->rankmap[channel]) |

Definition at line 427 of file raminit_common.h.

| #define FOR_ALL_POPULATED_RANKS for (slotrank = 0; slotrank < NUM_SLOTRANKS; slotrank++) if (ctrl->rankmap[channel] & (1 << slotrank)) |

Definition at line 426 of file raminit_common.h.

Definition at line 443 of file raminit_common.h.

| #define IOSAV_ACT (0xf006) |

Definition at line 20 of file raminit_common.h.

| #define IOSAV_MRS (0xf000) |

Definition at line 17 of file raminit_common.h.

| #define IOSAV_NOP (0xf207) |

Definition at line 24 of file raminit_common.h.

| #define IOSAV_NOP_ALT (0xf107) |

Definition at line 22 of file raminit_common.h.

| #define IOSAV_PRE (0xf002) |

Definition at line 18 of file raminit_common.h.

| #define IOSAV_RD (0xf105) |

Definition at line 21 of file raminit_common.h.

| #define IOSAV_WR (0xf201) |

Definition at line 23 of file raminit_common.h.

| #define IOSAV_ZQCS (0xf003) |

Definition at line 19 of file raminit_common.h.

| #define MAKE_ERR ((channel << 16) | (slotrank << 8) | 1) |

Definition at line 442 of file raminit_common.h.

| #define MAX_CAS 18 |

Definition at line 432 of file raminit_common.h.

| #define MAX_EDGE_TIMING 71 |

Definition at line 428 of file raminit_common.h.

| #define MAX_RCVEN 127 |

Definition at line 431 of file raminit_common.h.

| #define MAX_TX_DQ 127 |

Definition at line 429 of file raminit_common.h.

| #define MAX_TX_DQS 511 |

Definition at line 430 of file raminit_common.h.

| #define MIN_CAS 4 |

Definition at line 433 of file raminit_common.h.

| #define MRC_CACHE_VERSION 5 |

Definition at line 307 of file raminit_common.h.

| #define NUM_CHANNELS 2 |

Definition at line 11 of file raminit_common.h.

| #define NUM_LANES 9 |

Definition at line 14 of file raminit_common.h.

| #define NUM_PATTERNS 4 |

Definition at line 302 of file raminit_common.h.

| #define NUM_SLOTRANKS 4 |

Definition at line 12 of file raminit_common.h.

| #define NUM_SLOTS 2 |

Definition at line 13 of file raminit_common.h.

| #define QCLK_PI 64 |

Definition at line 440 of file raminit_common.h.

| #define SOUTHBRIDGE PCI_DEV(0, 0x1f, 0) |

Definition at line 422 of file raminit_common.h.

| #define SSQ_NA 0 /* Non-data */ |

Definition at line 27 of file raminit_common.h.

| #define SSQ_RD 1 /* Read */ |

Definition at line 28 of file raminit_common.h.

| #define SSQ_RW 3 /* Read and write */ |

Definition at line 30 of file raminit_common.h.

| #define SSQ_WR 2 /* Write */ |

Definition at line 29 of file raminit_common.h.

| #define tDLLK 512 |

Definition at line 9 of file raminit_common.h.

| typedef struct dimm_info_st dimm_info |

| typedef struct ramctr_timing_st ramctr_timing |

Definition at line 1 of file raminit_common.h.

| enum power_down_mode |

| Enumerator | |

|---|---|

| PDM_NONE | |

| PDM_APD | |

| PDM_PPD | |

| PDM_APD_PPD | |

| PDM_DLL_OFF | |

| PDM_APD_DLL_OFF | |

Definition at line 309 of file raminit_common.h.

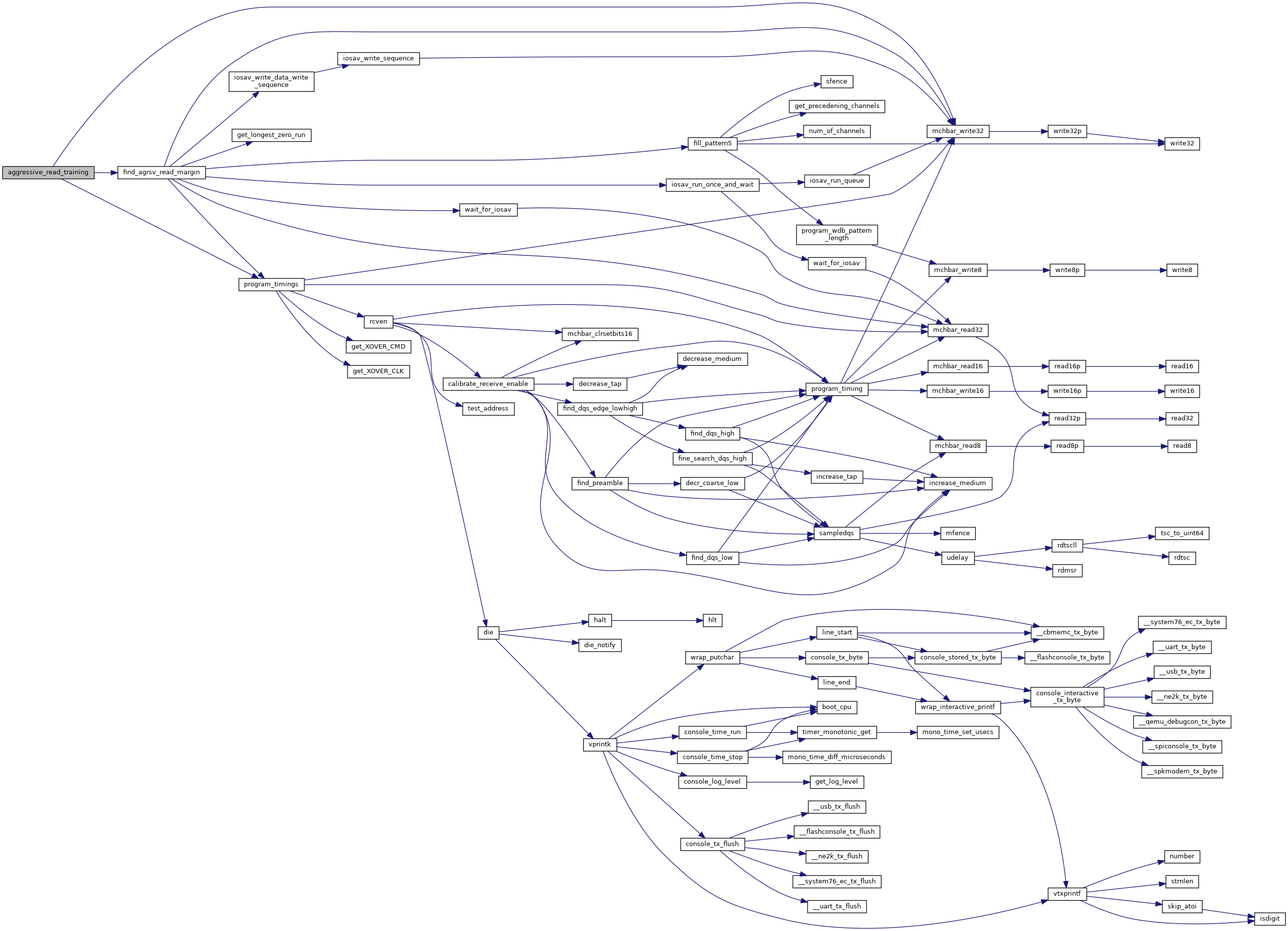

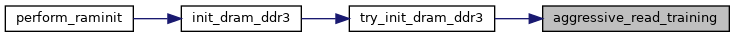

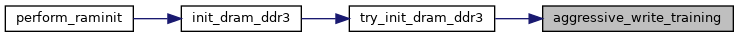

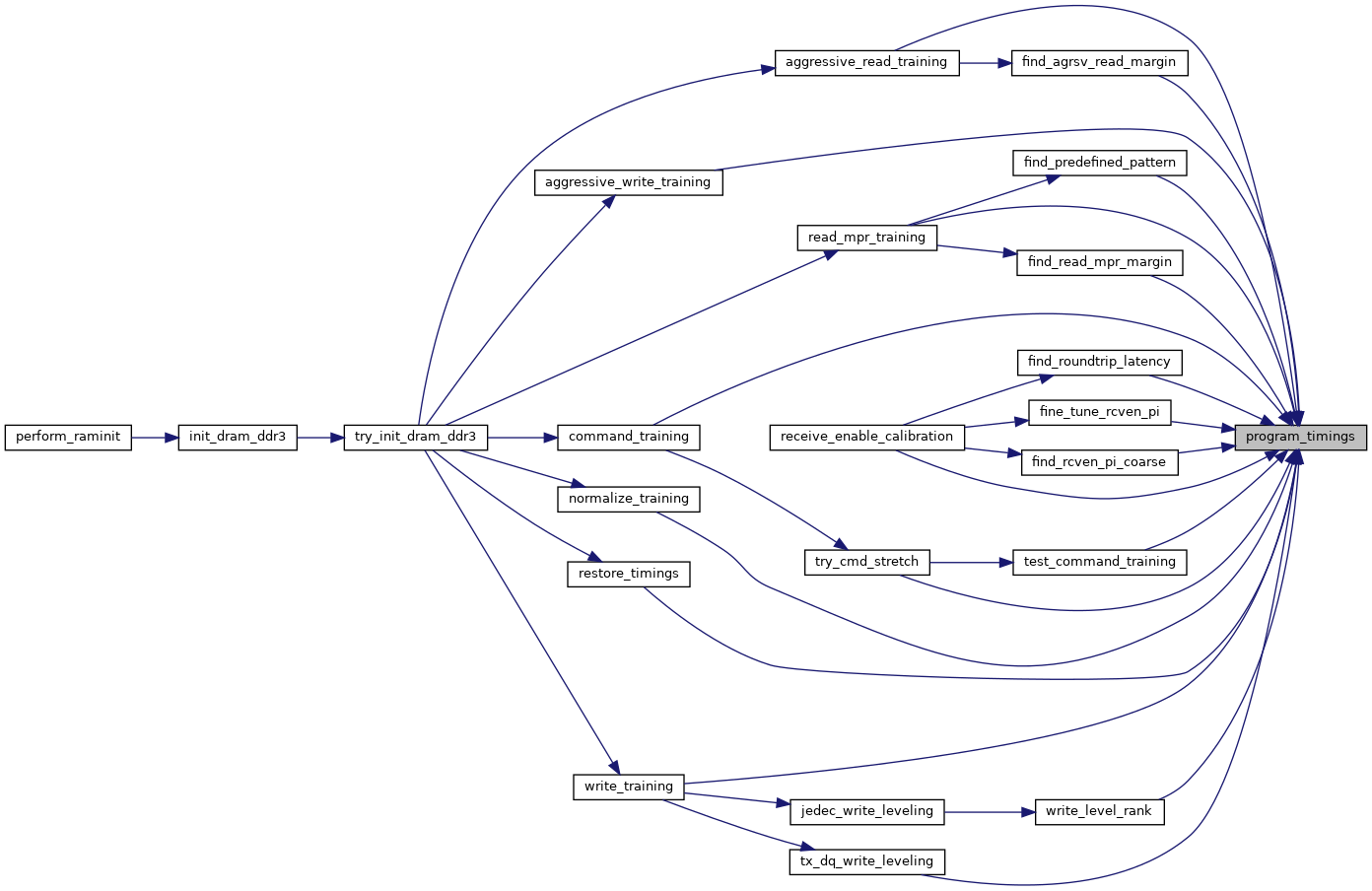

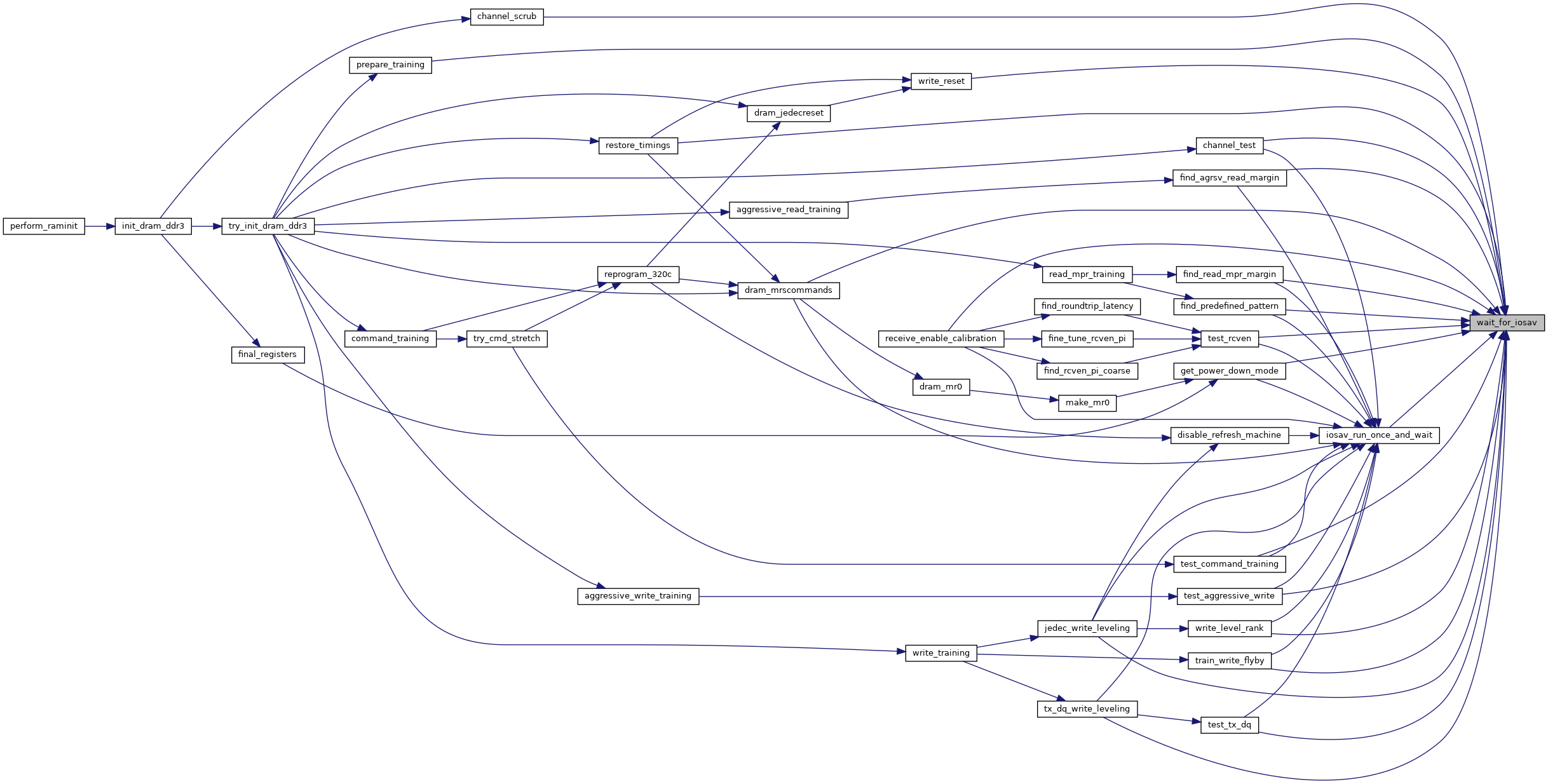

| int aggressive_read_training | ( | ramctr_timing * | ctrl | ) |

Definition at line 2352 of file raminit_common.c.

References find_agrsv_read_margin(), FOR_ALL_CHANNELS, FOR_ALL_LANES, FOR_ALL_POPULATED_CHANNELS, FOR_ALL_POPULATED_RANKS, IOSAV_DC_MASK, ram_rank_timings::lanes, mchbar_write32(), NUM_CHANNELS, NUM_LANES, NUM_SLOTRANKS, printram, program_timings(), ram_rank_timings::ram_lane_timings::rx_dqs_n, ram_rank_timings::ram_lane_timings::rx_dqs_p, and ramctr_timing_st::timings.

Referenced by try_init_dram_ddr3().

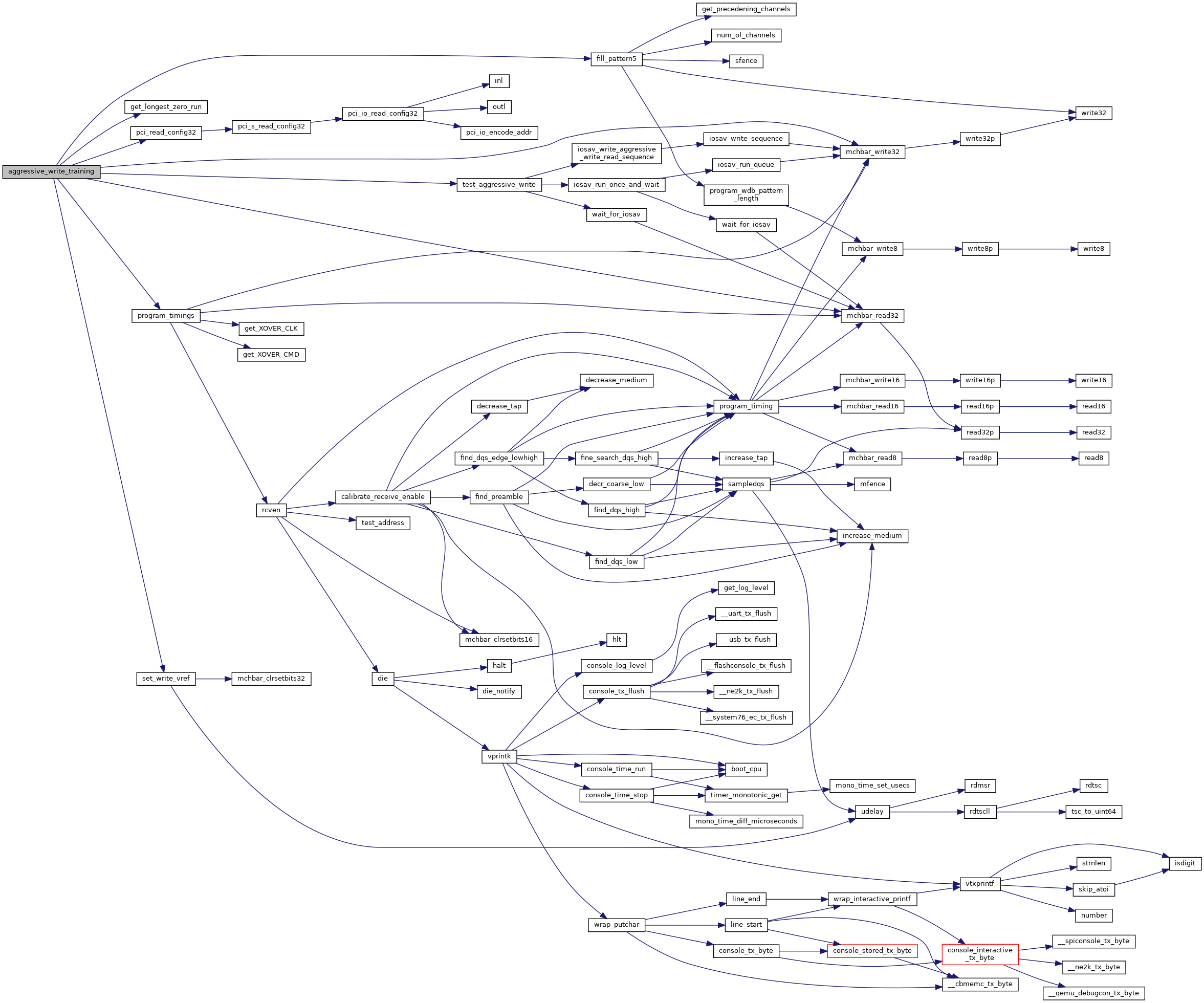

| int aggressive_write_training | ( | ramctr_timing * | ctrl | ) |

Definition at line 2413 of file raminit_common.c.

References run::all, ARRAY_SIZE, BIOS_EMERG, CAPID0_A, CAPID_WRTVREF, ramctr_timing_st::cpu, run::end, fill_pattern5(), FOR_ALL_CHANNELS, FOR_ALL_LANES, FOR_ALL_POPULATED_CHANNELS, FOR_ALL_POPULATED_RANKS, get_longest_zero_run(), HOST_BRIDGE, IOSAV_BYTE_SERROR_C_ch, IS_IVY_CPU, IS_IVY_CPU_D, IS_IVY_CPU_E, ram_rank_timings::lanes, MAKE_ERR, MAX, MAX_TX_DQ, mchbar_read32(), mchbar_write32(), MCMNTS_SPARE, run::middle, MIN, NUM_CHANNELS, NUM_LANES, NUM_PATTERNS, NUM_SLOTRANKS, pci_read_config32(), printk, printram, program_timings(), set_write_vref(), run::start, test_aggressive_write(), ramctr_timing_st::timings, ram_rank_timings::ram_lane_timings::tx_dq, and ramctr_timing_st::tx_dq_offset.

Referenced by try_init_dram_ddr3().

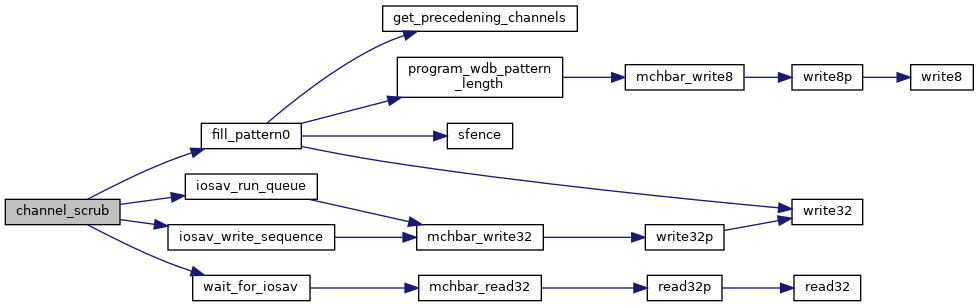

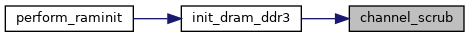

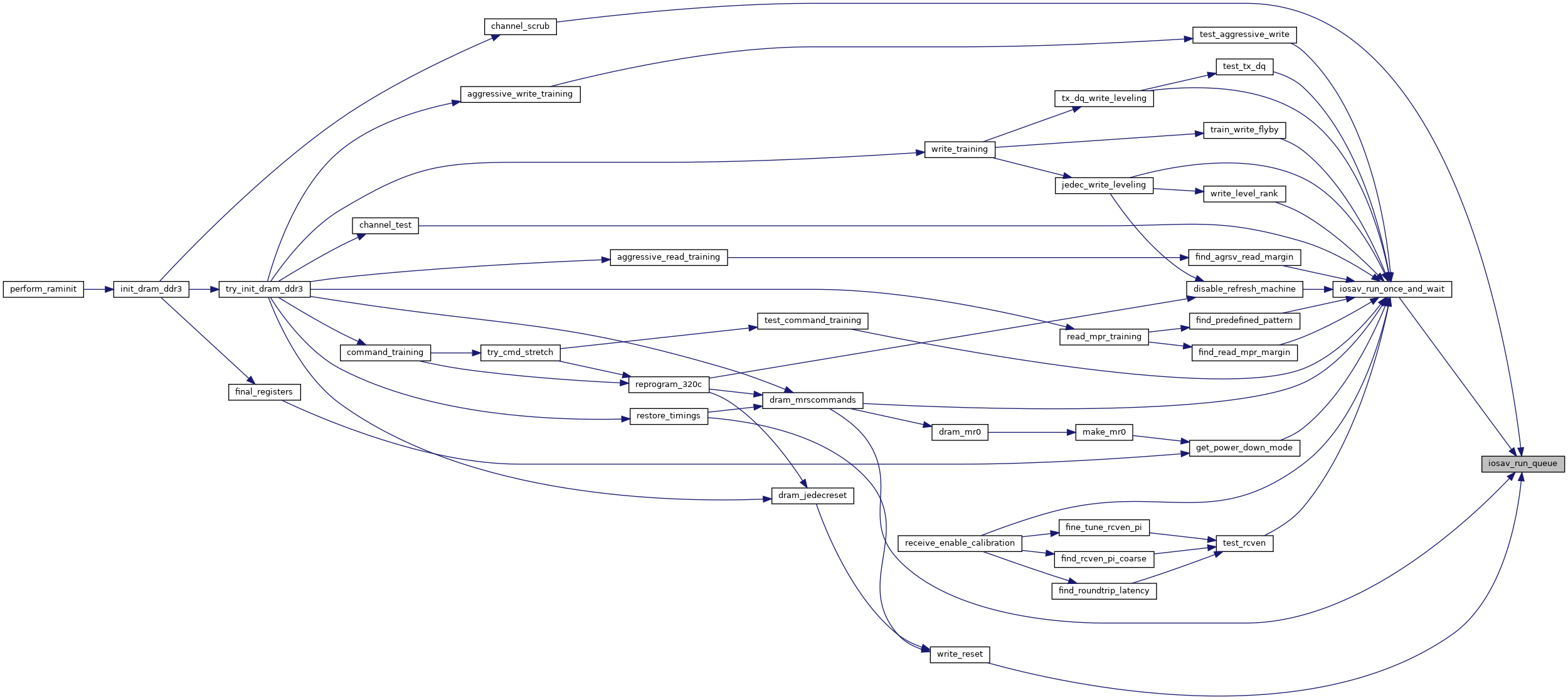

| void channel_scrub | ( | ramctr_timing * | ctrl | ) |

Definition at line 2595 of file raminit_common.c.

References ARRAY_SIZE, iosav_ssq::bank, iosav_ssq::command, ramctr_timing_st::CWL, fill_pattern0(), FOR_ALL_POPULATED_CHANNELS, FOR_ALL_POPULATED_RANKS, ramctr_timing_st::info, IOSAV_ACT, IOSAV_PRE, iosav_run_queue(), IOSAV_WR, iosav_write_sequence(), MAX, iosav_ssq::sp_cmd_ctrl, SSQ_NA, SSQ_WR, ramctr_timing_st::tFAW, ramctr_timing_st::tRCD, ramctr_timing_st::tRP, ramctr_timing_st::tRRD, ramctr_timing_st::tWTR, and wait_for_iosav().

Referenced by init_dram_ddr3().

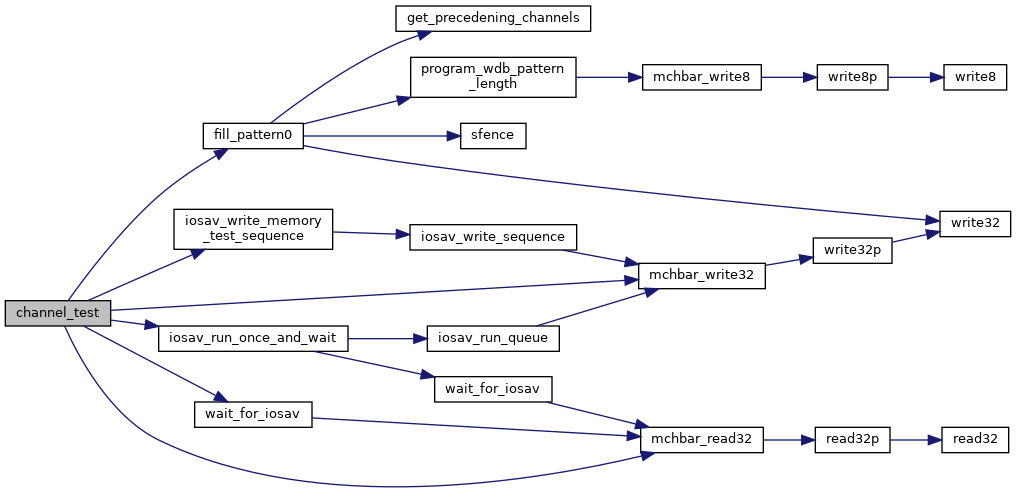

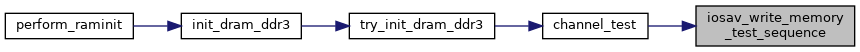

| int channel_test | ( | ramctr_timing * | ctrl | ) |

Definition at line 2558 of file raminit_common.c.

References BIOS_EMERG, fill_pattern0(), FOR_ALL_CHANNELS, FOR_ALL_LANES, FOR_ALL_POPULATED_CHANNELS, IOSAV_By_BW_SERROR_C, IOSAV_By_ERROR_COUNT, IOSAV_By_ERROR_COUNT_ch, iosav_run_once_and_wait(), iosav_write_memory_test_sequence(), MAKE_ERR, MC_INIT_STATE_ch, mchbar_read32(), mchbar_write32(), printk, ramctr_timing_st::rankmap, and wait_for_iosav().

Referenced by try_init_dram_ddr3().

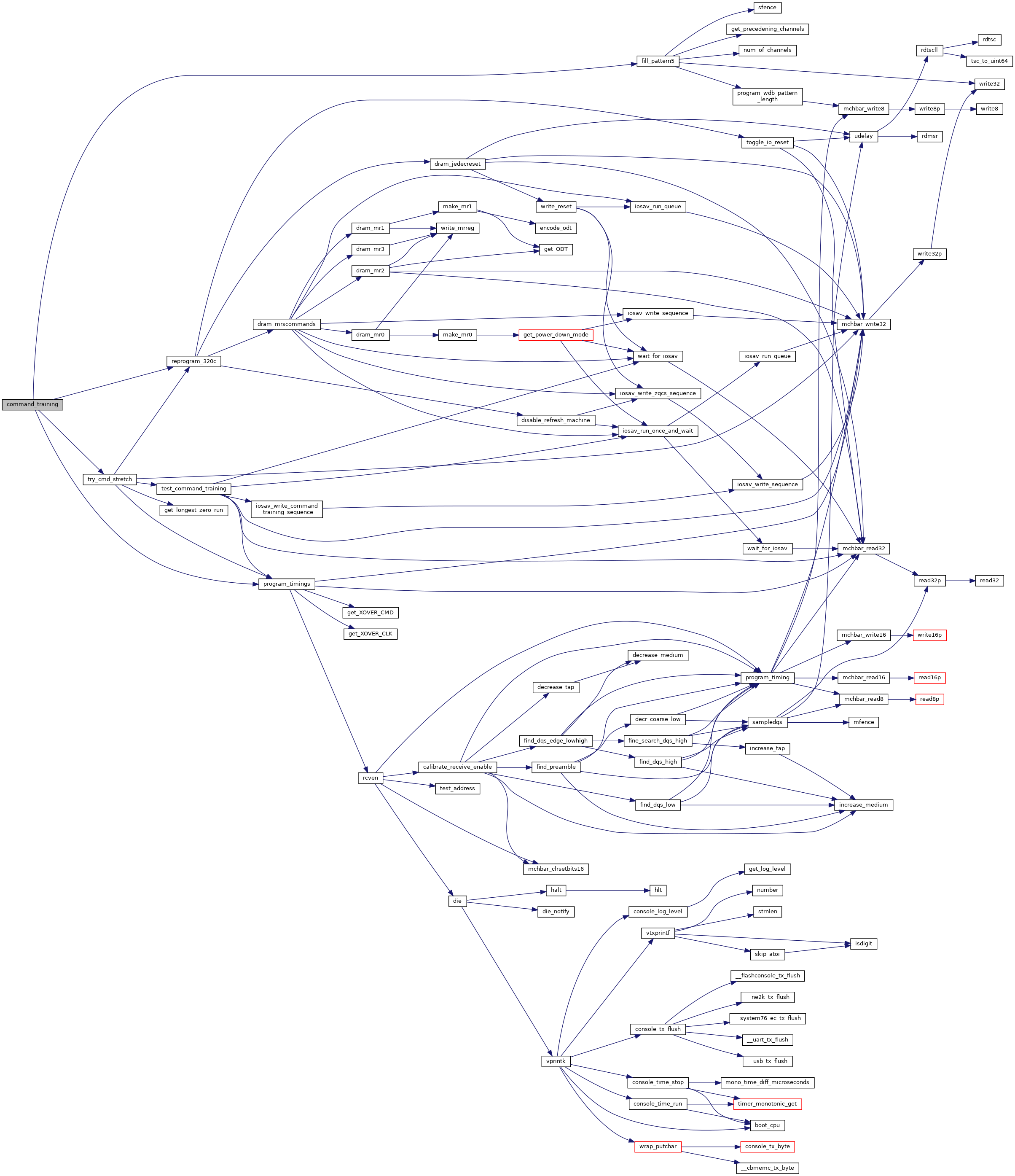

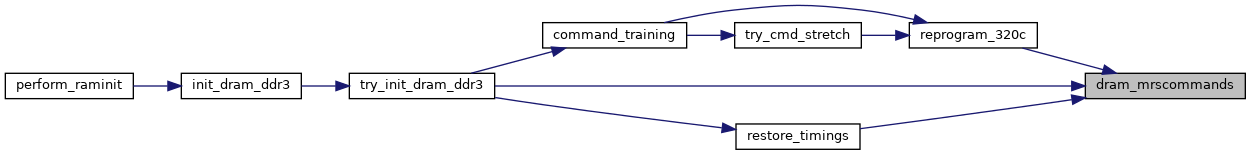

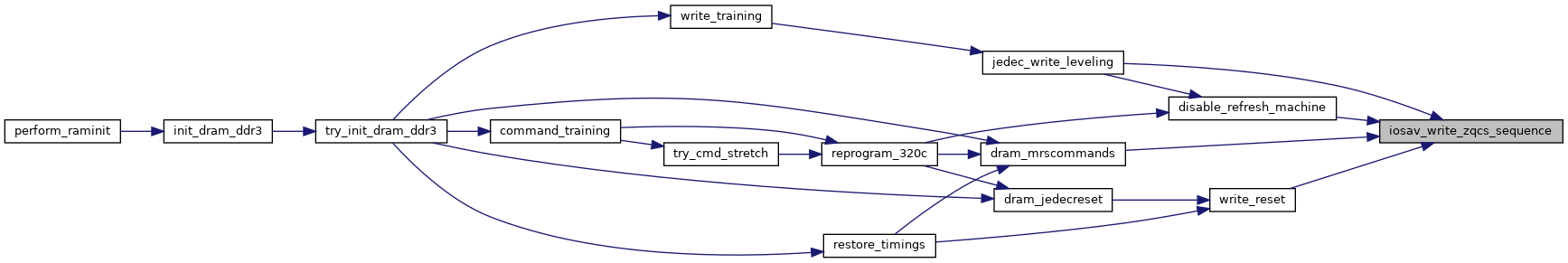

| int command_training | ( | ramctr_timing * | ctrl | ) |

Definition at line 2057 of file raminit_common.c.

References BIOS_EMERG, DIV_ROUND_UP, fill_pattern5(), FOR_ALL_POPULATED_CHANNELS, MIN, printk, printram, program_timings(), ramctr_timing_st::rankmap, reprogram_320c(), ramctr_timing_st::tCMD, and try_cmd_stretch().

Referenced by try_init_dram_ddr3().

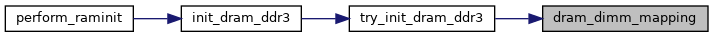

| void dram_dimm_mapping | ( | ramctr_timing * | ctrl | ) |

Definition at line 242 of file raminit_common.c.

References FOR_ALL_CHANNELS, info, ramctr_timing_st::info, ramctr_timing_st::mad_dimm, dimm_attr_ddr3_st::ranks, dimm_attr_ddr3_st::size_mb, and dimm_attr_ddr3_st::width.

Referenced by try_init_dram_ddr3().

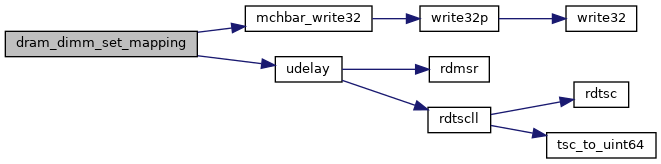

| void dram_dimm_set_mapping | ( | ramctr_timing * | ctrl, |

| int | training | ||

| ) |

Definition at line 290 of file raminit_common.c.

References ecc, ramctr_timing_st::ecc_enabled, FOR_ALL_CHANNELS, MAD_DIMM, ramctr_timing_st::mad_dimm, mchbar_write32(), and udelay().

Referenced by try_init_dram_ddr3().

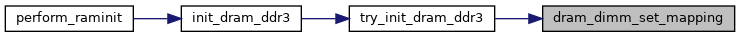

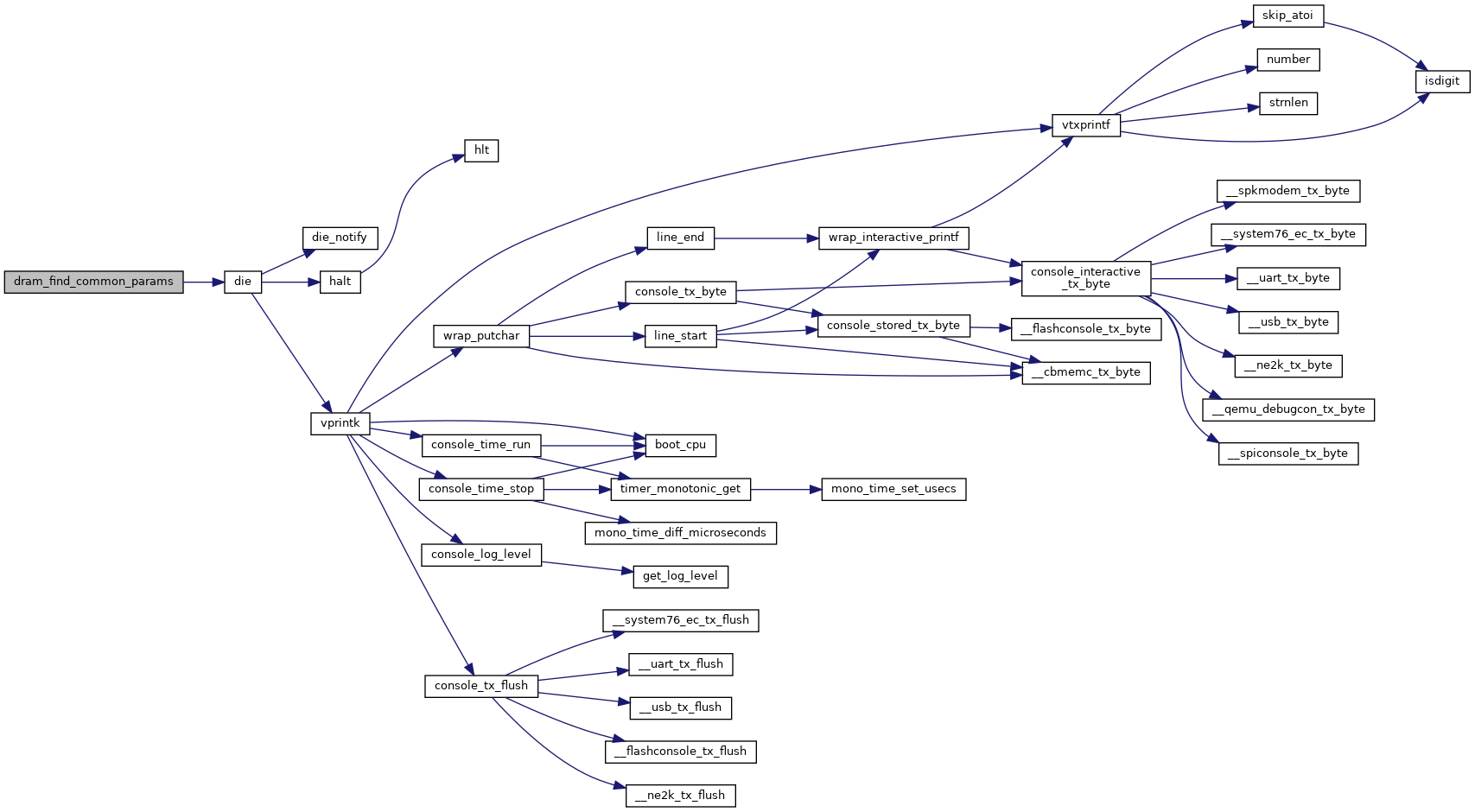

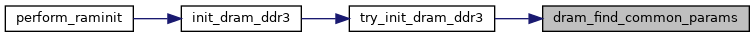

| void dram_find_common_params | ( | ramctr_timing * | ctrl | ) |

Definition at line 58 of file raminit_common.c.

References dimm_attr_ddr3_st::cas_supported, ramctr_timing_st::cas_supported, die(), dimm_attr_ddr3_st::dram_type, FOR_ALL_CHANNELS, ramctr_timing_st::info, MAX, MAX_CAS, MIN_CAS, SPD_MEMORY_TYPE_SDRAM_DDR3, dimm_attr_ddr3_st::tAA, ramctr_timing_st::tAA, dimm_attr_ddr3_st::tCK, ramctr_timing_st::tCK, dimm_attr_ddr3_st::tCMD, ramctr_timing_st::tCMD, dimm_attr_ddr3_st::tCWL, ramctr_timing_st::tCWL, dimm_attr_ddr3_st::tFAW, ramctr_timing_st::tFAW, dimm_attr_ddr3_st::tRAS, ramctr_timing_st::tRAS, dimm_attr_ddr3_st::tRCD, ramctr_timing_st::tRCD, dimm_attr_ddr3_st::tRFC, ramctr_timing_st::tRFC, dimm_attr_ddr3_st::tRP, ramctr_timing_st::tRP, dimm_attr_ddr3_st::tRRD, ramctr_timing_st::tRRD, dimm_attr_ddr3_st::tRTP, ramctr_timing_st::tRTP, dimm_attr_ddr3_st::tWR, ramctr_timing_st::tWR, dimm_attr_ddr3_st::tWTR, and ramctr_timing_st::tWTR.

Referenced by try_init_dram_ddr3().

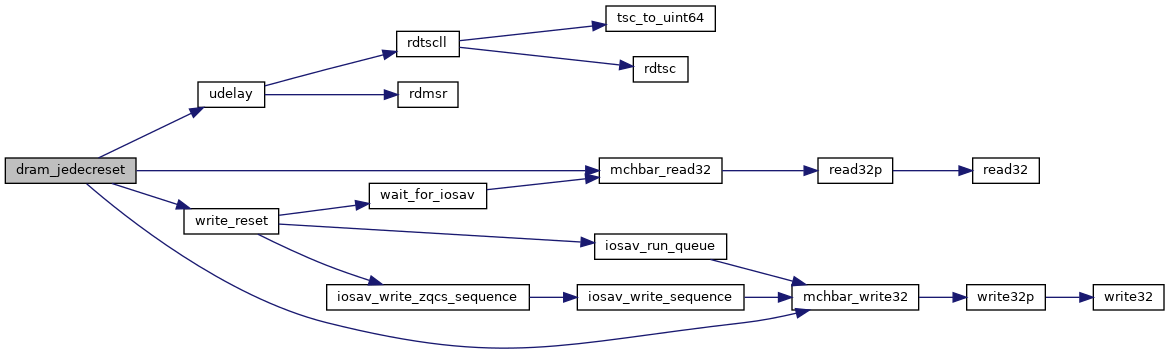

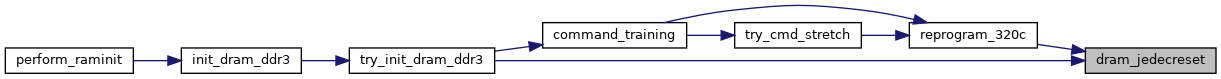

| void dram_jedecreset | ( | ramctr_timing * | ctrl | ) |

Definition at line 539 of file raminit_common.c.

References FOR_ALL_CHANNELS, IOSAV_STATUS_ch, MC_INIT_STATE, MC_INIT_STATE_ch, MC_INIT_STATE_G, mchbar_clrbits32, mchbar_read32(), mchbar_setbits32, mchbar_write32(), ramctr_timing_st::rankmap, RCOMP_TIMER, udelay(), and write_reset().

Referenced by reprogram_320c(), and try_init_dram_ddr3().

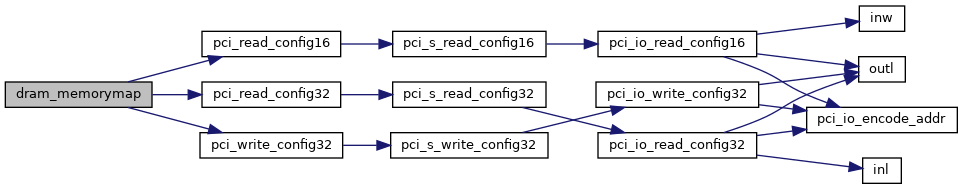

| void dram_memorymap | ( | ramctr_timing * | ctrl, |

| int | me_uma_size | ||

| ) |

Definition at line 369 of file raminit_common.c.

References BDSM, BGSM, BIOS_DEBUG, ramctr_timing_st::channel_size_mb, DEFAULT_PCI_MMIO_SIZE, GGC, HOST_BRIDGE, MAX, ME_STLEN_EN, MELCK, MESEG_BASE, MESEG_MASK, MIN, pci_read_config16(), pci_read_config32(), pci_write_config32(), printk, REMAPBASE, REMAPLIMIT, TOLUD, TOM, TOUUD, TSEGMB, and val.

Referenced by try_init_dram_ddr3().

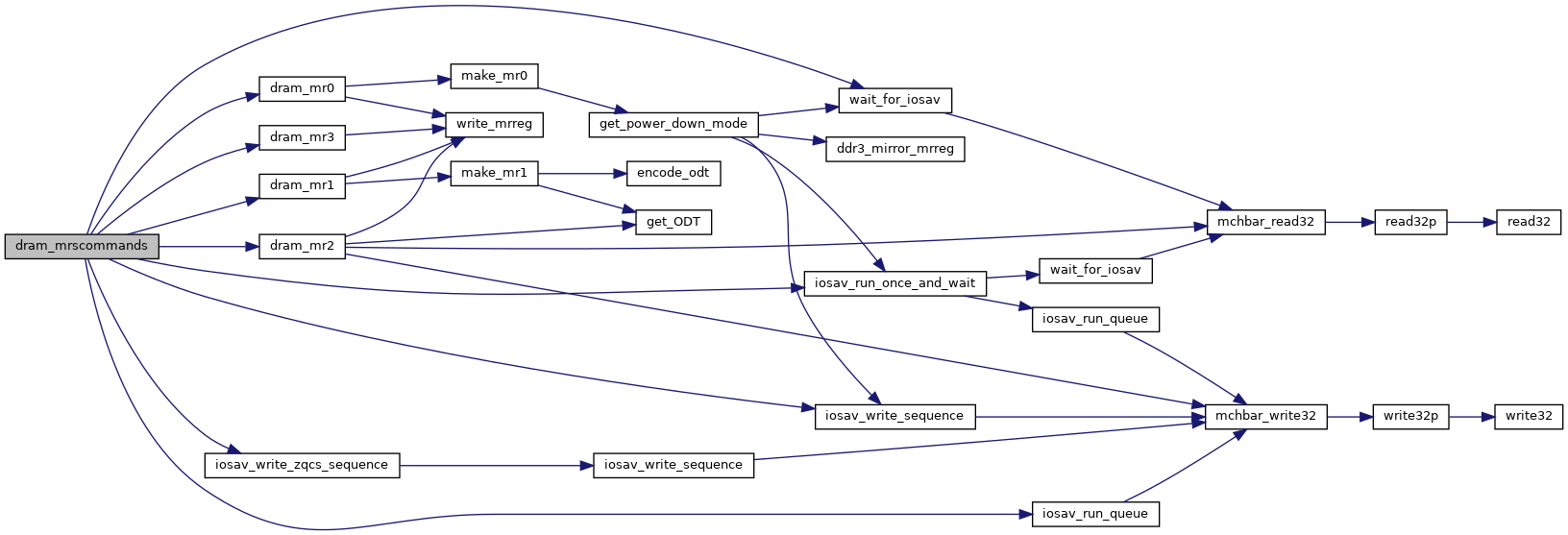

| void dram_mrscommands | ( | ramctr_timing * | ctrl | ) |

Definition at line 811 of file raminit_common.c.

References ARRAY_SIZE, BROADCAST_CH, iosav_ssq::command, dram_mr0(), dram_mr1(), dram_mr2(), dram_mr3(), FOR_ALL_CHANNELS, FOR_ALL_POPULATED_CHANNELS, FOR_ALL_POPULATED_RANKS, IOSAV_NOP, iosav_run_once_and_wait(), iosav_run_queue(), iosav_write_sequence(), iosav_write_zqcs_sequence(), IOSAV_ZQCS, MC_INIT_STATE_G, mchbar_clrbits32, mchbar_setbits32, ramctr_timing_st::rankmap, SCHED_CBIT_ch, iosav_ssq::sp_cmd_ctrl, SSQ_NA, and wait_for_iosav().

Referenced by reprogram_320c(), restore_timings(), and try_init_dram_ddr3().

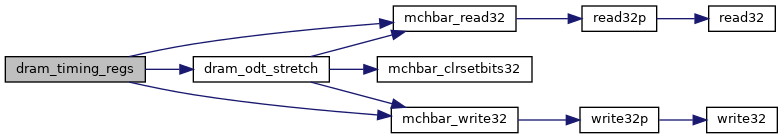

| void dram_timing_regs | ( | ramctr_timing * | ctrl | ) |

Definition at line 147 of file raminit_common.c.

References ramctr_timing_st::CAS, ramctr_timing_st::cpu, ramctr_timing_st::CWL, dram_odt_stretch(), FOR_ALL_CHANNELS, IS_IVY_CPU, mchbar_read32(), mchbar_write32(), MIN, tc_rfp_reg::oref_ri, tc_dtp_reg::overclock_tXP, printram, tc_dbp_reg::raw, tc_rap_reg::raw, tc_othp_reg::raw, tc_dtp_reg::raw, tc_rfp_reg::raw, tc_rftp_reg::raw, tc_srftp_reg::raw, ramctr_timing_st::tAONPD, TC_DBP_ch, TC_DTP_ch, TC_OTHP_ch, TC_RAP_ch, TC_RFP_ch, TC_RFTP_ch, TC_SRFTP_ch, ramctr_timing_st::tCK, ramctr_timing_st::tCKE, tDLLK, ramctr_timing_st::tFAW, ramctr_timing_st::tMOD, ramctr_timing_st::tRAS, tc_dbp_reg::tRCD, ramctr_timing_st::tRCD, tc_rftp_reg::tREFI, ramctr_timing_st::tREFI, ramctr_timing_st::tRFC, ramctr_timing_st::tRP, tc_rap_reg::tRRD, ramctr_timing_st::tRRD, ramctr_timing_st::tRTP, ramctr_timing_st::tWR, ramctr_timing_st::tWTR, ramctr_timing_st::tXP, tc_othp_reg::tXPDLL, ramctr_timing_st::tXPDLL, tc_srftp_reg::tXSDLL, and ramctr_timing_st::tXSOffset.

Referenced by try_init_dram_ddr3().

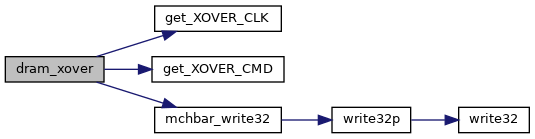

| void dram_xover | ( | ramctr_timing * | ctrl | ) |

Definition at line 101 of file raminit_common.c.

References FOR_ALL_CHANNELS, GDCRCKPICODE_ch, GDCRCMDPICODING_ch, get_XOVER_CLK(), get_XOVER_CMD(), mchbar_write32(), printram, and ramctr_timing_st::rankmap.

Referenced by try_init_dram_ddr3().

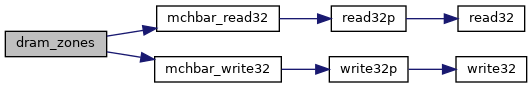

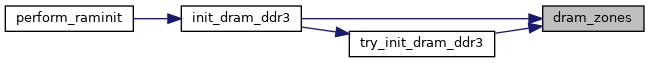

| void dram_zones | ( | ramctr_timing * | ctrl, |

| int | training | ||

| ) |

Definition at line 308 of file raminit_common.c.

References ramctr_timing_st::channel_size_mb, MAD_CHNL, MAD_ZR, mchbar_read32(), mchbar_write32(), and val.

Referenced by init_dram_ddr3(), and try_init_dram_ddr3().

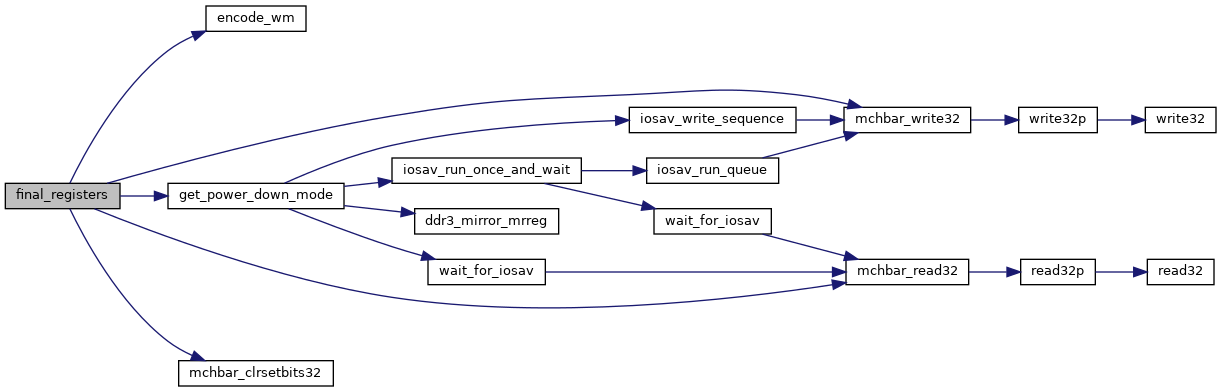

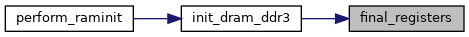

| void final_registers | ( | ramctr_timing * | ctrl | ) |

Definition at line 2806 of file raminit_common.c.

References BANDTIMERS_IVB, BANDTIMERS_SNB, BIOS_DEBUG, encode_wm(), FOR_ALL_CHANNELS, FOR_ALL_POPULATED_CHANNELS, get_power_down_mode(), MC_INIT_STATE_G, mchbar_clrbits32, mchbar_clrsetbits32(), mchbar_read32(), mchbar_setbits32, mchbar_write32(), ramctr_timing_st::mdll_wake_delay, MEM_TRML_ESTIMATION_CONFIG, MEM_TRML_INTERRUPT, MEM_TRML_THRESHOLDS_CONFIG, PM_BW_LIMIT_CONFIG, PM_CMD_PWR_ch, PM_DLL_CONFIG, PM_PDWN_CONFIG, PM_TRML_M_CONFIG_ch, printk, ramctr_timing_st::rankmap, tc_othp_reg::raw, tc_rfp_reg::raw, tc_rfp_reg::refresh_2x_control, SAPMCTL, SAPMTIMERS, SAPMTIMERS2_IVB, SSKPD, TC_OTHP_ch, TC_RFP_ch, TC_SRFTP_ch, TC_ZQCAL_ch, ramctr_timing_st::tCK, tc_othp_reg::tCPDED, and WMM_READ_CONFIG.

Referenced by init_dram_ddr3().

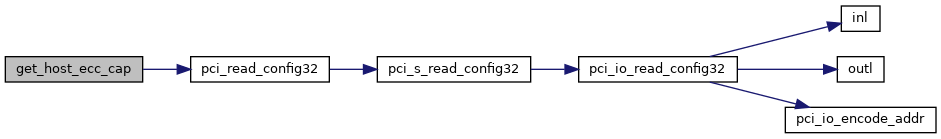

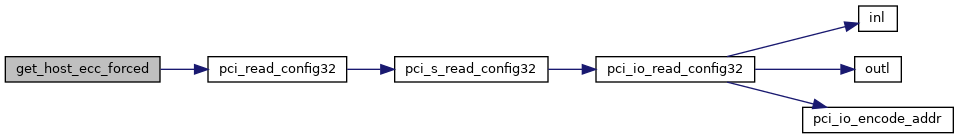

Definition at line 360 of file raminit_common.c.

References CAPID0_A, HOST_BRIDGE, and pci_read_config32().

Referenced by reinit_ctrl().

Definition at line 347 of file raminit_common.c.

References CAPID0_A, HOST_BRIDGE, and pci_read_config32().

Referenced by reinit_ctrl().

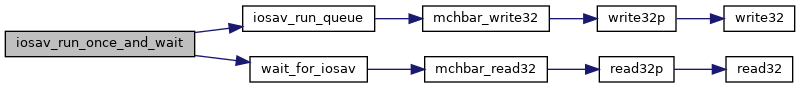

| void iosav_run_once_and_wait | ( | const int | ch | ) |

Definition at line 45 of file raminit_iosav.c.

References ch, iosav_run_queue(), and wait_for_iosav().

Referenced by channel_test(), disable_refresh_machine(), dram_mrscommands(), find_agrsv_read_margin(), find_predefined_pattern(), find_read_mpr_margin(), get_power_down_mode(), jedec_write_leveling(), receive_enable_calibration(), test_aggressive_write(), test_command_training(), test_rcven(), test_tx_dq(), train_write_flyby(), tx_dq_write_leveling(), and write_level_rank().

Definition at line 28 of file raminit_iosav.c.

References ch, IOSAV_SEQ_CTL_ch, mchbar_write32(), and ssq_count.

Referenced by channel_scrub(), dram_mrscommands(), iosav_run_once_and_wait(), and write_reset().

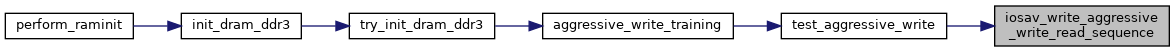

| void iosav_write_aggressive_write_read_sequence | ( | ramctr_timing * | ctrl, |

| int | channel, | ||

| int | slotrank | ||

| ) |

Definition at line 681 of file raminit_iosav.c.

References ARRAY_SIZE, iosav_ssq::command, ramctr_timing_st::CWL, IOSAV_ACT, IOSAV_PRE, IOSAV_RD, IOSAV_WR, iosav_write_sequence(), MAX, iosav_ssq::sp_cmd_ctrl, SSQ_NA, SSQ_RD, SSQ_WR, ramctr_timing_st::tFAW, ramctr_timing_st::tRCD, ramctr_timing_st::tRP, ramctr_timing_st::tRRD, ramctr_timing_st::tRTP, and ramctr_timing_st::tWTR.

Referenced by test_aggressive_write().

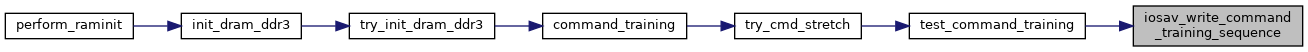

| void iosav_write_command_training_sequence | ( | ramctr_timing * | ctrl, |

| int | channel, | ||

| int | slotrank, | ||

| unsigned int | address | ||

| ) |

Definition at line 483 of file raminit_iosav.c.

References address, ARRAY_SIZE, iosav_ssq::command, ramctr_timing_st::CWL, IOSAV_ACT, IOSAV_PRE, IOSAV_RD, IOSAV_WR, iosav_write_sequence(), MAX, iosav_ssq::sp_cmd_ctrl, SSQ_NA, SSQ_RD, SSQ_WR, ramctr_timing_st::tFAW, ramctr_timing_st::tRCD, ramctr_timing_st::tRRD, ramctr_timing_st::tRTP, and ramctr_timing_st::tWTR.

Referenced by test_command_training().

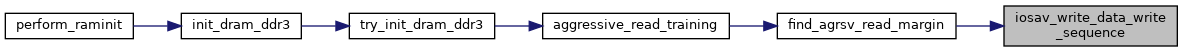

| void iosav_write_data_write_sequence | ( | ramctr_timing * | ctrl, |

| int | channel, | ||

| int | slotrank | ||

| ) |

Definition at line 586 of file raminit_iosav.c.

References ARRAY_SIZE, iosav_ssq::command, ramctr_timing_st::CWL, IOSAV_ACT, IOSAV_PRE, IOSAV_RD, IOSAV_WR, iosav_write_sequence(), MAX, iosav_ssq::sp_cmd_ctrl, SSQ_NA, SSQ_RD, SSQ_WR, ramctr_timing_st::tFAW, ramctr_timing_st::tRCD, ramctr_timing_st::tRP, ramctr_timing_st::tRRD, ramctr_timing_st::tRTP, and ramctr_timing_st::tWTR.

Referenced by find_agrsv_read_margin().

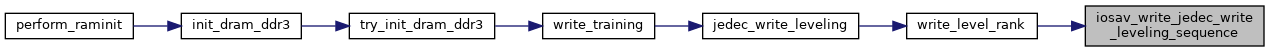

| void iosav_write_jedec_write_leveling_sequence | ( | ramctr_timing * | ctrl, |

| int | channel, | ||

| int | slotrank, | ||

| int | bank, | ||

| u32 | mr1reg | ||

| ) |

Definition at line 298 of file raminit_iosav.c.

References ARRAY_SIZE, iosav_ssq::bank, ramctr_timing_st::CAS, iosav_ssq::command, ramctr_timing_st::CWL, IOSAV_MRS, IOSAV_NOP, IOSAV_NOP_ALT, iosav_write_sequence(), iosav_ssq::sp_cmd_ctrl, SSQ_NA, SSQ_RD, SSQ_WR, ramctr_timing_st::tMOD, and ramctr_timing_st::tWLO.

Referenced by write_level_rank().

| void iosav_write_memory_test_sequence | ( | ramctr_timing * | ctrl, |

| int | channel, | ||

| int | slotrank | ||

| ) |

Definition at line 776 of file raminit_iosav.c.

References ARRAY_SIZE, iosav_ssq::command, IOSAV_ACT, IOSAV_PRE, IOSAV_RD, IOSAV_WR, iosav_write_sequence(), iosav_ssq::sp_cmd_ctrl, SSQ_NA, SSQ_RD, and SSQ_WR.

Referenced by channel_test().

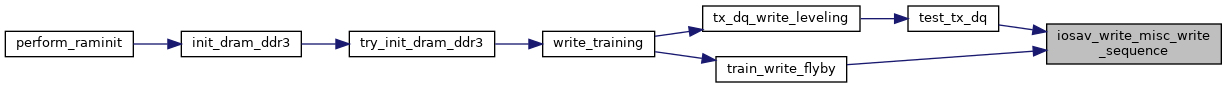

| void iosav_write_misc_write_sequence | ( | ramctr_timing * | ctrl, |

| int | channel, | ||

| int | slotrank, | ||

| u32 | gap0, | ||

| u32 | loops0, | ||

| u32 | gap1, | ||

| u32 | loops2, | ||

| u32 | wrap2 | ||

| ) |

Definition at line 385 of file raminit_iosav.c.

References ARRAY_SIZE, iosav_ssq::command, ramctr_timing_st::CWL, IOSAV_ACT, IOSAV_NOP, IOSAV_WR, iosav_write_sequence(), iosav_ssq::sp_cmd_ctrl, SSQ_NA, SSQ_WR, ramctr_timing_st::tRCD, and ramctr_timing_st::tWTR.

Referenced by test_tx_dq(), and train_write_flyby().

| void iosav_write_prea_act_read_sequence | ( | ramctr_timing * | ctrl, |

| int | channel, | ||

| int | slotrank | ||

| ) |

Definition at line 201 of file raminit_iosav.c.

References ARRAY_SIZE, ramctr_timing_st::CAS, iosav_ssq::command, IOSAV_ACT, IOSAV_PRE, IOSAV_RD, iosav_write_sequence(), MAX, iosav_ssq::sp_cmd_ctrl, SSQ_NA, SSQ_RD, ramctr_timing_st::tFAW, ramctr_timing_st::tRP, ramctr_timing_st::tRRD, and ramctr_timing_st::tRTP.

Referenced by test_tx_dq().

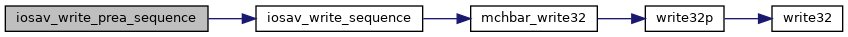

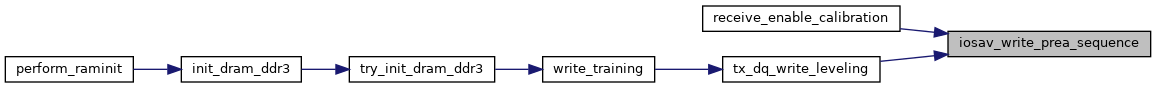

Definition at line 79 of file raminit_iosav.c.

References ARRAY_SIZE, iosav_ssq::command, IOSAV_PRE, iosav_write_sequence(), iosav_ssq::sp_cmd_ctrl, and SSQ_NA.

Referenced by receive_enable_calibration(), and tx_dq_write_leveling().

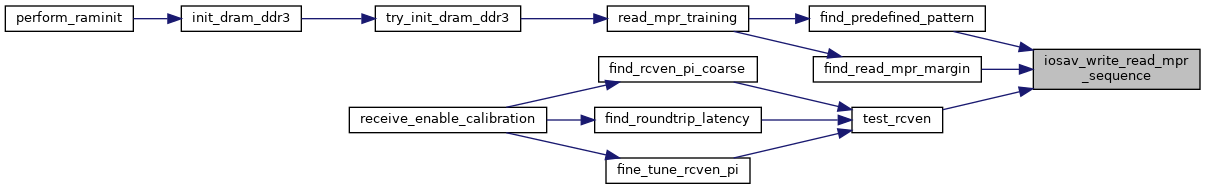

| void iosav_write_read_mpr_sequence | ( | int | channel, |

| int | slotrank, | ||

| u32 | tMOD, | ||

| u32 | loops, | ||

| u32 | gap, | ||

| u32 | loops2, | ||

| u32 | post2 | ||

| ) |

Definition at line 108 of file raminit_iosav.c.

References ARRAY_SIZE, iosav_ssq::command, IOSAV_MRS, IOSAV_RD, iosav_write_sequence(), iosav_ssq::sp_cmd_ctrl, SSQ_NA, and SSQ_RD.

Referenced by find_predefined_pattern(), find_read_mpr_margin(), and test_rcven().

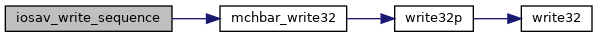

Definition at line 16 of file raminit_iosav.c.

References ch, IOSAV_n_ADDR_UPDATE_ch, IOSAV_n_SP_CMD_ADDR_ch, IOSAV_n_SP_CMD_CTRL_ch, IOSAV_n_SUBSEQ_CTRL_ch, length, mchbar_write32(), iosav_ssq::raw, and ssq_count.

Referenced by channel_scrub(), dram_mrscommands(), get_power_down_mode(), iosav_write_aggressive_write_read_sequence(), iosav_write_command_training_sequence(), iosav_write_data_write_sequence(), iosav_write_jedec_write_leveling_sequence(), iosav_write_memory_test_sequence(), iosav_write_misc_write_sequence(), iosav_write_prea_act_read_sequence(), iosav_write_prea_sequence(), iosav_write_read_mpr_sequence(), iosav_write_zqcs_sequence(), and train_write_flyby().

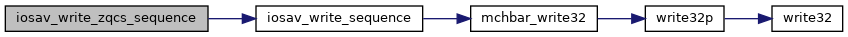

Definition at line 51 of file raminit_iosav.c.

References ARRAY_SIZE, iosav_ssq::command, iosav_write_sequence(), IOSAV_ZQCS, iosav_ssq::sp_cmd_ctrl, and SSQ_NA.

Referenced by disable_refresh_machine(), dram_mrscommands(), jedec_write_leveling(), and write_reset().

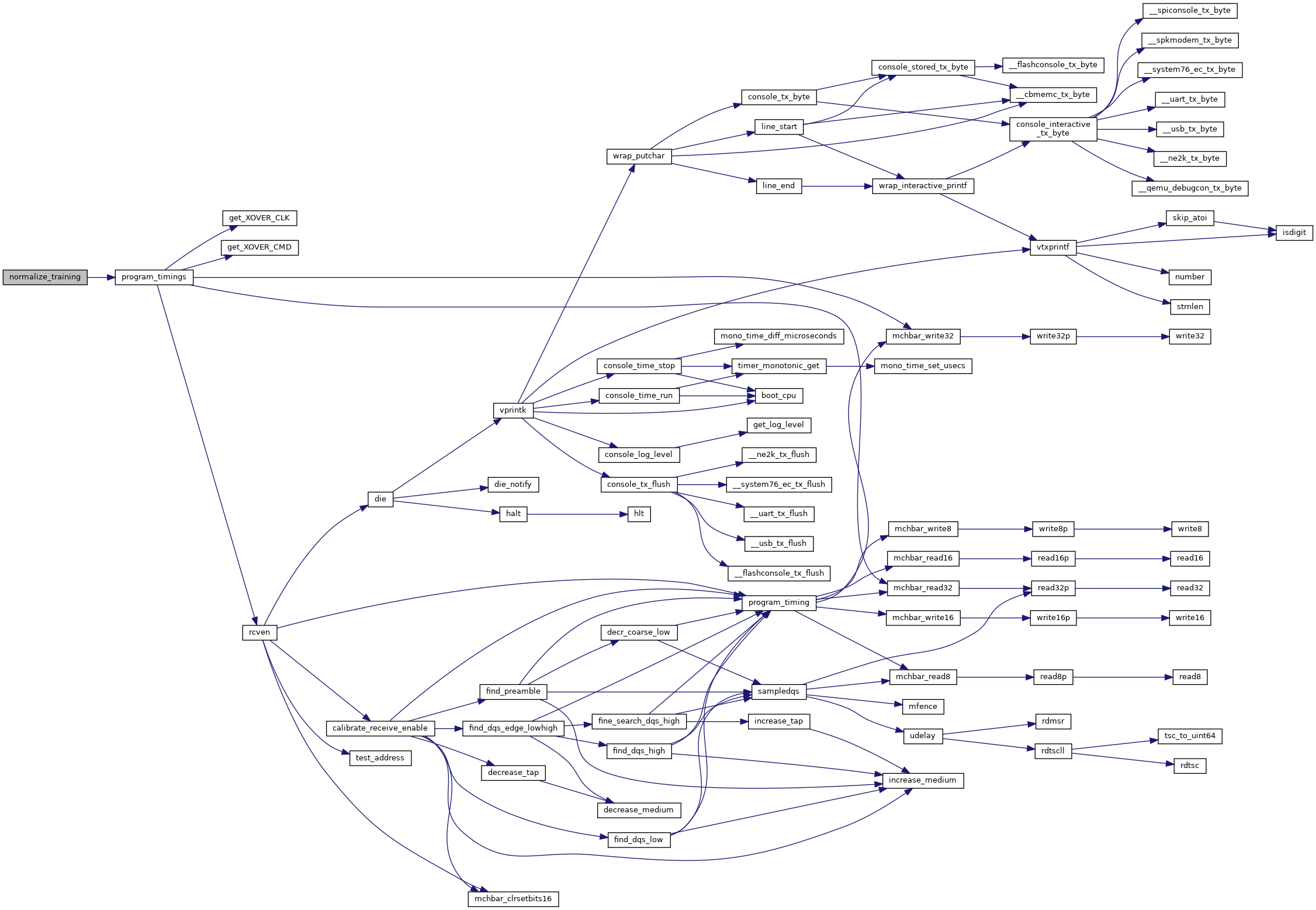

| void normalize_training | ( | ramctr_timing * | ctrl | ) |

Definition at line 2532 of file raminit_common.c.

References FOR_ALL_CHANNELS, FOR_ALL_LANES, FOR_ALL_POPULATED_CHANNELS, FOR_ALL_POPULATED_RANKS, ram_rank_timings::io_latency, ram_rank_timings::lanes, MAX, printram, program_timings(), ram_rank_timings::ram_lane_timings::rcven, ram_rank_timings::roundtrip_latency, and ramctr_timing_st::timings.

Referenced by try_init_dram_ddr3().

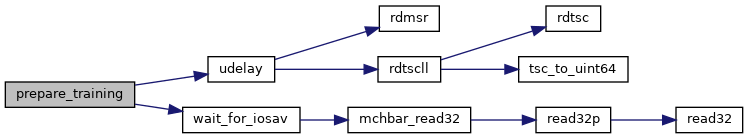

| void prepare_training | ( | ramctr_timing * | ctrl | ) |

Definition at line 2738 of file raminit_common.c.

References FOR_ALL_POPULATED_CHANNELS, mchbar_setbits32, TC_RAP_ch, udelay(), and wait_for_iosav().

Referenced by try_init_dram_ddr3().

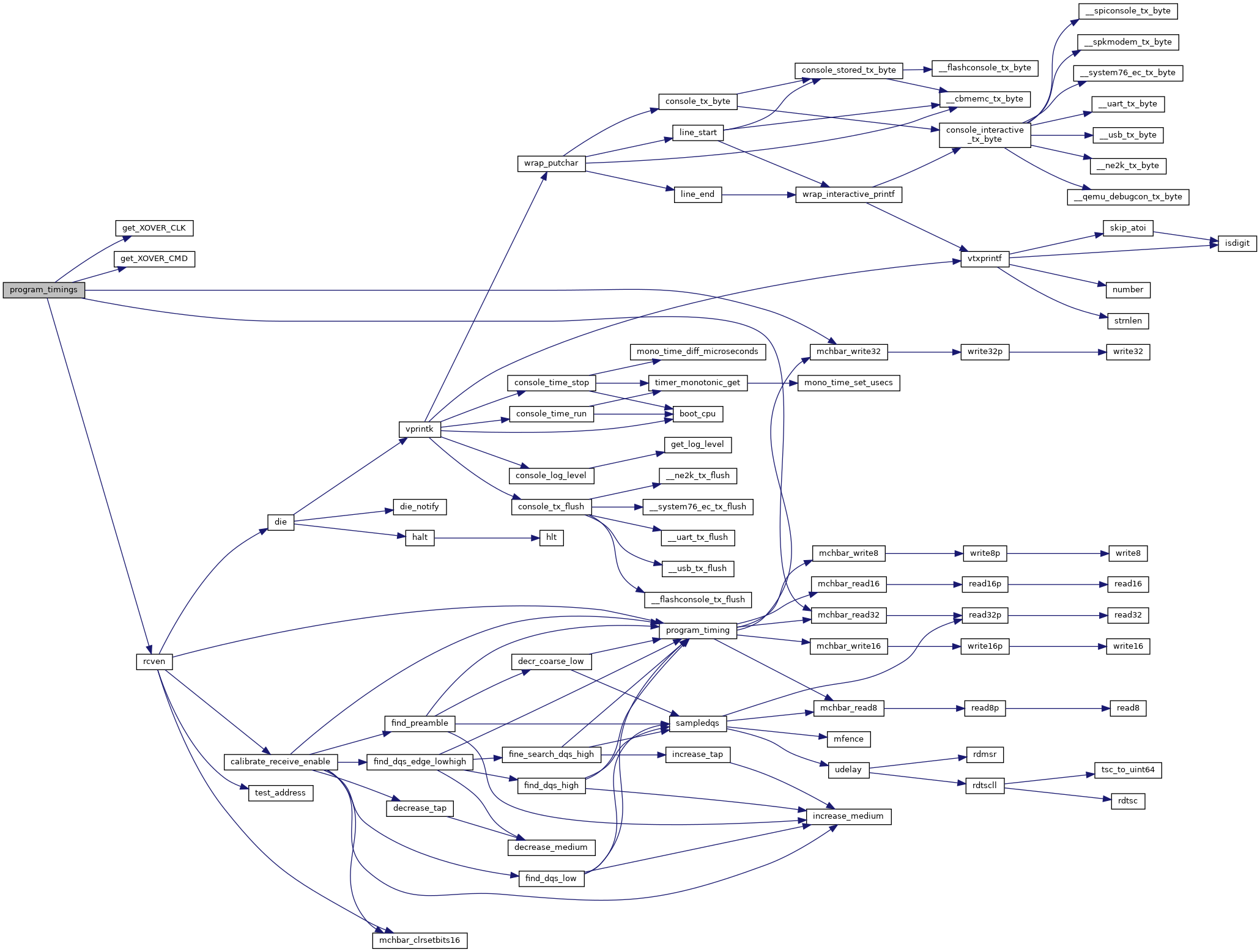

| void program_timings | ( | ramctr_timing * | ctrl, |

| int | channel | ||

| ) |

Definition at line 910 of file raminit_common.c.

References BIOS_ERR, CCC_MAX_PI, gdcr_cmd_pi_coding_reg::cmd_logic_delay, gdcr_cmd_pi_coding_reg::cmd_pi_code, gdcr_cmd_pi_coding_reg::ctl_logic_delay_d0, gdcr_cmd_pi_coding_reg::ctl_logic_delay_d1, gdcr_cmd_pi_coding_reg::ctl_pi_code_d0, gdcr_cmd_pi_coding_reg::ctl_pi_code_d1, FOR_ALL_LANES, FOR_ALL_POPULATED_RANKS, GDCRCKLOGICDELAY_ch, GDCRCKPICODE_ch, GDCRCMDPICODING_ch, GDCRRX, GDCRTX, get_XOVER_CLK(), get_XOVER_CMD(), ram_rank_timings::io_latency, lane_base, ram_rank_timings::lanes, MAX, mchbar_read32(), mchbar_write32(), NUM_SLOTS, ramctr_timing_st::pi_code_offset, ram_rank_timings::pi_coding, printk, QCLK_PI, ramctr_timing_st::rankmap, gdcr_rx_reg::raw, gdcr_tx_reg::raw, gdcr_cmd_pi_coding_reg::raw, ram_rank_timings::ram_lane_timings::rcven, rcven(), gdcr_rx_reg::rcven_pi_code, ram_rank_timings::roundtrip_latency, ram_rank_timings::ram_lane_timings::rx_dqs_n, ram_rank_timings::ram_lane_timings::rx_dqs_p, SC_IO_LATENCY_ch, SC_ROUNDT_LAT_ch, ramctr_timing_st::timings, ram_rank_timings::ram_lane_timings::tx_dq, gdcr_tx_reg::tx_dq_pi_code, and ram_rank_timings::ram_lane_timings::tx_dqs.

Referenced by aggressive_read_training(), aggressive_write_training(), command_training(), find_agrsv_read_margin(), find_predefined_pattern(), find_rcven_pi_coarse(), find_read_mpr_margin(), find_roundtrip_latency(), fine_tune_rcven_pi(), normalize_training(), read_mpr_training(), receive_enable_calibration(), restore_timings(), test_command_training(), try_cmd_stretch(), tx_dq_write_leveling(), write_level_rank(), and write_training().

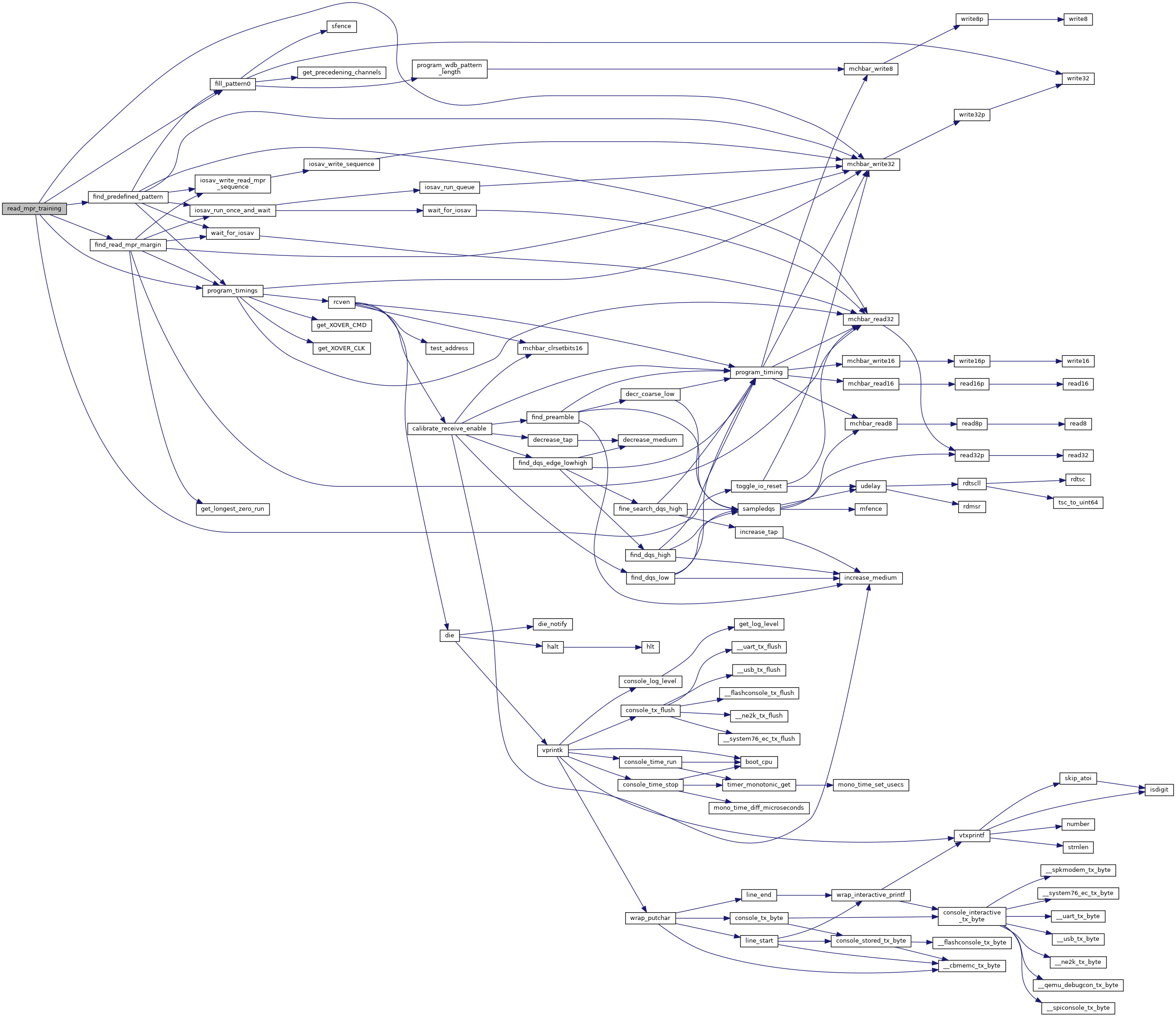

| int read_mpr_training | ( | ramctr_timing * | ctrl | ) |

Definition at line 2204 of file raminit_common.c.

References fill_pattern0(), find_predefined_pattern(), find_read_mpr_margin(), FOR_ALL_CHANNELS, FOR_ALL_LANES, FOR_ALL_POPULATED_CHANNELS, FOR_ALL_POPULATED_RANKS, GDCRTRAININGMOD, IOSAV_By_BW_MASK_ch, IOSAV_DC_MASK, ram_rank_timings::lanes, mchbar_write32(), NUM_CHANNELS, NUM_LANES, NUM_SLOTRANKS, printram, program_timings(), ram_rank_timings::ram_lane_timings::rx_dqs_n, ram_rank_timings::ram_lane_timings::rx_dqs_p, ramctr_timing_st::timings, and toggle_io_reset().

Referenced by try_init_dram_ddr3().

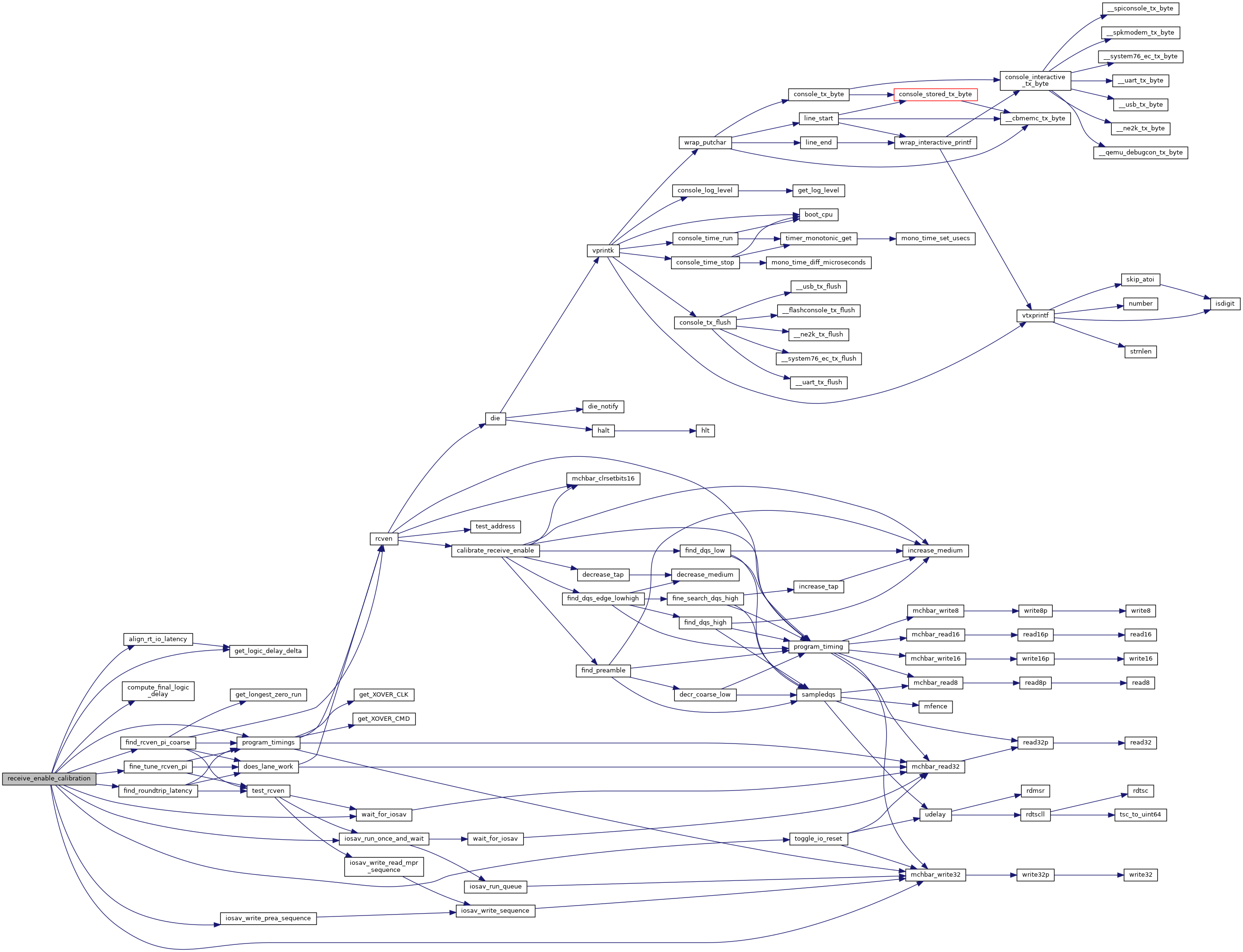

| int receive_enable_calibration | ( | ramctr_timing * | ctrl | ) |

Definition at line 1312 of file raminit_common.c.

References align_rt_io_latency(), compute_final_logic_delay(), find_rcven_pi_coarse(), find_roundtrip_latency(), fine_tune_rcven_pi(), FOR_ALL_CHANNELS, FOR_ALL_LANES, FOR_ALL_POPULATED_CHANNELS, FOR_ALL_POPULATED_RANKS, GDCRTRAININGMOD, get_logic_delay_delta(), ram_rank_timings::io_latency, iosav_run_once_and_wait(), iosav_write_prea_sequence(), ram_rank_timings::lanes, mchbar_write32(), NUM_LANES, printram, program_timings(), QCLK_PI, gdcr_training_mod_reg::raw, ram_rank_timings::ram_lane_timings::rcven, gdcr_training_mod_reg::receive_enable_mode, ram_rank_timings::roundtrip_latency, ramctr_timing_st::timings, toggle_io_reset(), ramctr_timing_st::tRP, and wait_for_iosav().

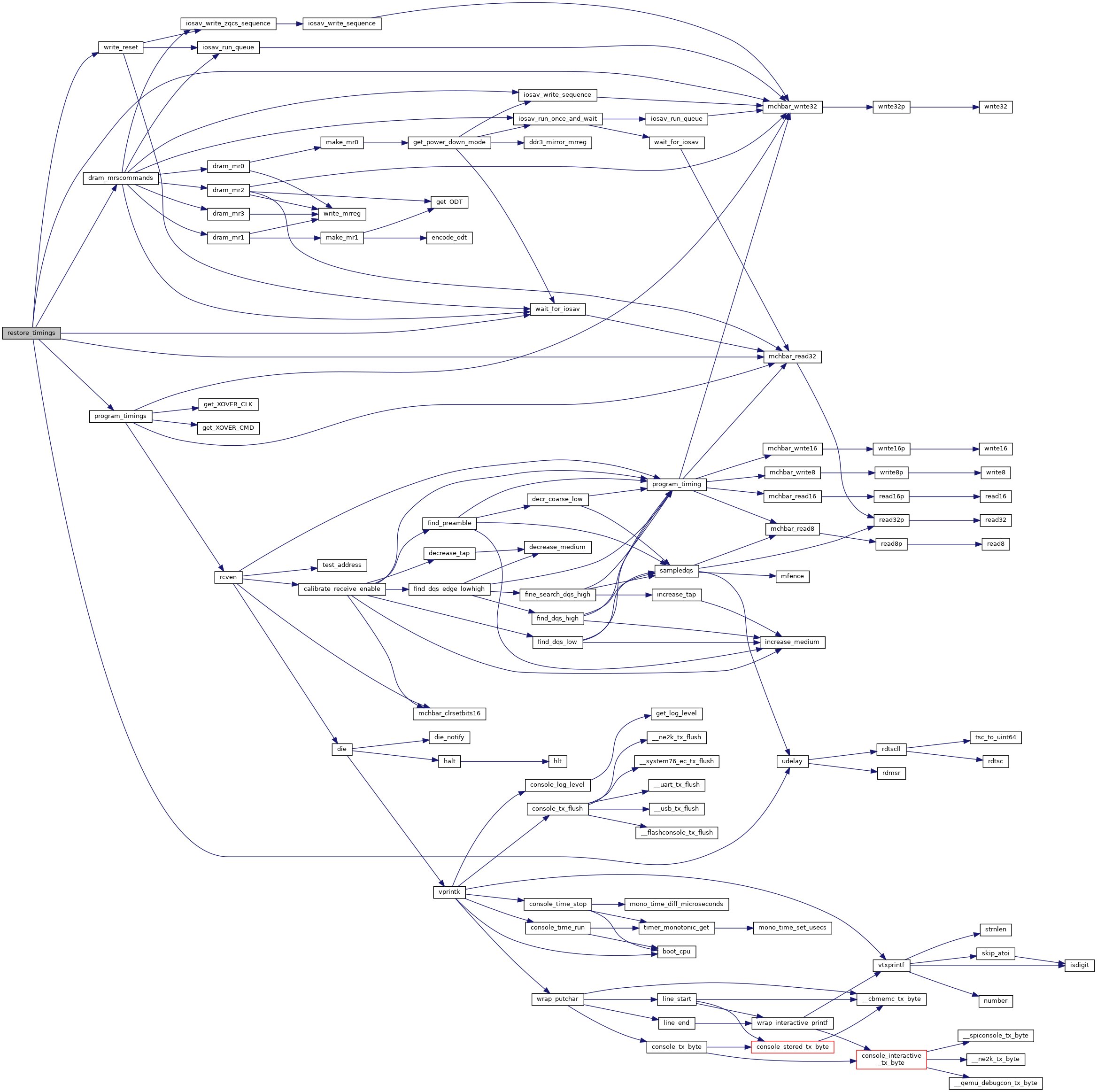

| void restore_timings | ( | ramctr_timing * | ctrl | ) |

Definition at line 2896 of file raminit_common.c.

References addr, ramctr_timing_st::cmd_stretch, dram_mrscommands(), FOR_ALL_CHANNELS, FOR_ALL_POPULATED_CHANNELS, GDCRCMDDEBUGMUXCFG_Cz_S, GDCRTRAININGMOD, GDCRTRAININGMOD_ch, IOSAV_DC_MASK, IOSAV_STATUS_ch, MC_INIT_STATE, MC_INIT_STATE_ch, MC_INIT_STATE_G, mchbar_clrbits32, mchbar_read32(), mchbar_setbits32, mchbar_write32(), printram, program_timings(), ramctr_timing_st::rankmap, tc_rap_reg::raw, RCOMP_TIMER, SCHED_CBIT_ch, TC_RAP_ch, TC_RWP_ch, ramctr_timing_st::tCKE, ramctr_timing_st::tFAW, tc_rap_reg::tRRD, ramctr_timing_st::tRRD, ramctr_timing_st::tRTP, ramctr_timing_st::tWR, ramctr_timing_st::tWTR, udelay(), wait_for_iosav(), and write_reset().

Referenced by try_init_dram_ddr3().

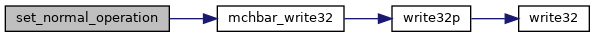

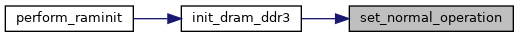

| void set_normal_operation | ( | ramctr_timing * | ctrl | ) |

Definition at line 2790 of file raminit_common.c.

References FOR_ALL_POPULATED_CHANNELS, MC_INIT_STATE_ch, mchbar_clrbits32, mchbar_write32(), ramctr_timing_st::rankmap, and TC_RAP_ch.

Referenced by init_dram_ddr3().

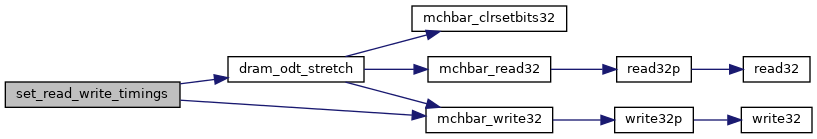

| void set_read_write_timings | ( | ramctr_timing * | ctrl | ) |

Definition at line 2754 of file raminit_common.c.

References dram_odt_stretch(), FOR_ALL_POPULATED_CHANNELS, FOR_ALL_POPULATED_RANKS, MAX, mchbar_write32(), MIN, ram_rank_timings::pi_coding, ramctr_timing_st::pi_coding_threshold, tc_rwp_reg::raw, ramctr_timing_st::ref_card_offset, TC_RWP_ch, ramctr_timing_st::tCK, TCK_1066MHZ, ramctr_timing_st::timings, tc_rwp_reg::tRRDR, tc_rwp_reg::tWRDRDD, and val.

Referenced by try_init_dram_ddr3().

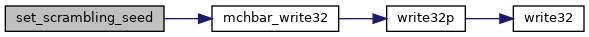

| void set_scrambling_seed | ( | ramctr_timing * | ctrl | ) |

Definition at line 2712 of file raminit_common.c.

References FOR_ALL_POPULATED_CHANNELS, mchbar_clrbits32, mchbar_write32(), NUM_CHANNELS, SCHED_CBIT_ch, SCRAMBLING_SEED_1_ch, SCRAMBLING_SEED_2_HI_ch, and SCRAMBLING_SEED_2_LO_ch.

Referenced by init_dram_ddr3().

Definition at line 2729 of file raminit_common.c.

References IS_SANDY_CPU, IS_SANDY_CPU_D0, IS_SANDY_CPU_D1, mchbar_write32(), and SC_WDBWM.

Referenced by try_init_dram_ddr3().

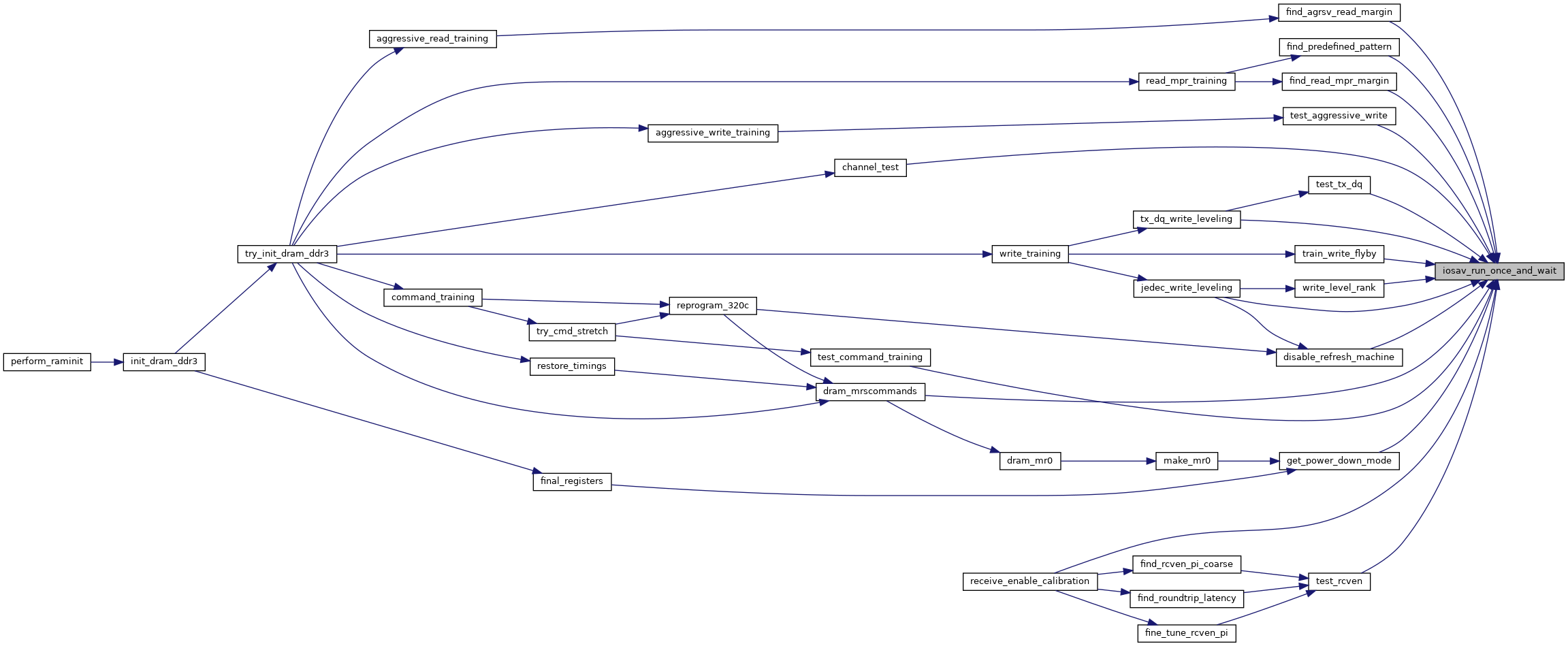

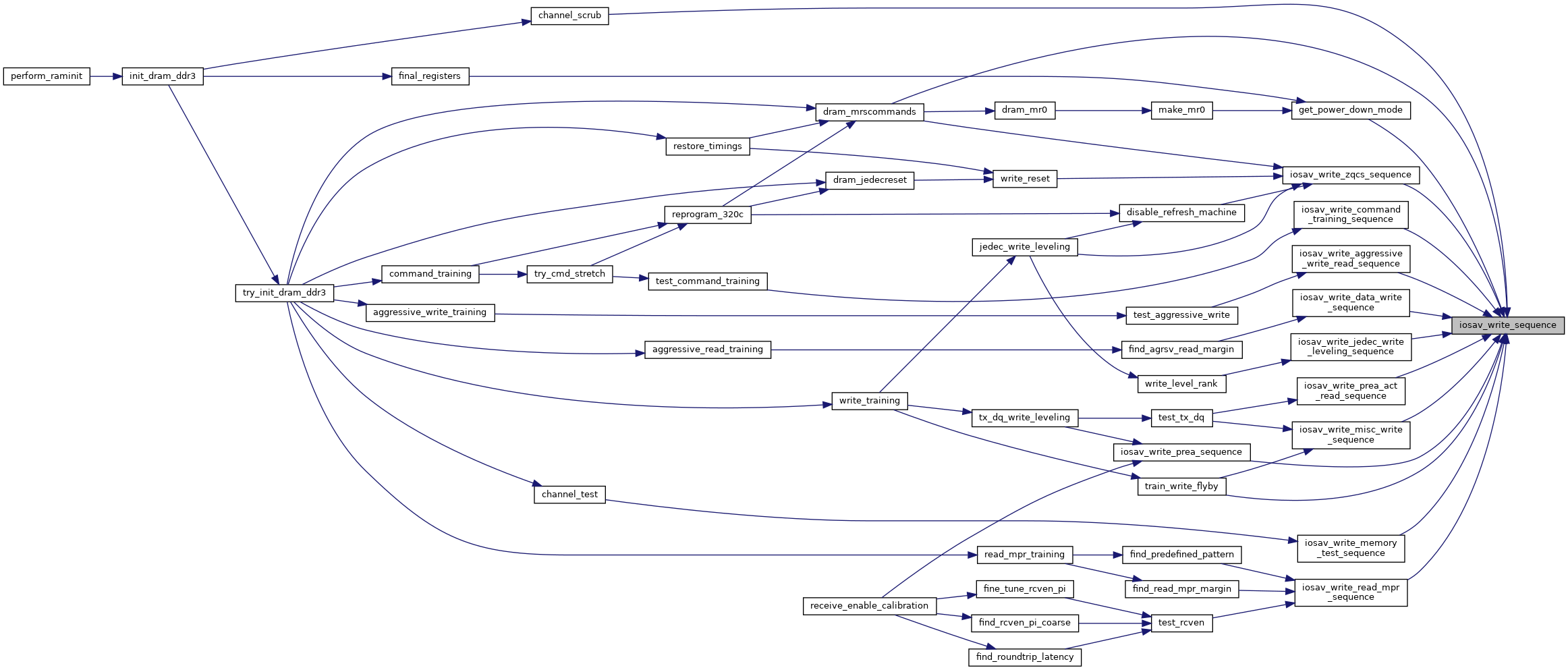

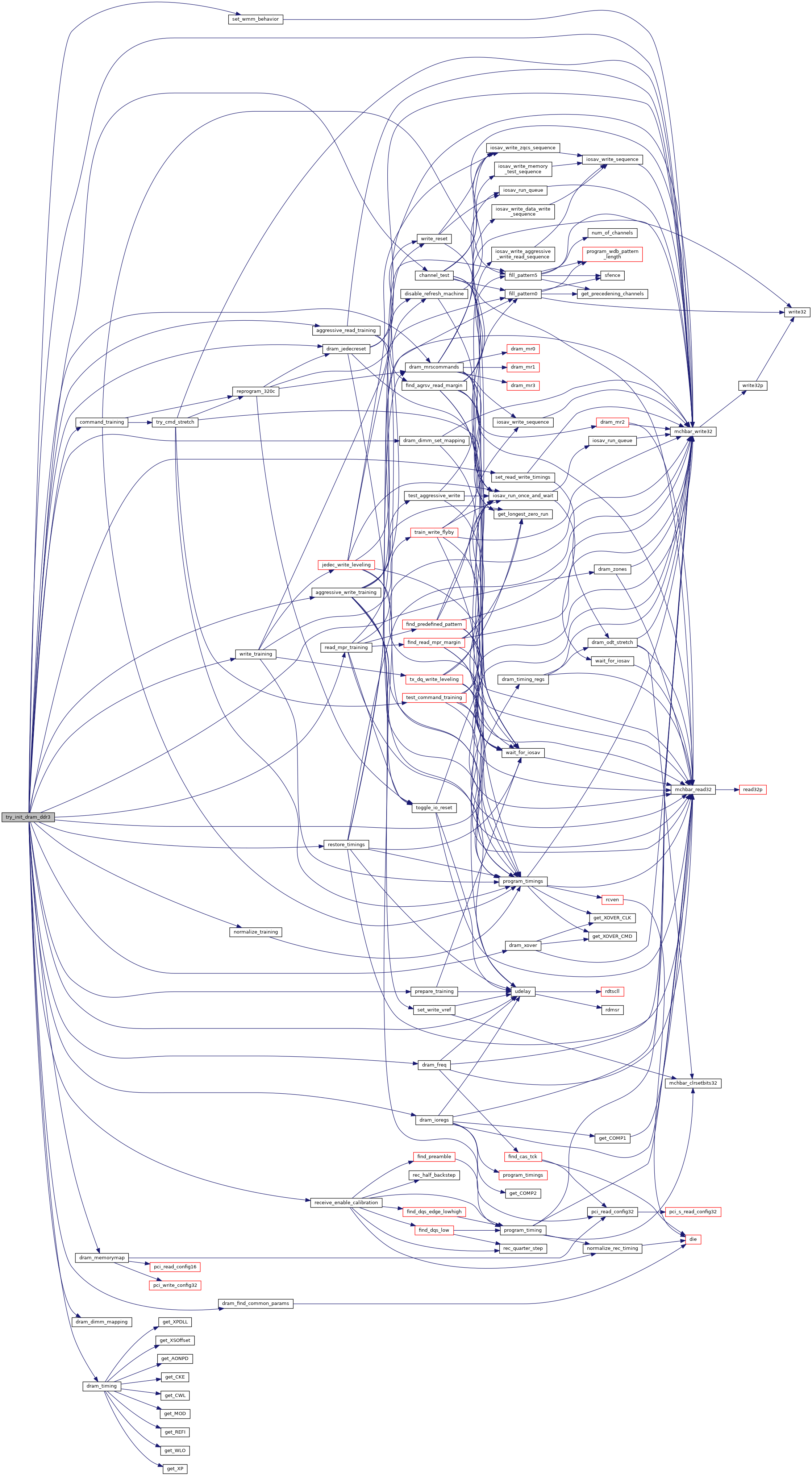

| int try_init_dram_ddr3 | ( | ramctr_timing * | ctrl, |

| int | fast_boot, | ||

| int | s3resume, | ||

| int | me_uma_size | ||

| ) |

Definition at line 633 of file raminit_native.c.

References aggressive_read_training(), aggressive_write_training(), BIOS_DEBUG, channel_test(), command_training(), ramctr_timing_st::cpu, dram_dimm_mapping(), dram_dimm_set_mapping(), dram_find_common_params(), dram_freq(), dram_ioregs(), dram_jedecreset(), dram_memorymap(), dram_mrscommands(), dram_timing(), dram_timing_regs(), dram_xover(), dram_zones(), IS_SANDY_CPU, MC_INIT_STATE_G, mchbar_clrbits32, mchbar_write32(), MRC_REVISION, normalize_training(), PM_THML_STAT, prepare_training(), printk, printram, read_mpr_training(), receive_enable_calibration(), restore_timings(), SCHED_CBIT, set_read_write_timings(), set_wmm_behavior(), udelay(), and write_training().

Referenced by init_dram_ddr3().

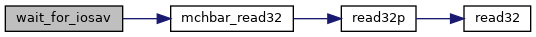

| void wait_for_iosav | ( | int | channel | ) |

Definition at line 37 of file raminit_iosav.c.

References IOSAV_STATUS_ch, and mchbar_read32().

Referenced by channel_scrub(), channel_test(), dram_mrscommands(), find_agrsv_read_margin(), find_predefined_pattern(), find_read_mpr_margin(), get_power_down_mode(), iosav_run_once_and_wait(), jedec_write_leveling(), prepare_training(), receive_enable_calibration(), restore_timings(), test_aggressive_write(), test_command_training(), test_rcven(), test_tx_dq(), train_write_flyby(), tx_dq_write_leveling(), write_level_rank(), and write_reset().

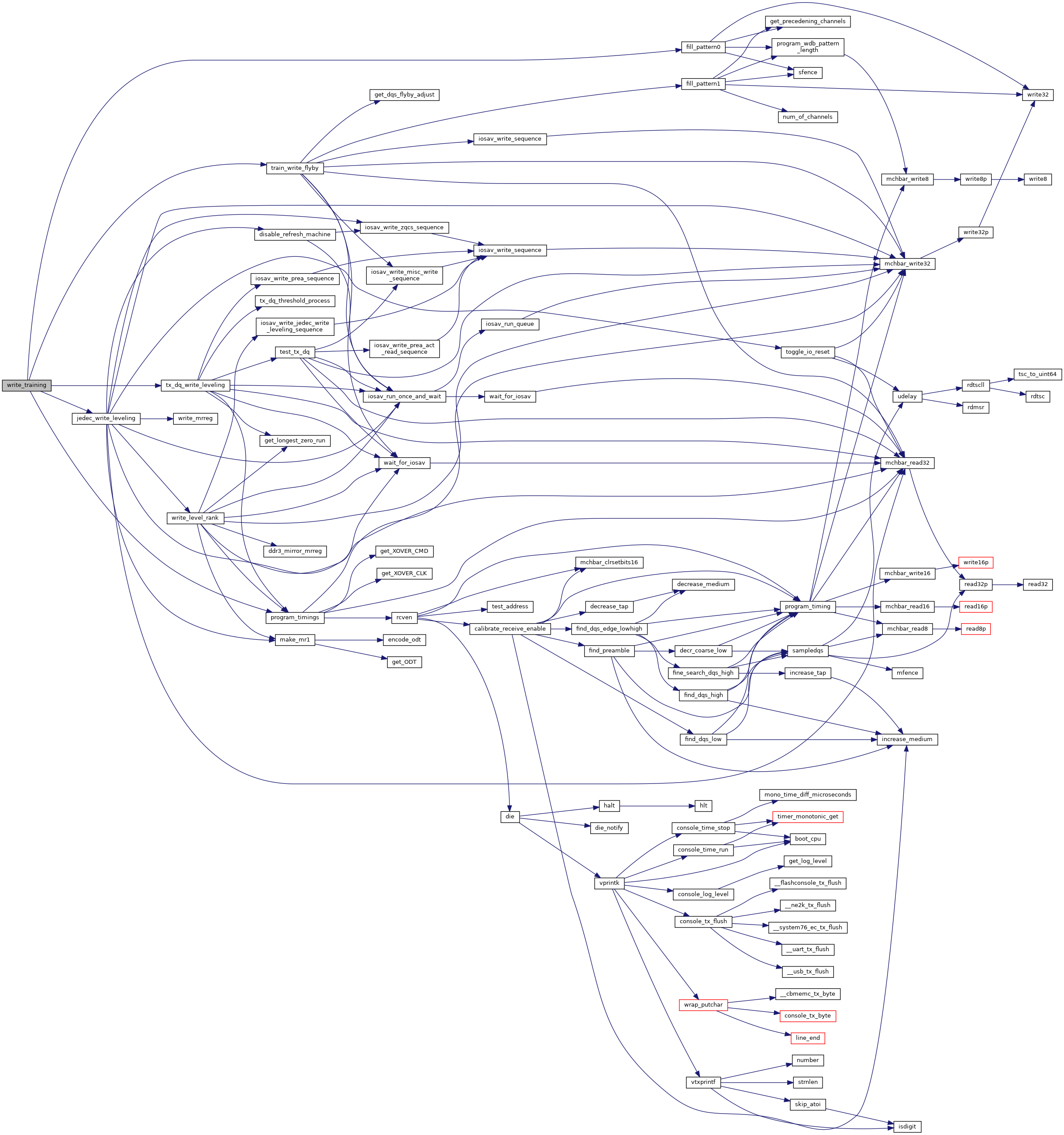

| int write_training | ( | ramctr_timing * | ctrl | ) |

Definition at line 1844 of file raminit_common.c.

References fill_pattern0(), FOR_ALL_CHANNELS, FOR_ALL_POPULATED_CHANNELS, FOR_ALL_POPULATED_RANKS, jedec_write_leveling(), mchbar_setbits32, printram, program_timings(), TC_RWP_ch, train_write_flyby(), and tx_dq_write_leveling().

Referenced by try_init_dram_ddr3().