|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

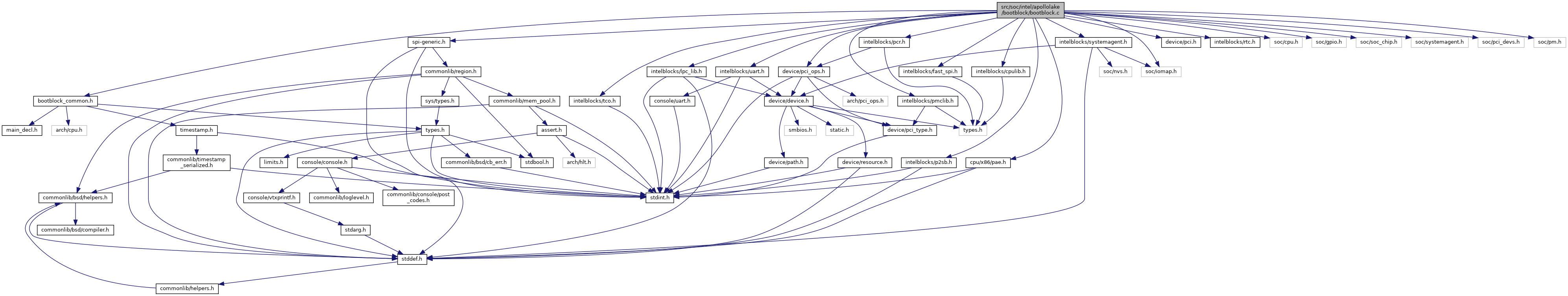

#include <bootblock_common.h>#include <cpu/x86/pae.h>#include <device/pci.h>#include <device/pci_ops.h>#include <intelblocks/cpulib.h>#include <intelblocks/fast_spi.h>#include <intelblocks/lpc_lib.h>#include <intelblocks/p2sb.h>#include <intelblocks/pcr.h>#include <intelblocks/rtc.h>#include <intelblocks/systemagent.h>#include <intelblocks/pmclib.h>#include <intelblocks/tco.h>#include <intelblocks/uart.h>#include <soc/iomap.h>#include <soc/cpu.h>#include <soc/gpio.h>#include <soc/soc_chip.h>#include <soc/systemagent.h>#include <soc/pci_devs.h>#include <soc/pm.h>#include <spi-generic.h>

Go to the source code of this file.

Functions | |

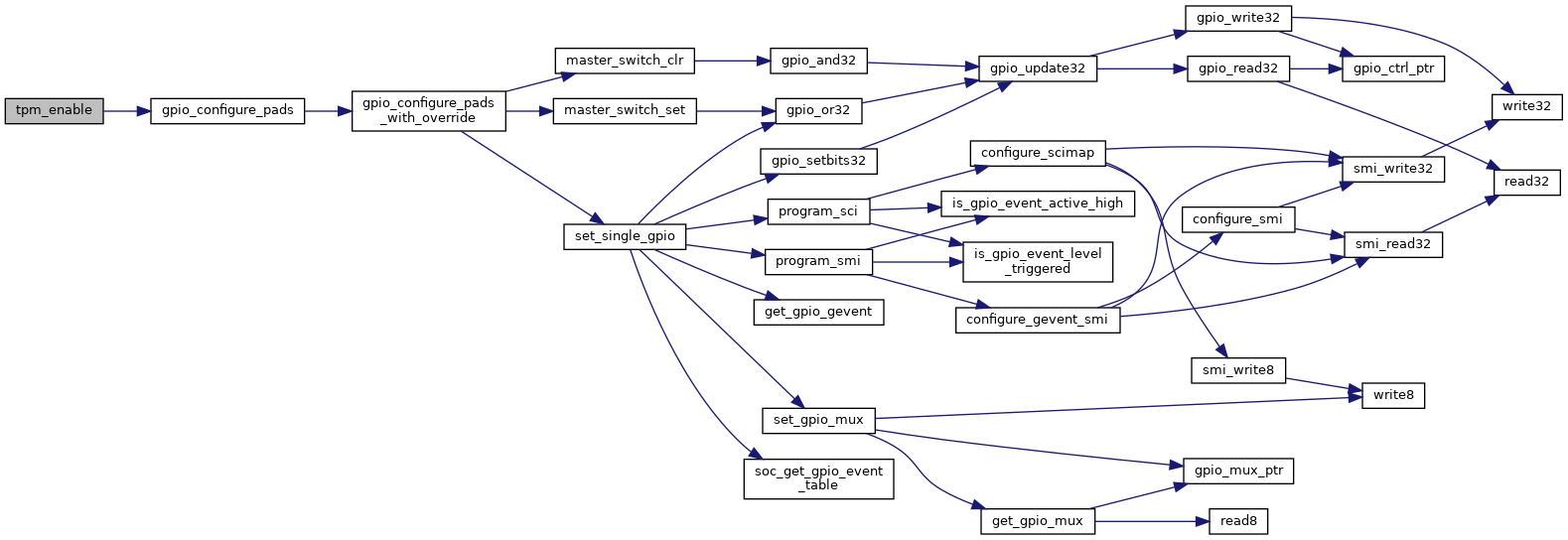

| static void | tpm_enable (void) |

| asmlinkage void | bootblock_c_entry (uint64_t base_timestamp) |

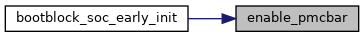

| static void | enable_pmcbar (void) |

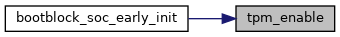

| void | bootblock_soc_early_init (void) |

Variables | |

| static const struct pad_config | tpm_spi_configs [] |

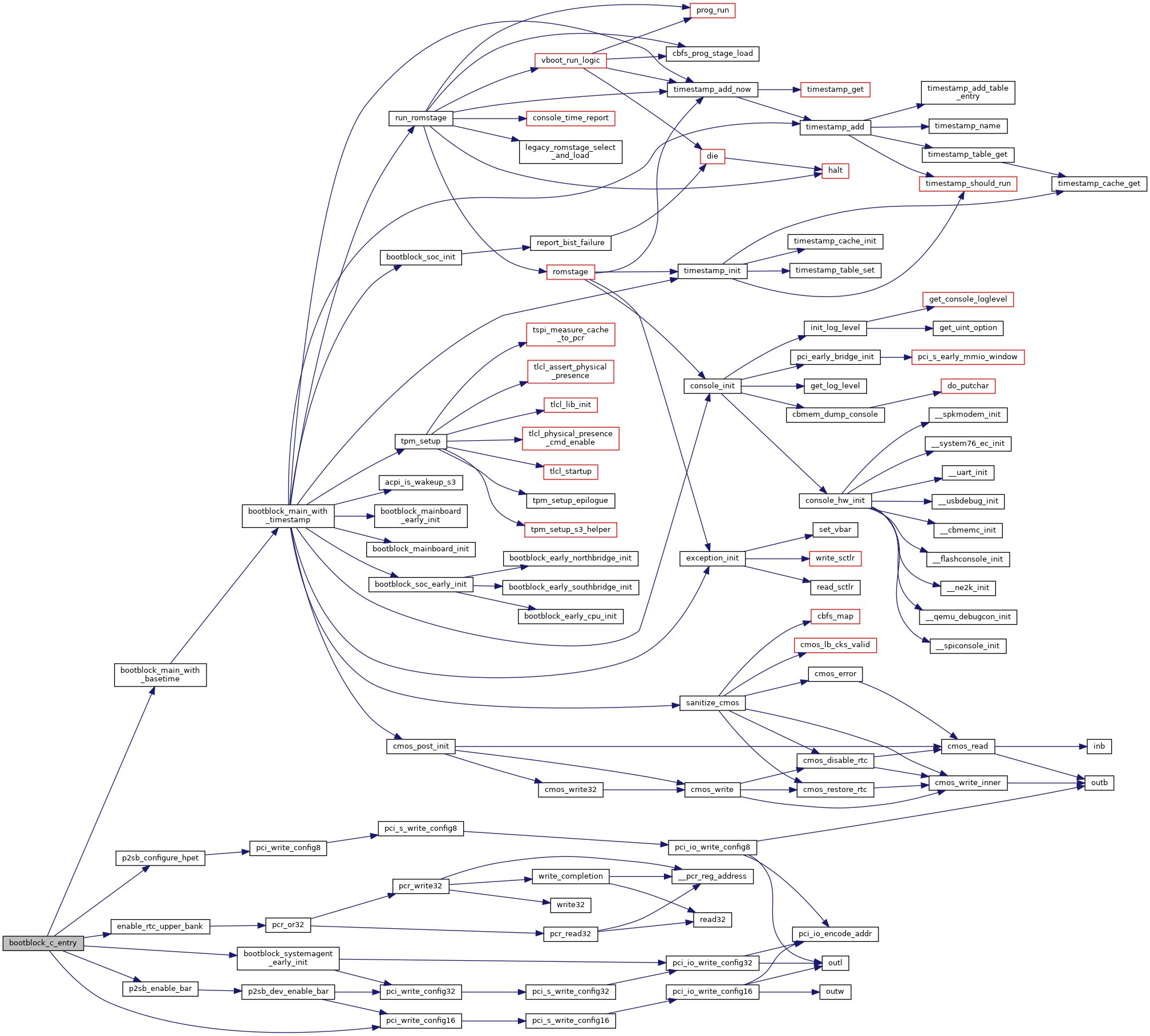

| asmlinkage void bootblock_c_entry | ( | uint64_t | base_timestamp | ) |

Definition at line 40 of file bootblock.c.

References ACPI_BASE_ADDRESS, bootblock_main_with_basetime(), bootblock_systemagent_early_init(), enable_rtc_upper_bank(), p2sb_configure_hpet(), p2sb_enable_bar(), PCH_DEV_PMC, PCI_BASE_ADDRESS_4, PCI_COMMAND, PCI_COMMAND_IO, PCI_COMMAND_MASTER, and pci_write_config16().

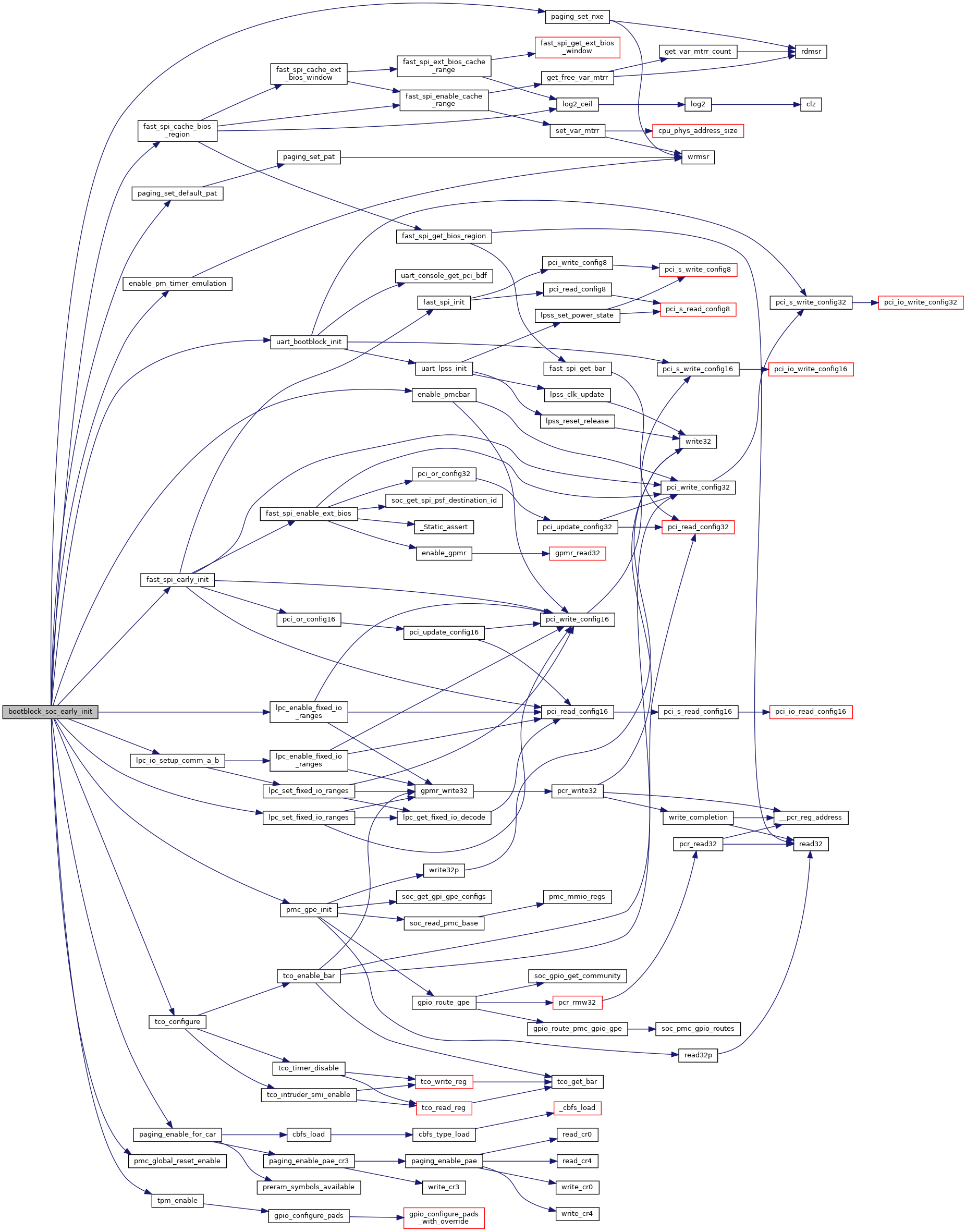

Definition at line 76 of file bootblock.c.

References config, CONFIG, config_of_soc, enable_pm_timer_emulation(), enable_pmcbar(), fast_spi_cache_bios_region(), fast_spi_early_init(), lpc_enable_fixed_io_ranges(), lpc_io_setup_comm_a_b(), LPC_IOE_EC_62_66, LPC_IOE_KBC_60_64, LPC_IOE_SUPERIO_2E_2F, lpc_set_fixed_io_ranges(), paging_enable_for_car(), paging_set_default_pat(), paging_set_nxe(), pmc_global_reset_enable(), pmc_gpe_init(), SPI_BASE_ADDRESS, tco_configure(), tpm_enable(), and uart_bootblock_init().

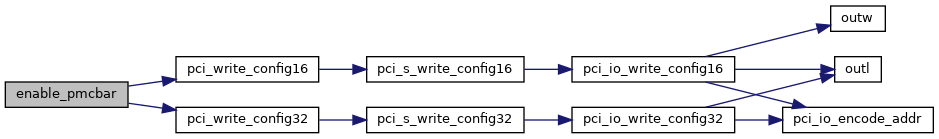

Definition at line 61 of file bootblock.c.

References ACPI_BASE_ADDRESS, PCH_DEV_PMC, PCH_PWRM_BASE_ADDRESS, PCI_BASE_ADDRESS_0, PCI_BASE_ADDRESS_1, PCI_BASE_ADDRESS_2, PCI_BASE_ADDRESS_3, PCI_BASE_ADDRESS_4, PCI_COMMAND, PCI_COMMAND_IO, PCI_COMMAND_MASTER, PCI_COMMAND_MEMORY, pci_write_config16(), pci_write_config32(), pmc, and PMC_BAR1.

Referenced by bootblock_soc_early_init().

Definition at line 34 of file bootblock.c.

References ARRAY_SIZE, gpio_configure_pads(), and tpm_spi_configs.

Referenced by bootblock_soc_early_init().

|

static |

Definition at line 1 of file bootblock.c.

Referenced by tpm_enable().