|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

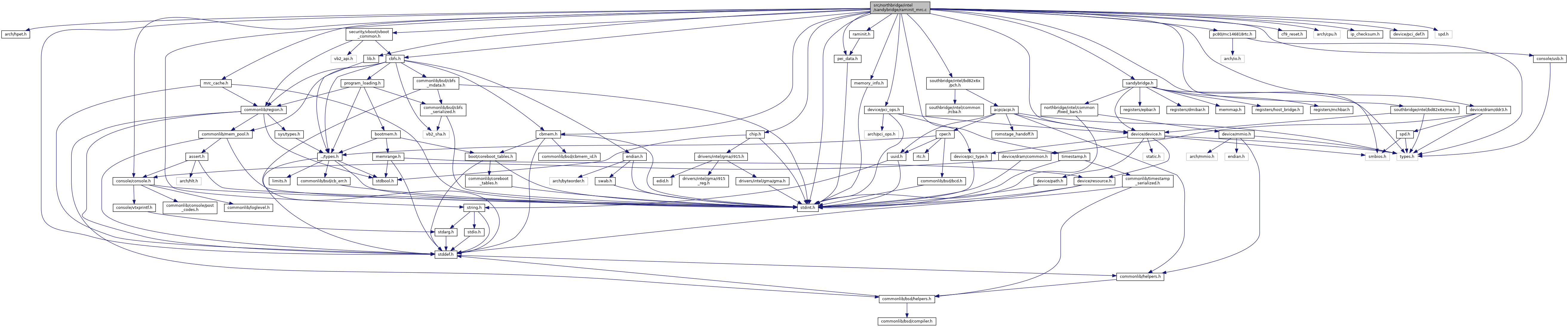

#include <arch/hpet.h>#include <console/console.h>#include <console/usb.h>#include <cf9_reset.h>#include <string.h>#include <device/device.h>#include <device/dram/ddr3.h>#include <device/pci_ops.h>#include <arch/cpu.h>#include <cbmem.h>#include <cbfs.h>#include <ip_checksum.h>#include <pc80/mc146818rtc.h>#include <device/pci_def.h>#include <lib.h>#include <mrc_cache.h>#include <spd.h>#include <smbios.h>#include <stddef.h>#include <stdint.h>#include <timestamp.h>#include "raminit.h"#include "pei_data.h"#include "sandybridge.h"#include "chip.h"#include <security/vboot/vboot_common.h>#include <southbridge/intel/bd82x6x/pch.h>#include <memory_info.h>#include <southbridge/intel/bd82x6x/me.h>

Go to the source code of this file.

Data Structures | |

| struct | mrc_var_data |

Macros | |

| #define | CMOS_OFFSET_MRC_SEED 152 |

| #define | CMOS_OFFSET_MRC_SEED_S3 156 |

| #define | CMOS_OFFSET_MRC_SEED_CHK 160 |

| #define | MRC_CACHE_VERSION 0 |

| #define | DCACHE_RAM_MRC_VAR_BASE |

Functions | |

| static void | save_mrc_data (struct pei_data *pei_data) |

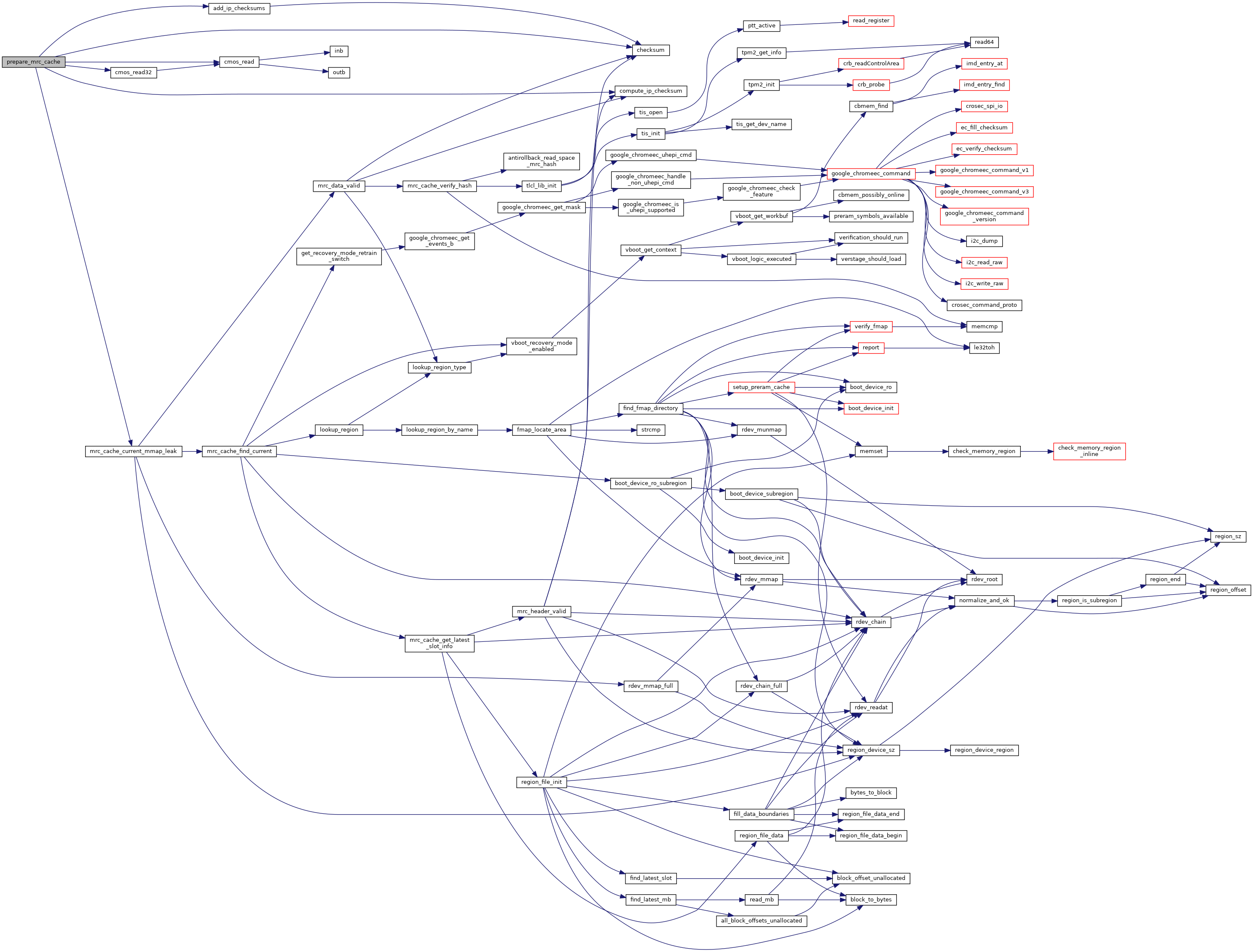

| static void | prepare_mrc_cache (struct pei_data *pei_data) |

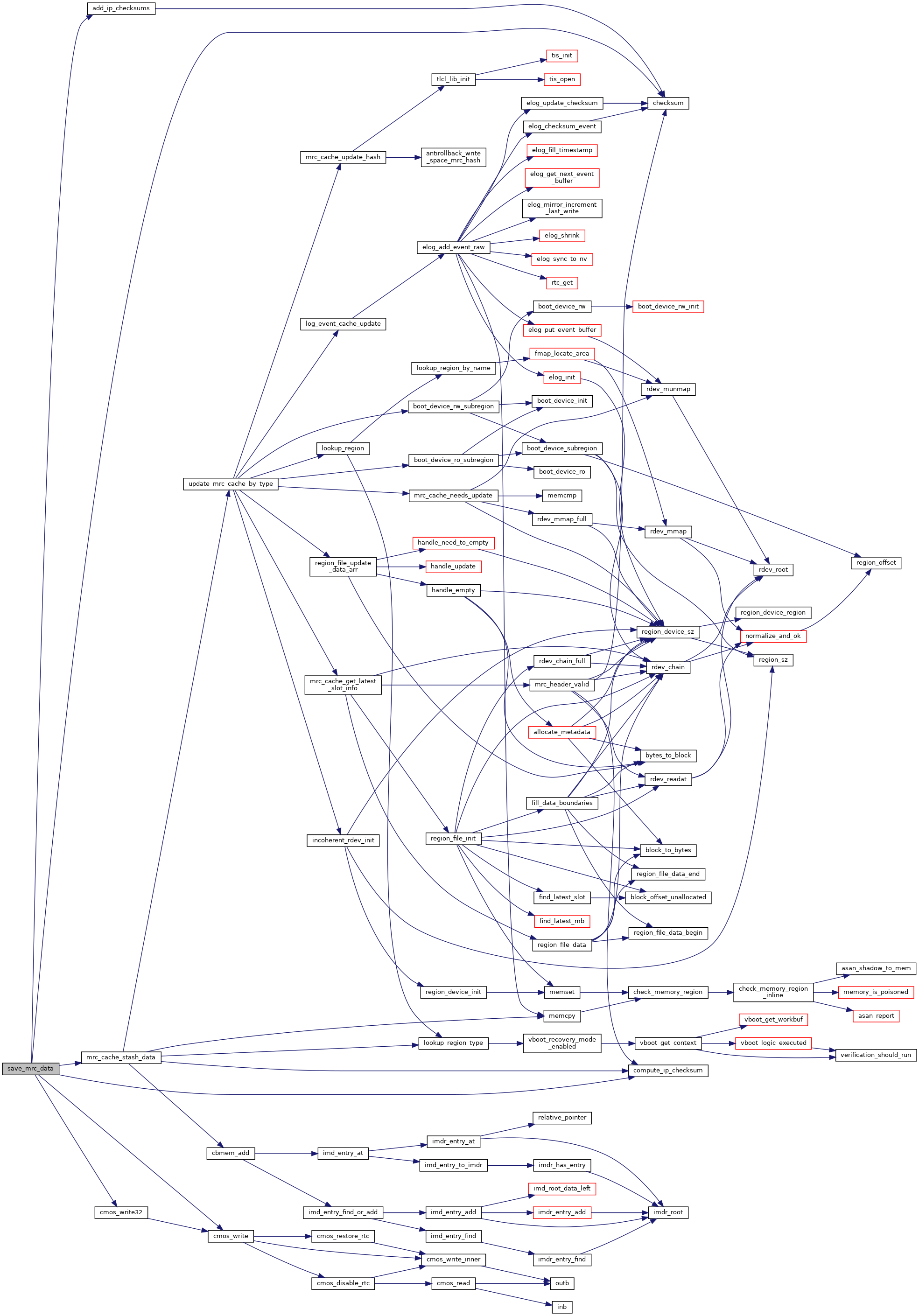

| static void | sdram_initialize (struct pei_data *pei_data) |

| Find PEI executable in coreboot filesystem and execute it. More... | |

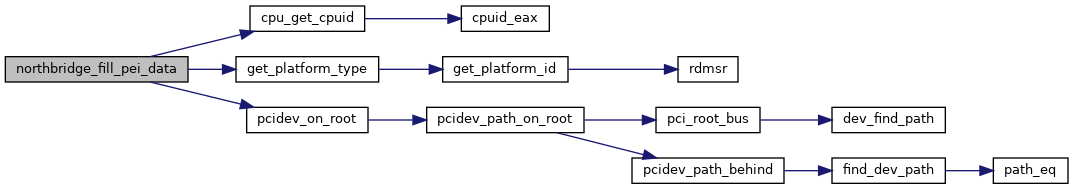

| static void | northbridge_fill_pei_data (struct pei_data *pei_data) |

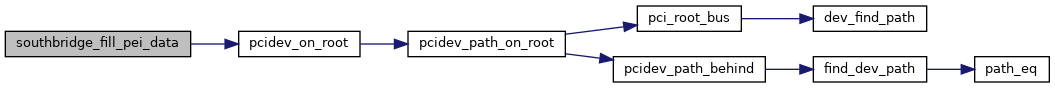

| static void | southbridge_fill_pei_data (struct pei_data *pei_data) |

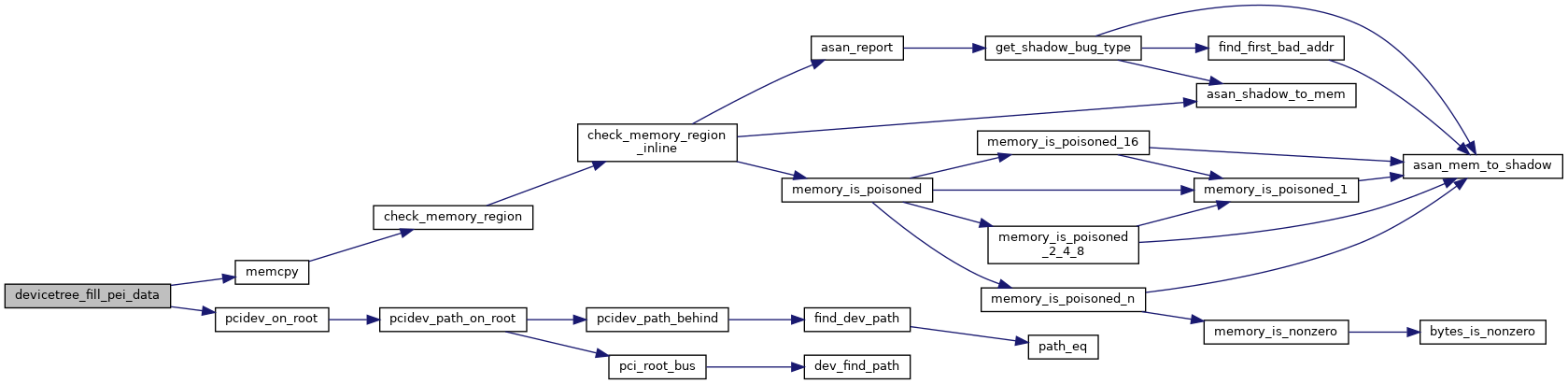

| static void | devicetree_fill_pei_data (struct pei_data *pei_data) |

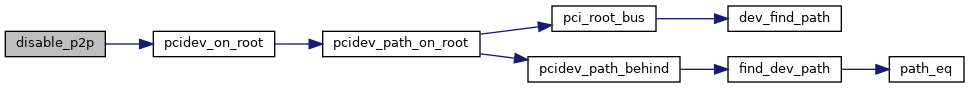

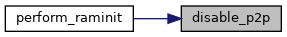

| static void | disable_p2p (void) |

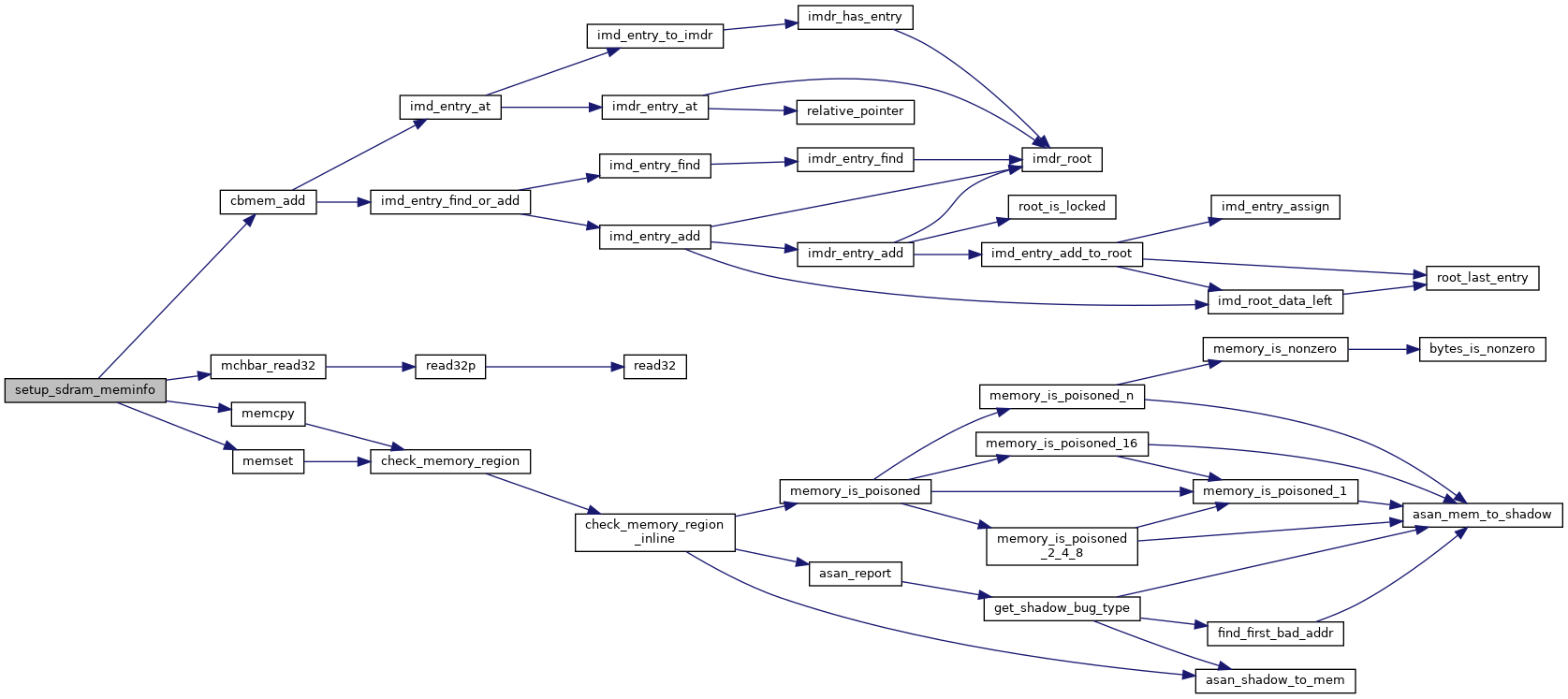

| static void | setup_sdram_meminfo (struct pei_data *pei_data) |

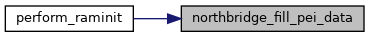

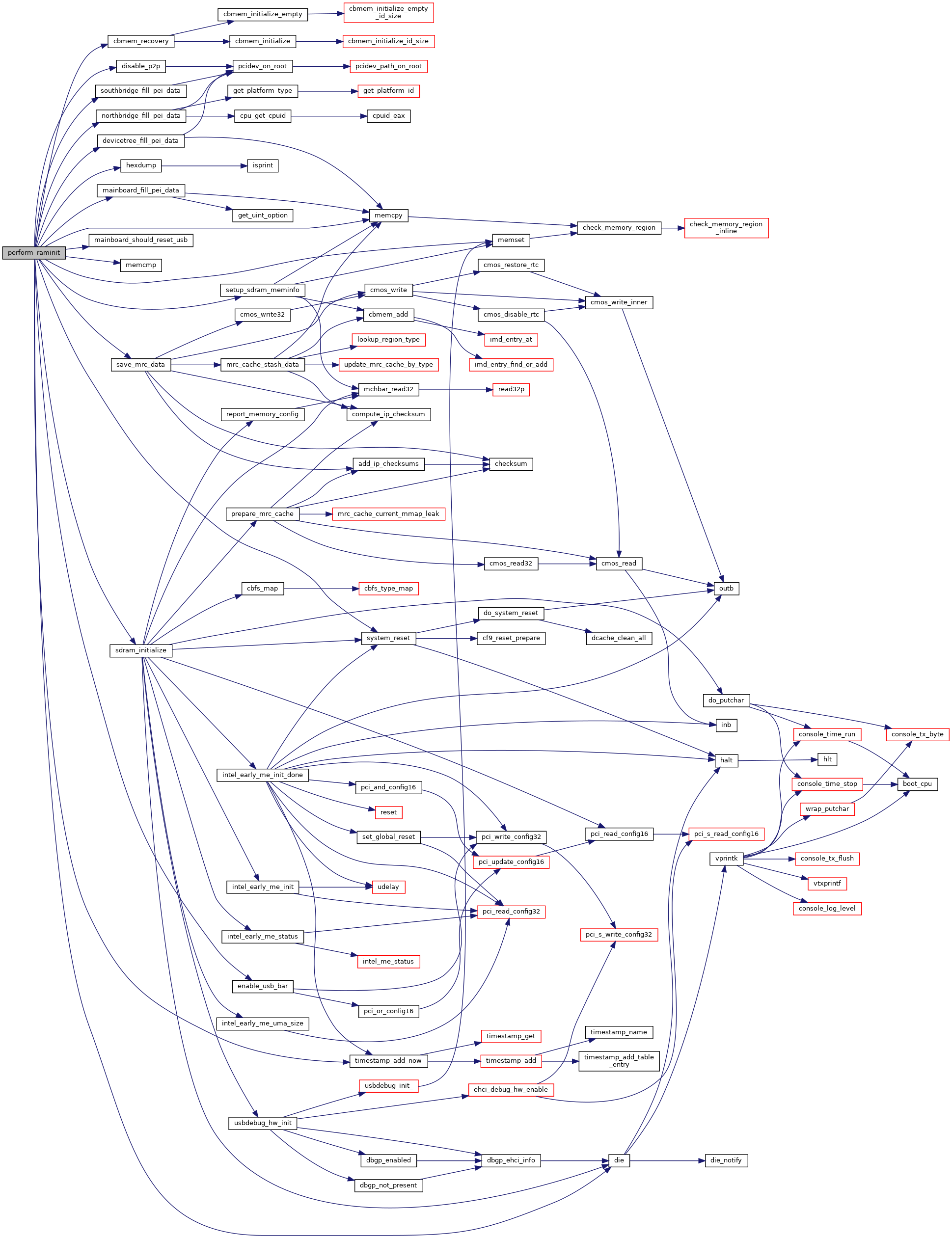

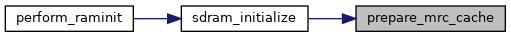

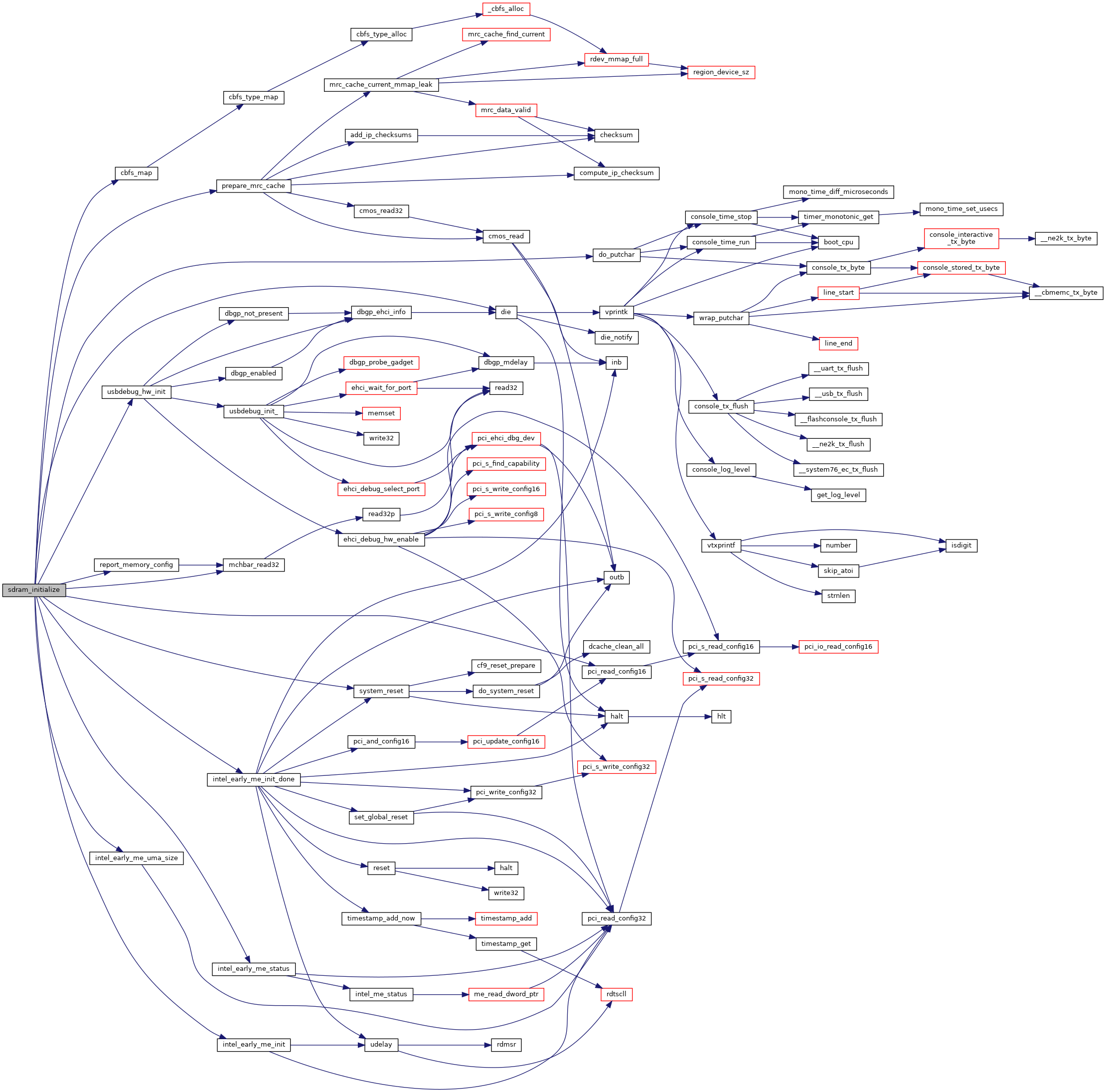

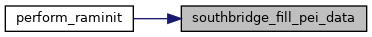

| void | perform_raminit (int s3resume) |

Variables | |

| struct mrc_var_data | __packed |

| #define CMOS_OFFSET_MRC_SEED 152 |

Definition at line 45 of file raminit_mrc.c.

| #define CMOS_OFFSET_MRC_SEED_CHK 160 |

Definition at line 47 of file raminit_mrc.c.

| #define CMOS_OFFSET_MRC_SEED_S3 156 |

Definition at line 46 of file raminit_mrc.c.

| #define DCACHE_RAM_MRC_VAR_BASE |

Definition at line 222 of file raminit_mrc.c.

| #define MRC_CACHE_VERSION 0 |

Definition at line 50 of file raminit_mrc.c.

Definition at line 265 of file raminit_mrc.c.

References __fallthrough, BIOS_WARNING, device::chip_info, northbridge_intel_sandybridge_config::ddr3lv_support, pei_data::ddr3lv_support, northbridge_intel_sandybridge_config::ddr_refresh_rate_config, pei_data::ddr_refresh_rate_config, pei_data::ec_present, northbridge_intel_sandybridge_config::ec_present, northbridge_intel_sandybridge_config::hs_port_switch_mask, pch_usb3_controller_settings::hs_port_switch_mask, pei_data::max_ddr3_freq, northbridge_intel_sandybridge_config::max_mem_clock_mhz, memcpy(), northbridge_intel_sandybridge_config::mode, pch_usb3_controller_settings::mode, northbridge_intel_sandybridge_config::nmode, pei_data::nmode, pcidev_on_root(), northbridge_intel_sandybridge_config::preboot_support, pch_usb3_controller_settings::preboot_support, printk, pei_data::spd_addresses, northbridge_intel_sandybridge_config::spd_addresses, northbridge_intel_sandybridge_config::ts_addresses, pei_data::ts_addresses, northbridge_intel_sandybridge_config::usb3, pei_data::usb3, northbridge_intel_sandybridge_config::usb_port_config, pei_data::usb_port_config, northbridge_intel_sandybridge_config::xhci_streams, and pch_usb3_controller_settings::xhci_streams.

Referenced by perform_raminit().

Definition at line 313 of file raminit_mrc.c.

References device::enabled, FD, PCH_DISABLE_P2P, pcidev_on_root(), and RCBA32.

Referenced by perform_raminit().

Definition at line 233 of file raminit_mrc.c.

References cpu_get_cpuid(), pei_data::dmibar, device::enabled, pei_data::epbar, get_platform_type(), pei_data::hpet_address, HPET_BASE_ADDRESS, pei_data::mchbar, pcidev_on_root(), pei_data::pcie_init, pei_data::pciexbar, PLATFORM_MOBILE, pei_data::system_type, pei_data::thermalbase, and pei_data::tseg_size.

Referenced by perform_raminit().

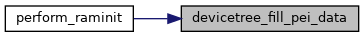

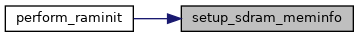

| void perform_raminit | ( | int | s3resume | ) |

Definition at line 325 of file raminit_mrc.c.

References ARRAY_SIZE, BIOS_DEBUG, BIOS_ERR, pei_data::boot_mode, cbmem_recovery(), DCACHE_RAM_MRC_VAR_BASE, devicetree_fill_pei_data(), die(), pei_data::dimm_channel0_disabled, pei_data::dimm_channel1_disabled, disable_p2p(), enable_usb_bar(), hexdump(), mainboard_fill_pei_data(), mainboard_should_reset_usb(), memcmp(), memcpy(), memset(), northbridge_fill_pei_data(), PEI_VERSION, pei_data::pei_version, mrc_var_data::pool_base, mrc_var_data::pool_used, post_code, printk, save_mrc_data(), sdram_initialize(), setup_sdram_meminfo(), southbridge_fill_pei_data(), pei_data::spd_addresses, pei_data::spd_data, system_reset(), timestamp_add_now(), TS_INITRAM_END, TS_INITRAM_START, pei_data::tx_byte, and mrc_var_data::tx_byte.

Definition at line 78 of file raminit_mrc.c.

References add_ip_checksums(), BIOS_DEBUG, BIOS_ERR, checksum(), CMOS_OFFSET_MRC_SEED, CMOS_OFFSET_MRC_SEED_CHK, CMOS_OFFSET_MRC_SEED_S3, cmos_read(), cmos_read32(), compute_ip_checksum(), mrc_cache_current_mmap_leak(), MRC_CACHE_VERSION, pei_data::mrc_input, pei_data::mrc_input_len, MRC_TRAINING_DATA, NULL, printk, pei_data::scrambler_seed, and pei_data::scrambler_seed_s3.

Referenced by sdram_initialize().

Definition at line 52 of file raminit_mrc.c.

References add_ip_checksums(), BIOS_DEBUG, checksum(), CMOS_OFFSET_MRC_SEED, CMOS_OFFSET_MRC_SEED_CHK, CMOS_OFFSET_MRC_SEED_S3, cmos_write(), cmos_write32(), compute_ip_checksum(), mrc_cache_stash_data(), MRC_CACHE_VERSION, pei_data::mrc_output, pei_data::mrc_output_len, MRC_TRAINING_DATA, printk, pei_data::scrambler_seed, and pei_data::scrambler_seed_s3.

Referenced by perform_raminit().

Find PEI executable in coreboot filesystem and execute it.

| pei_data | configuration data for UEFI PEI reference code |

Definition at line 130 of file raminit_mrc.c.

References BASE_REV_MASK, BASE_REV_SNB, BIOS_DEBUG, BIOS_ERR, pei_data::boot_mode, cbfs_map(), CONFIG, die(), die_with_post_code, do_putchar(), intel_early_me_init(), intel_early_me_init_done(), intel_early_me_status(), intel_early_me_uma_size(), mchbar_read32(), ME_INIT_STATUS_SUCCESS, pei_data::mrc_input, MRC_REVISION, NULL, PCI_CPU_DEVICE, PCI_DEVICE_ID, pci_read_config16(), POST_INVALID_VENDOR_BINARY, prepare_mrc_cache(), printk, report_memory_config(), system_reset(), pei_data::tx_byte, usbdebug_hw_init(), and version.

Referenced by perform_raminit().

Definition at line 395 of file raminit_mrc.c.

References ARRAY_SIZE, dimm_info::bank_locator, dimm_info::bus_width, cbmem_add(), CBMEM_ID_MEMINFO, dimm_info::channel_num, DDR3_SPD_SODIMM, dimm_info::ddr_frequency, dimm_info::ddr_type, memory_info::dimm, memory_info::dimm_cnt, dimm_info::dimm_num, dimm_info::dimm_size, MAD_CHNL, MAD_DIMM_CH0, MAD_DIMM_CH1, MC_BIOS_DATA, MC_BIOS_REQ, mchbar_read32(), memcpy(), MEMORY_BUS_WIDTH_64, MEMORY_TYPE_DDR3, memset(), dimm_info::mod_id, dimm_info::mod_type, dimm_info::module_part_number, dimm_info::rank_per_dimm, dimm_info::serial, pei_data::spd_data, SPD_DIMM_MOD_ID1, SPD_DIMM_MOD_ID2, SPD_DIMM_PART_LEN, SPD_DIMM_PART_NUM, SPD_DIMM_SERIAL_LEN, and SPD_DIMM_SERIAL_NUM.

Referenced by perform_raminit().

Definition at line 252 of file raminit_mrc.c.

References DEFAULT_GPIOBASE, DEFAULT_PMBASE, DEFAULT_RCBA, device::enabled, pei_data::gbe_enable, pei_data::gpiobase, pcidev_on_root(), pei_data::pmbase, pei_data::rcba, pei_data::smbusbar, pei_data::wdbbar, and pei_data::wdbsize.

Referenced by perform_raminit().

| struct mrc_var_data __packed |