|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

Go to the source code of this file.

Data Structures | |

| struct | aoac_devs |

Typedefs | |

| typedef struct aoac_devs | aoac_devs_t |

Functions | |

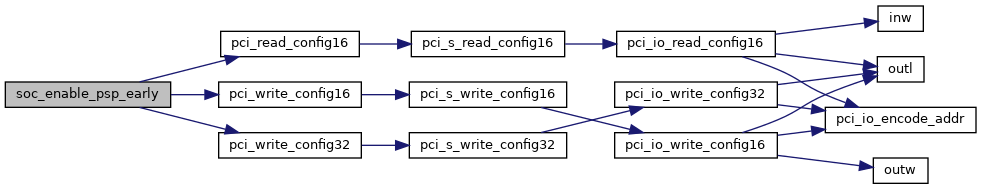

| void | soc_enable_psp_early (void) |

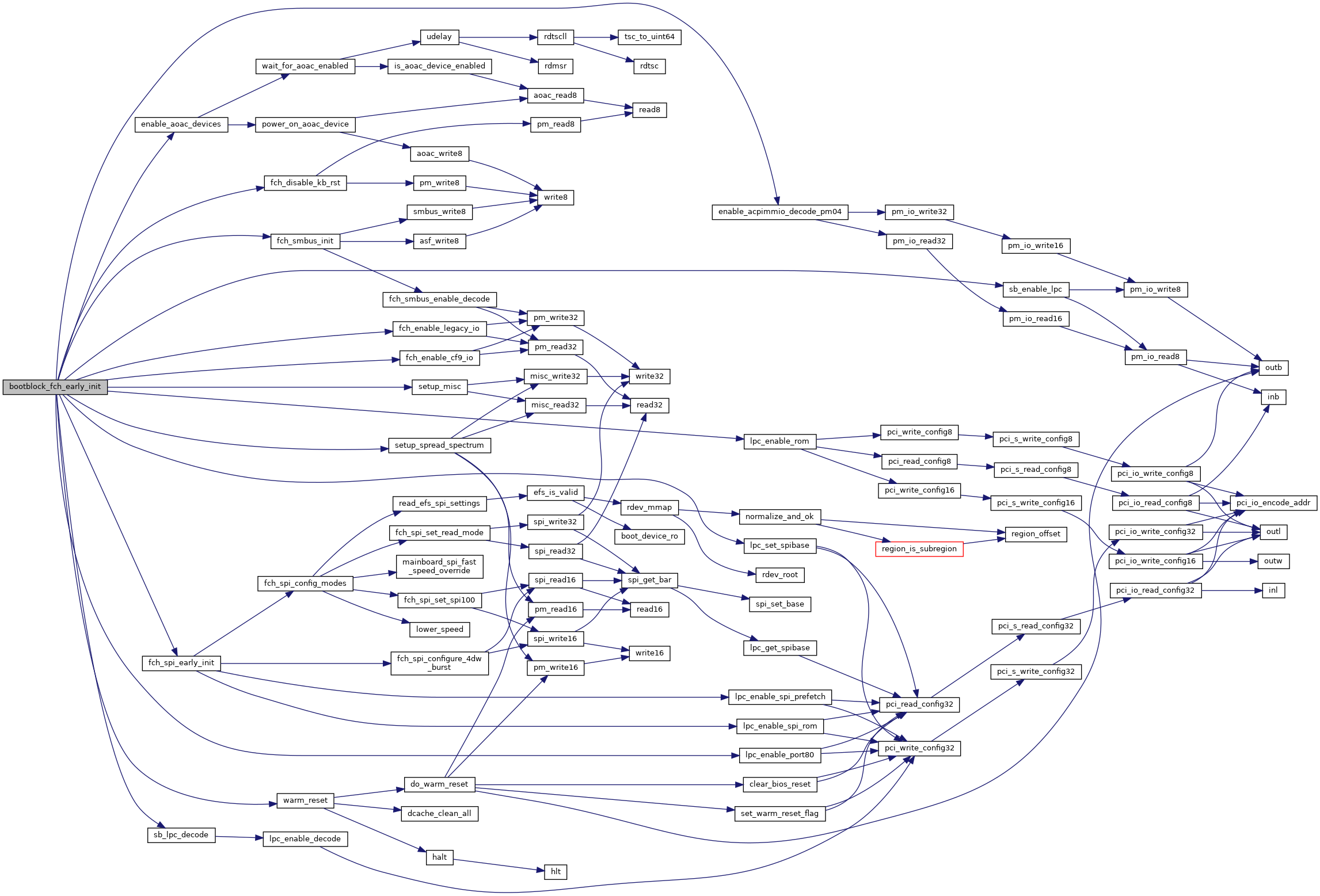

| void | bootblock_fch_early_init (void) |

| void | bootblock_fch_init (void) |

| void | fch_init (void *chip_info) |

| void | fch_final (void *chip_info) |

| void | enable_aoac_devices (void) |

| void | fch_clk_output_48Mhz (u32 osc) |

| int | mainboard_get_xhci_oc_map (uint16_t *usb_oc_map) |

| int | mainboard_get_ehci_oc_map (uint16_t *usb_oc_map) |

Definition at line 150 of file southbridge.h.

| #define BM_STS BIT(4) |

Definition at line 42 of file southbridge.h.

| #define CG1PLL_FBDIV_MASK (0xfff << CG1PLL_FBDIV_SHIFT) |

Definition at line 91 of file southbridge.h.

| #define CG1PLL_FBDIV_SHIFT 10 |

Definition at line 90 of file southbridge.h.

| #define CG1PLL_FBDIV_TEST BIT(26) |

Definition at line 104 of file southbridge.h.

| #define CG1PLL_LF_MODE_MASK (0x1ff << CG1PLL_LF_MODE_SHIFT) |

Definition at line 102 of file southbridge.h.

| #define CG1PLL_LF_MODE_SHIFT 9 |

Definition at line 101 of file southbridge.h.

| #define CG1PLL_REFDIV_MASK (0x3ff << CG1PLL_REFDIV_SHIFT) |

Definition at line 89 of file southbridge.h.

| #define CG1PLL_REFDIV_SHIFT 0 |

Definition at line 88 of file southbridge.h.

| #define CG1PLL_SPREAD_SPECTRUM_ENABLE BIT(0) |

Definition at line 86 of file southbridge.h.

| #define DEBUG_PORT_ENABLE BIT(18) |

Definition at line 130 of file southbridge.h.

Definition at line 131 of file southbridge.h.

| #define DEBUG_PORT_SELECT_SHIFT 16 |

Definition at line 129 of file southbridge.h.

| #define EHCI_HUB_CONFIG4 0x90 |

Definition at line 128 of file southbridge.h.

| #define EHCI_OVER_CURRENT_CONTROL 0x70 |

Definition at line 127 of file southbridge.h.

| #define FORCE_SLPSTATE_RETRY BIT(25) |

Definition at line 18 of file southbridge.h.

| #define FORCE_STPCLK_RETRY BIT(24) |

Definition at line 19 of file southbridge.h.

| #define GBL_EN BIT(5) |

Definition at line 47 of file southbridge.h.

| #define GBL_STS BIT(5) |

Definition at line 41 of file southbridge.h.

| #define GPE0_LIMIT 28 |

Definition at line 134 of file southbridge.h.

| #define GPP_CLK0_REQ_MAP_CLK_REQ0 1 |

Definition at line 84 of file southbridge.h.

| #define GPP_CLK0_REQ_MAP_MASK (0xf << GPP_CLK0_REQ_MAP_SHIFT) |

Definition at line 83 of file southbridge.h.

| #define GPP_CLK0_REQ_MAP_SHIFT 0 |

Definition at line 82 of file southbridge.h.

| #define GPP_CLK2_REQ_MAP_CLK_REQ2 3 |

Definition at line 81 of file southbridge.h.

| #define GPP_CLK2_REQ_MAP_MASK (0xf << GPP_CLK2_REQ_MAP_SHIFT) |

Definition at line 80 of file southbridge.h.

| #define GPP_CLK2_REQ_MAP_SHIFT 8 |

Definition at line 79 of file southbridge.h.

| #define GPP_CLK_CNTRL 0x00 |

Definition at line 78 of file southbridge.h.

| #define MISC_CGPLL_CONFIG1 0x08 |

Definition at line 85 of file southbridge.h.

| #define MISC_CGPLL_CONFIG3 0x10 |

Definition at line 87 of file southbridge.h.

| #define MISC_CGPLL_CONFIG4 0x14 |

Definition at line 92 of file southbridge.h.

| #define MISC_CGPLL_CONFIG5 0x18 |

Definition at line 97 of file southbridge.h.

| #define MISC_CGPLL_CONFIG6 0x1c |

Definition at line 100 of file southbridge.h.

| #define MISC_CLK_CNTL1 0x40 |

Definition at line 103 of file southbridge.h.

| #define OC_PORT0_SHIFT 0 |

Definition at line 122 of file southbridge.h.

| #define OC_PORT1_SHIFT 4 |

Definition at line 123 of file southbridge.h.

| #define OC_PORT2_SHIFT 8 |

Definition at line 124 of file southbridge.h.

| #define OC_PORT3_SHIFT 12 |

Definition at line 125 of file southbridge.h.

| #define OSCOUT1_CLK_OUTPUT_ENB BIT(2) /* 0 = Enabled, 1 = Disabled */ |

Definition at line 105 of file southbridge.h.

| #define OSCOUT2_CLK_OUTPUT_ENB BIT(7) /* 0 = Enabled, 1 = Disabled */ |

Definition at line 106 of file southbridge.h.

| #define PCIEXPWAK_DIS BIT(14) /*AcpiPmEvtBlkx02 Pm1Enable */ |

Definition at line 44 of file southbridge.h.

| #define PCIEXPWAK_STS BIT(14) |

Definition at line 38 of file southbridge.h.

| #define PM1_CNT_BLK 0x62 |

Definition at line 49 of file southbridge.h.

| #define PM1_LIMIT 16 |

Definition at line 133 of file southbridge.h.

| #define PM_ACPI_BIOS_RLS BIT(7) |

Definition at line 60 of file southbridge.h.

| #define PM_ACPI_BLOCK_PCIE_PME BIT(24) |

Definition at line 63 of file southbridge.h.

| #define PM_ACPI_CONF 0x74 |

Definition at line 54 of file southbridge.h.

| #define PM_ACPI_DECODE_STD BIT(0) |

Definition at line 55 of file southbridge.h.

| #define PM_ACPI_GLOBAL_EN BIT(1) |

Definition at line 56 of file southbridge.h.

| #define PM_ACPI_MASK_ARB_DIS BIT(6) |

Definition at line 59 of file southbridge.h.

| #define PM_ACPI_NB_PME_GEVENT BIT(28) |

Definition at line 66 of file southbridge.h.

| #define PM_ACPI_PCIE_WAK_MASK BIT(25) |

Definition at line 64 of file southbridge.h.

| #define PM_ACPI_PWRBTNEN_EN BIT(8) |

Definition at line 61 of file southbridge.h.

| #define PM_ACPI_REDUCED_HW_EN BIT(9) |

Definition at line 62 of file southbridge.h.

| #define PM_ACPI_RTC_EN_EN BIT(2) |

Definition at line 57 of file southbridge.h.

| #define PM_ACPI_RTC_WAKE_EN BIT(29) |

Definition at line 67 of file southbridge.h.

| #define PM_ACPI_SMI_CMD 0x6a |

Definition at line 53 of file southbridge.h.

| #define PM_ACPI_TIMER_EN_EN BIT(4) |

Definition at line 58 of file southbridge.h.

| #define PM_ACPI_WAKE_AS_GEVENT BIT(27) |

Definition at line 65 of file southbridge.h.

| #define PM_CPU_CTRL 0x66 |

Definition at line 51 of file southbridge.h.

| #define PM_EVT_BLK 0x60 |

Definition at line 36 of file southbridge.h.

| #define PM_GENINT_DISABLE BIT(0) |

Definition at line 69 of file southbridge.h.

| #define PM_GPE0_BLK 0x68 |

Definition at line 52 of file southbridge.h.

| #define PM_LPC_A20_EN BIT(1) |

Definition at line 72 of file southbridge.h.

| #define PM_LPC_AB_NO_BYPASS_EN BIT(2) |

Definition at line 71 of file southbridge.h.

| #define PM_LPC_ENABLE BIT(0) |

Definition at line 73 of file southbridge.h.

| #define PM_LPC_GATING 0xec |

Definition at line 70 of file southbridge.h.

| #define PM_PCI_CTRL 0x08 |

Definition at line 17 of file southbridge.h.

| #define PM_PCIB_CFG 0xea |

Definition at line 68 of file southbridge.h.

| #define PM_SERIRQ_CONF 0x54 |

Definition at line 24 of file southbridge.h.

| #define PM_SERIRQ_ENABLE BIT(7) |

Definition at line 34 of file southbridge.h.

| #define PM_SERIRQ_MODE BIT(6) |

Definition at line 33 of file southbridge.h.

| #define PM_SERIRQ_NUM_BITS_17 0x0000 |

Definition at line 25 of file southbridge.h.

| #define PM_SERIRQ_NUM_BITS_18 0x0004 |

Definition at line 26 of file southbridge.h.

| #define PM_SERIRQ_NUM_BITS_19 0x0008 |

Definition at line 27 of file southbridge.h.

| #define PM_SERIRQ_NUM_BITS_20 0x000c |

Definition at line 28 of file southbridge.h.

| #define PM_SERIRQ_NUM_BITS_21 0x0010 |

Definition at line 29 of file southbridge.h.

| #define PM_SERIRQ_NUM_BITS_22 0x0014 |

Definition at line 30 of file southbridge.h.

| #define PM_SERIRQ_NUM_BITS_23 0x0018 |

Definition at line 31 of file southbridge.h.

| #define PM_SERIRQ_NUM_BITS_24 0x001c |

Definition at line 32 of file southbridge.h.

| #define PM_TMR_BLK 0x64 |

Definition at line 50 of file southbridge.h.

| #define PM_USB_ALL_CONTROLLERS 0x7f |

Definition at line 75 of file southbridge.h.

| #define PM_USB_ENABLE 0xef |

Definition at line 74 of file southbridge.h.

| #define PSP_BAR_ENABLES 0x48 |

Definition at line 149 of file southbridge.h.

| #define PSP_MAILBOX_BAR PCI_BASE_ADDRESS_4 /* BKDG: "BAR3" */ |

Definition at line 147 of file southbridge.h.

| #define PSP_MAILBOX_BAR_EN BIT(4) |

Definition at line 151 of file southbridge.h.

| #define PWR_RESET_CFG 0x10 |

Definition at line 21 of file southbridge.h.

| #define PWRBTN_EN BIT(8) |

Definition at line 46 of file southbridge.h.

| #define PWRBTN_STS BIT(8) |

Definition at line 40 of file southbridge.h.

| #define RTC_EN BIT(10) |

Definition at line 45 of file southbridge.h.

| #define RTC_STS BIT(10) |

Definition at line 39 of file southbridge.h.

| #define SATA_CAPABILITIES_REG 0xfc |

Definition at line 141 of file southbridge.h.

| #define SATA_CAPABILITY_SPM BIT(12) |

Definition at line 142 of file southbridge.h.

| #define SATA_MISC_CONTROL_REG 0x40 |

Definition at line 138 of file southbridge.h.

| #define SATA_MISC_SUBCLASS_WREN BIT(0) |

Definition at line 139 of file southbridge.h.

| #define SS_AMOUNT_DSFRAC_MASK (0xffff << SS_AMOUNT_DSFRAC_SHIFT) |

Definition at line 96 of file southbridge.h.

| #define SS_AMOUNT_DSFRAC_SHIFT 16 |

Definition at line 95 of file southbridge.h.

| #define SS_AMOUNT_NFRAC_SLIP_MASK (0xf << SS_AMOUNT_NFRAC_SLIP_SHIFT) |

Definition at line 99 of file southbridge.h.

| #define SS_AMOUNT_NFRAC_SLIP_SHIFT 8 |

Definition at line 98 of file southbridge.h.

| #define SS_STEP_SIZE_DSFRAC_MASK (0xffff << SS_STEP_SIZE_DSFRAC_SHIFT) |

Definition at line 94 of file southbridge.h.

| #define SS_STEP_SIZE_DSFRAC_SHIFT 0 |

Definition at line 93 of file southbridge.h.

| #define TIMER_STS BIT(0) |

Definition at line 48 of file southbridge.h.

| #define TIMER_STS BIT(0) |

Definition at line 48 of file southbridge.h.

| #define TOGGLE_ALL_PWR_GOOD BIT(1) |

Definition at line 22 of file southbridge.h.

| #define TOTAL_BITS | ( | a | ) | (8 * sizeof(a)) |

Definition at line 135 of file southbridge.h.

| #define USB_OC0 0 |

Definition at line 112 of file southbridge.h.

| #define USB_OC1 1 |

Definition at line 113 of file southbridge.h.

| #define USB_OC2 2 |

Definition at line 114 of file southbridge.h.

| #define USB_OC3 3 |

Definition at line 115 of file southbridge.h.

| #define USB_OC4 4 |

Definition at line 116 of file southbridge.h.

| #define USB_OC5 5 |

Definition at line 117 of file southbridge.h.

| #define USB_OC6 6 |

Definition at line 118 of file southbridge.h.

| #define USB_OC7 7 |

Definition at line 119 of file southbridge.h.

| #define USB_OC_DISABLE 0xf |

Definition at line 120 of file southbridge.h.

| #define USB_OC_DISABLE_ALL 0xffff |

Definition at line 121 of file southbridge.h.

| #define WAK_STS BIT(15) /*AcpiPmEvtBlkx00 Pm1Status */ |

Definition at line 37 of file southbridge.h.

| #define XHCI_FW_ADDR_OFFSET 0x6 |

Definition at line 175 of file southbridge.h.

| #define XHCI_FW_BOOTRAM_SIZE 0x8000 |

Definition at line 177 of file southbridge.h.

| #define XHCI_FW_SIG_OFFSET 0xc |

Definition at line 174 of file southbridge.h.

| #define XHCI_FW_SIZE_OFFSET 0x8 |

Definition at line 176 of file southbridge.h.

| #define XHCI_OVER_CURRENT_CONTROL 0x30 |

Definition at line 111 of file southbridge.h.

| #define XHCI_PM_INDIRECT_DATA 0x4c |

Definition at line 110 of file southbridge.h.

| #define XHCI_PM_INDIRECT_INDEX 0x48 |

Definition at line 109 of file southbridge.h.

| typedef struct aoac_devs aoac_devs_t |

Definition at line 114 of file early_fch.c.

References CONFIG, enable_acpimmio_decode_pm04(), enable_aoac_devices(), fch_disable_kb_rst(), fch_enable_cf9_io(), fch_enable_legacy_io(), fch_smbus_init(), fch_spi_early_init(), lpc_enable_port80(), lpc_enable_rom(), lpc_set_spibase(), sb_enable_lpc(), sb_lpc_decode(), setup_misc(), setup_spread_spectrum(), SPI_BASE_ADDRESS, and warm_reset().

Referenced by bootblock_soc_early_init().

Definition at line 145 of file early_fch.c.

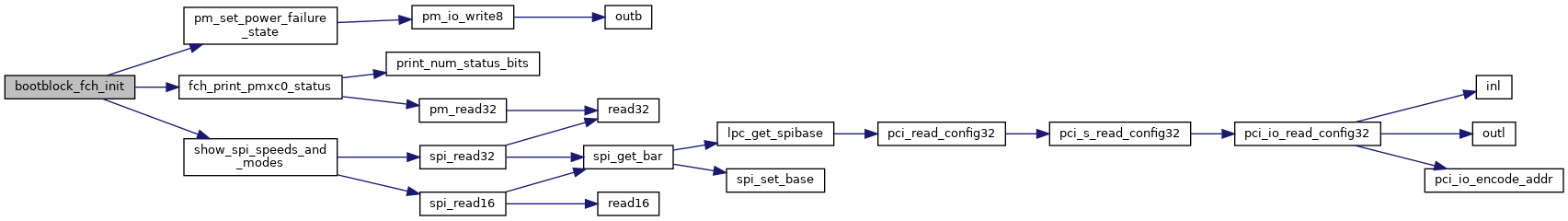

References fch_print_pmxc0_status(), pm_set_power_failure_state(), and show_spi_speeds_and_modes().

Referenced by bootblock_soc_init().

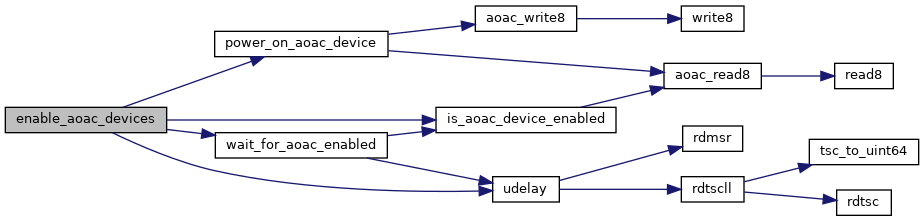

Definition at line 41 of file aoac.c.

References ARRAY_SIZE, CONFIG, FCH_AOAC_UART_FOR_CONSOLE, is_aoac_device_enabled(), power_on_aoac_device(), udelay(), and wait_for_aoac_enabled().

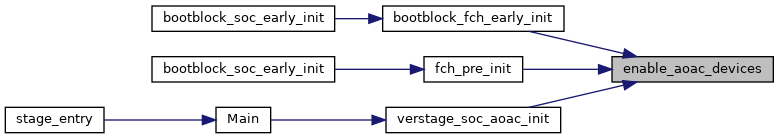

Referenced by bootblock_fch_early_init(), fch_pre_init(), and verstage_soc_aoac_init().

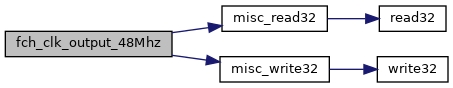

Definition at line 152 of file early_fch.c.

References MISC_CLK_CNTL1, misc_read32(), misc_write32(), OSCOUT1_CLK_OUTPUT_ENB, and OSCOUT2_CLK_OUTPUT_ENB.

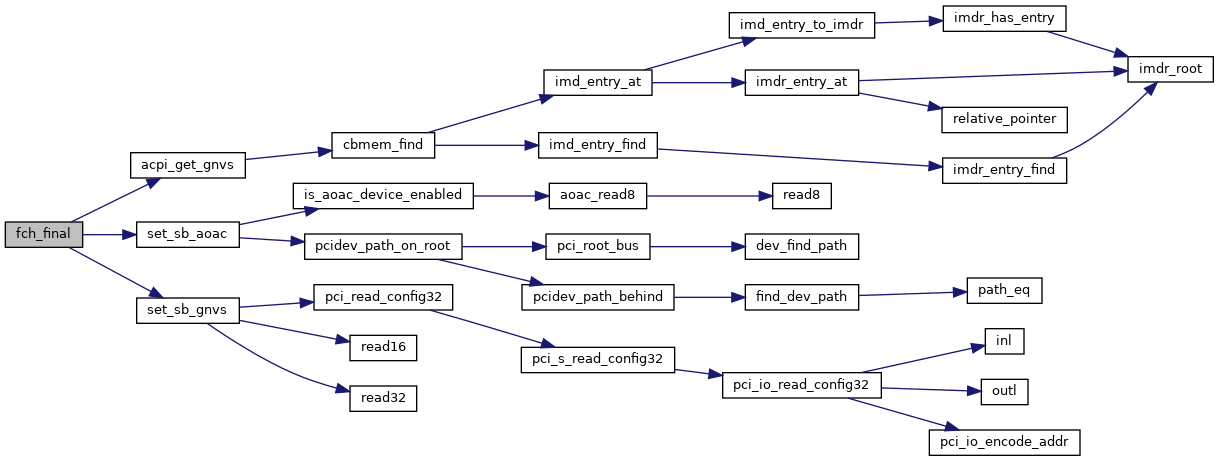

Definition at line 304 of file fch.c.

References acpi_get_gnvs(), global_nvs::aoac, gnvs, set_sb_aoac(), and set_sb_gnvs().

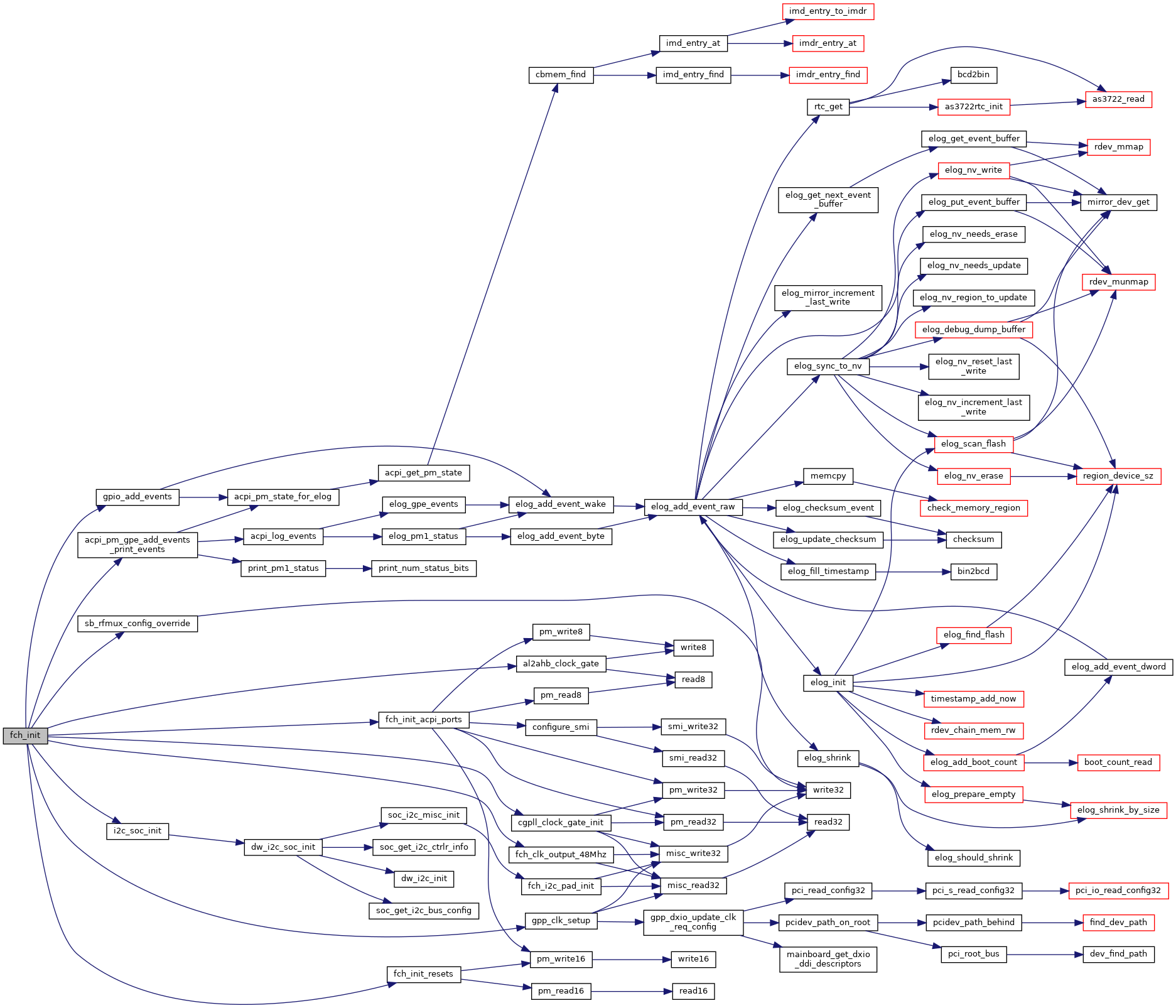

Definition at line 290 of file fch.c.

References acpi_pm_gpe_add_events_print_events(), al2ahb_clock_gate(), cgpll_clock_gate_init(), fch_clk_output_48Mhz(), fch_init_acpi_ports(), fch_init_resets(), gpio_add_events(), gpp_clk_setup(), i2c_soc_init(), and sb_rfmux_config_override().

Referenced by soc_init().

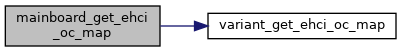

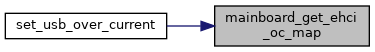

| int mainboard_get_ehci_oc_map | ( | uint16_t * | usb_oc_map | ) |

Definition at line 156 of file mainboard.c.

References BIOS_DEBUG, printk, and variant_get_ehci_oc_map().

Referenced by set_usb_over_current().

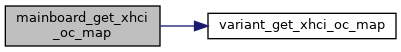

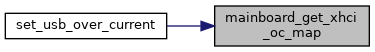

| int mainboard_get_xhci_oc_map | ( | uint16_t * | usb_oc_map | ) |

Definition at line 151 of file mainboard.c.

References BIOS_DEBUG, printk, and variant_get_xhci_oc_map().

Referenced by set_usb_over_current().

Definition at line 11 of file psp.c.

References ALIGN_DOWN, base, D18F1_MMIO_BASE0_LO, D18F1_MMIO_LIMIT0_LO, HPET_BASE_ADDRESS, KiB, MMIO_RE, MMIO_WE, PCI_COMMAND, PCI_COMMAND_MASTER, PCI_COMMAND_MEMORY, pci_read_config16(), pci_write_config16(), pci_write_config32(), PSP_BAR_ENABLES, PSP_MAILBOX_BAR, PSP_MAILBOX_BAR3_BASE, PSP_MAILBOX_BAR_EN, SOC_ADDR_DEV, and SOC_PSP_DEV.

Referenced by car_stage_entry().