|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

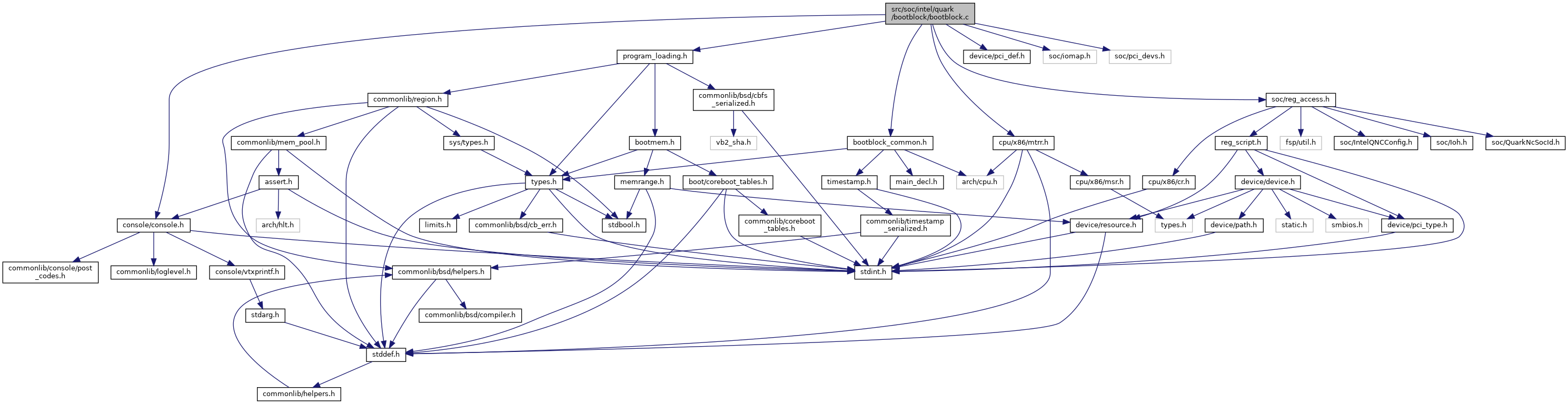

#include <bootblock_common.h>#include <console/console.h>#include <cpu/x86/mtrr.h>#include <device/pci_def.h>#include <program_loading.h>#include <soc/iomap.h>#include <soc/pci_devs.h>#include <soc/reg_access.h>

Go to the source code of this file.

Functions | |

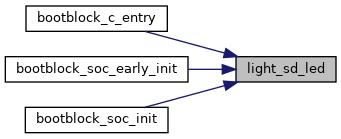

| void asmlinkage | light_sd_led (void) |

| asmlinkage void | bootblock_c_entry (uint64_t base_timestamp) |

| void | bootblock_soc_early_init (void) |

| void | bootblock_soc_init (void) |

| void | platform_prog_run (struct prog *prog) |

Variables | |

| static const struct reg_script | legacy_gpio_init [] |

| static const struct reg_script | i2c_gpio_controller_init [] |

| static const struct reg_script | hsuart_init [] |

| static const struct reg_script | mtrr_init [] |

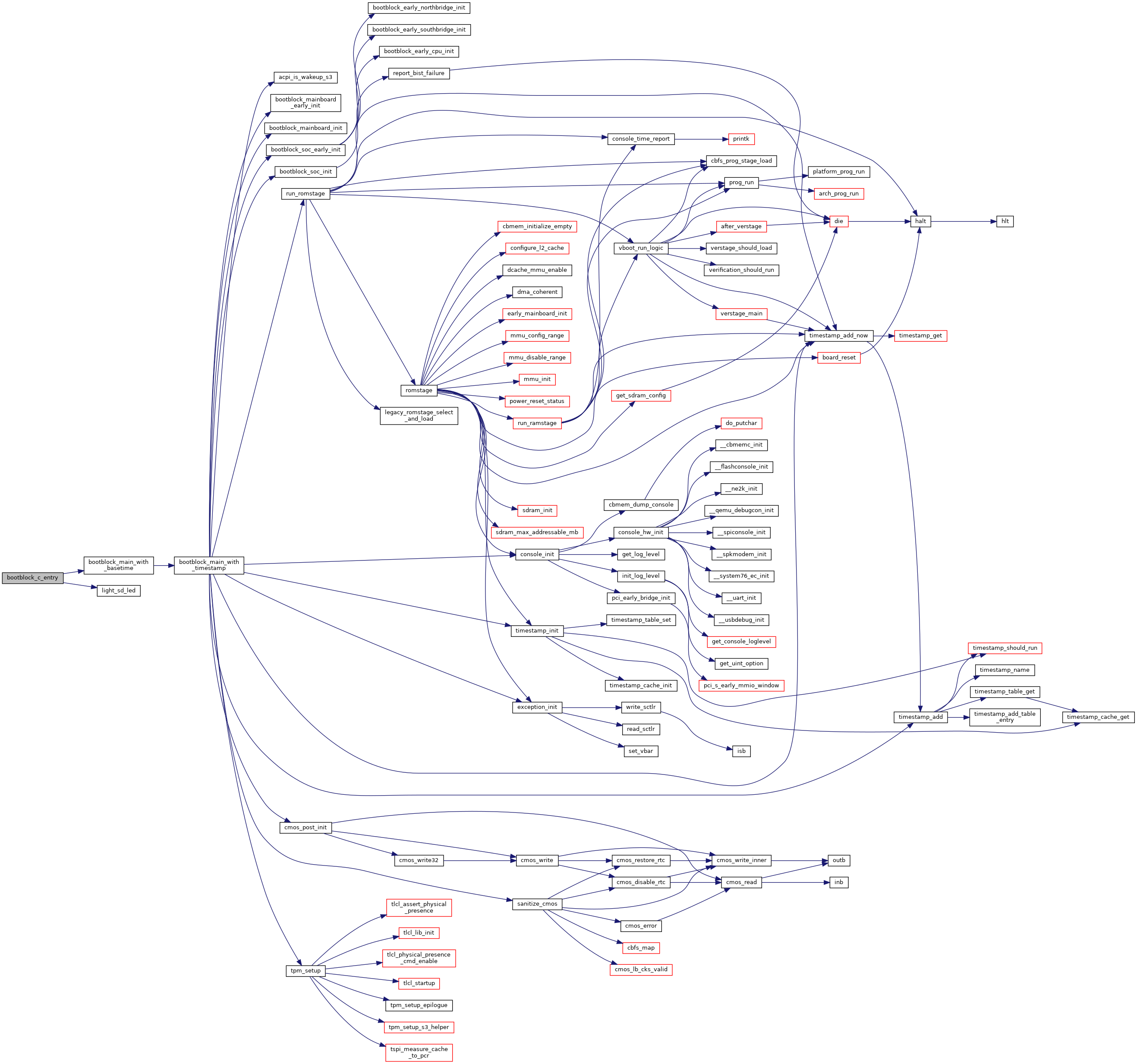

| asmlinkage void bootblock_c_entry | ( | uint64_t | base_timestamp | ) |

Definition at line 66 of file bootblock.c.

References bootblock_main_with_basetime(), CONFIG, and light_sd_led().

Definition at line 74 of file bootblock.c.

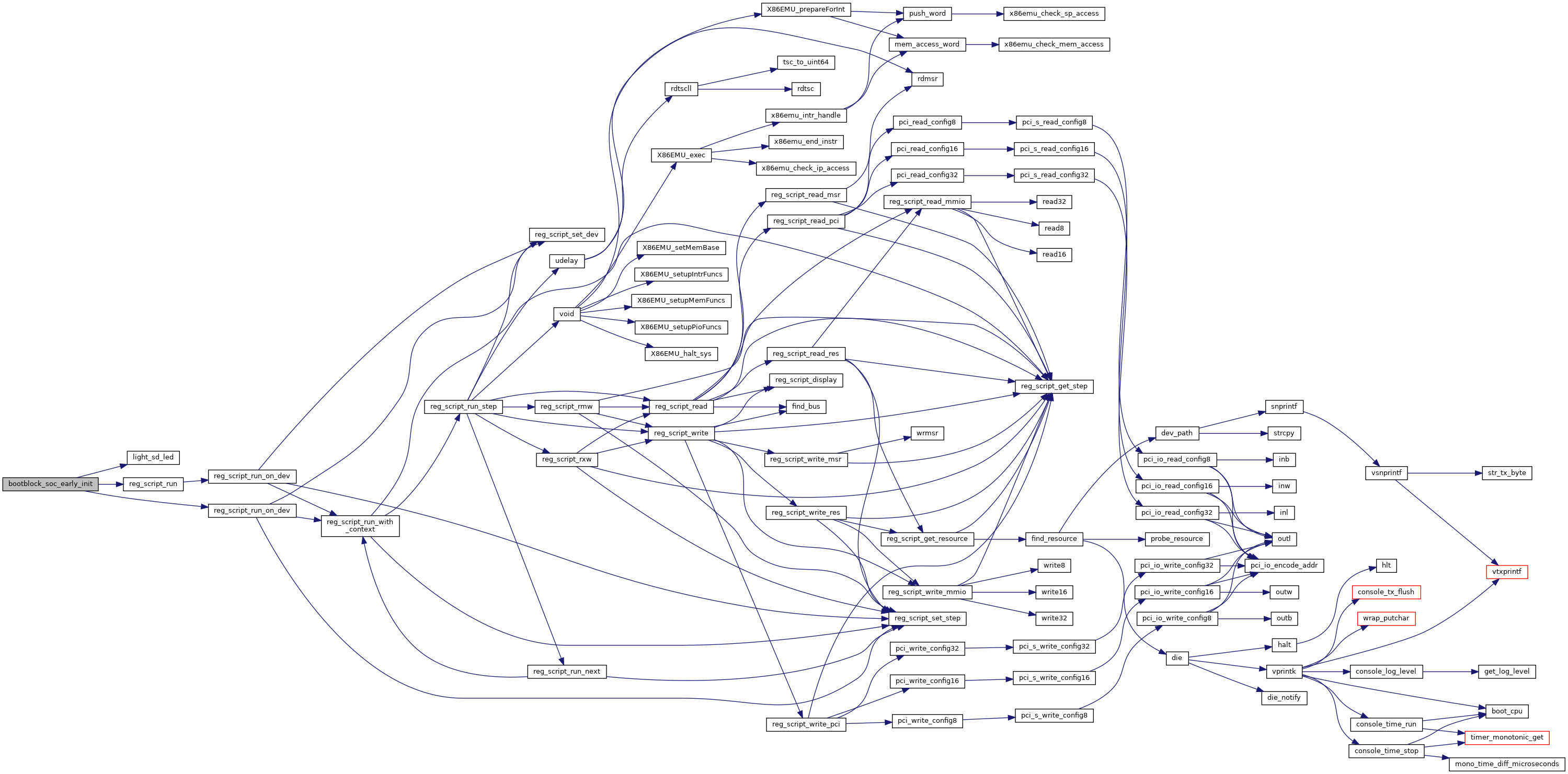

References CONFIG, HSUART0_BDF, HSUART1_BDF, hsuart_init, i2c_gpio_controller_init, I2CGPIO_BDF, legacy_gpio_init, light_sd_led(), LPC_BDF, mtrr_init, reg_script_run(), and reg_script_run_on_dev().

Definition at line 96 of file bootblock.c.

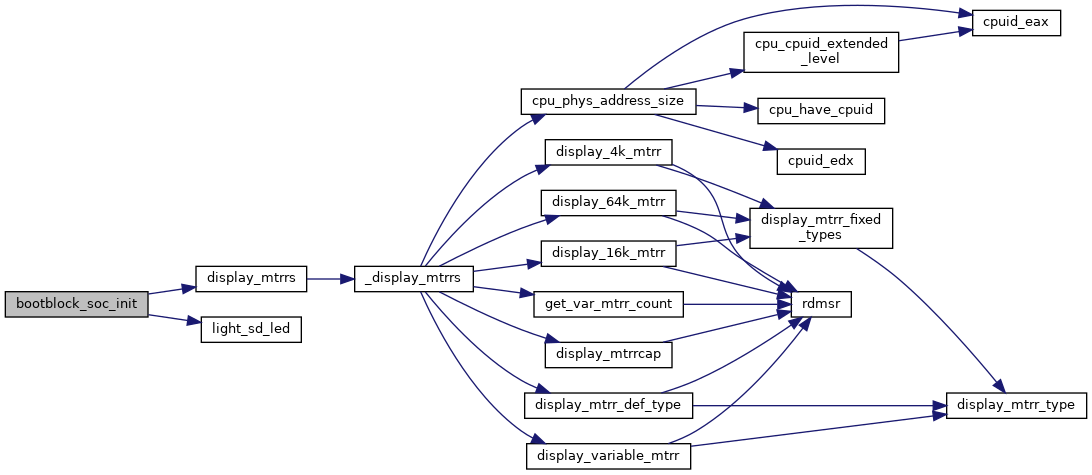

References CONFIG, display_mtrrs(), and light_sd_led().

| void asmlinkage light_sd_led | ( | void | ) |

Referenced by bootblock_c_entry(), bootblock_soc_early_init(), and bootblock_soc_init().

Definition at line 104 of file bootblock.c.

References prog::arg, BIOS_SPEW, prog::entry, prog::name, and printk.

|

static |

Definition at line 11 of file bootblock.c.

Referenced by bootblock_soc_early_init().

|

static |

Definition at line 11 of file bootblock.c.

Referenced by bootblock_soc_early_init().

|

static |

Definition at line 11 of file bootblock.c.

Referenced by bootblock_soc_early_init().

|

static |

Definition at line 11 of file bootblock.c.

Referenced by bootblock_soc_early_init().