|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

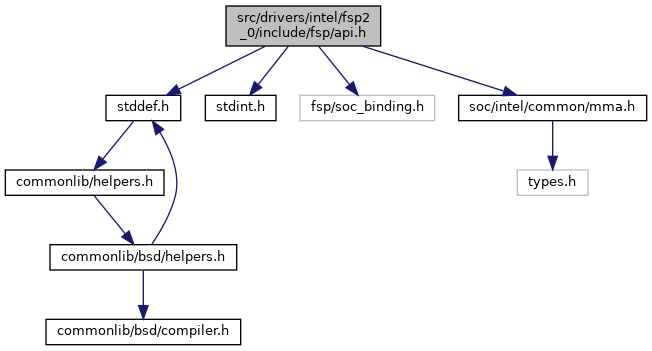

#include <stddef.h>#include <stdint.h>#include <fsp/soc_binding.h>#include <soc/intel/common/mma.h>

Go to the source code of this file.

Macros | |

| #define | FSP_SUCCESS EFI_SUCCESS |

| #define | FSP_INVALID_PARAMETER EFI_INVALID_PARAMETER |

| #define | FSP_DEVICE_ERROR EFI_DEVICE_ERROR |

| #define | FSP_NOT_FOUND EFI_NOT_FOUND |

| #define | FSP_NOT_STARTED EFI_NOT_STARTED |

| #define | FSP_UNSUPPORTED EFI_UNSUPPORTED |

Enumerations | |

| enum | fsp_boot_mode { FSP_BOOT_WITH_FULL_CONFIGURATION = 0x00 , FSP_BOOT_WITH_MINIMAL_CONFIGURATION = 0x01 , FSP_BOOT_ASSUMING_NO_CONFIGURATION_CHANGES = 0x02 , FSP_BOOT_ON_S4_RESUME = 0x05 , FSP_BOOT_ON_S3_RESUME = 0x11 , FSP_BOOT_ON_FLASH_UPDATE = 0x12 , FSP_BOOT_IN_RECOVERY_MODE = 0x20 } |

| enum | fsp_notify_phase { AFTER_PCI_ENUM = 0x20 , READY_TO_BOOT = 0x40 , END_OF_FIRMWARE = 0xF0 } |

Functions | |

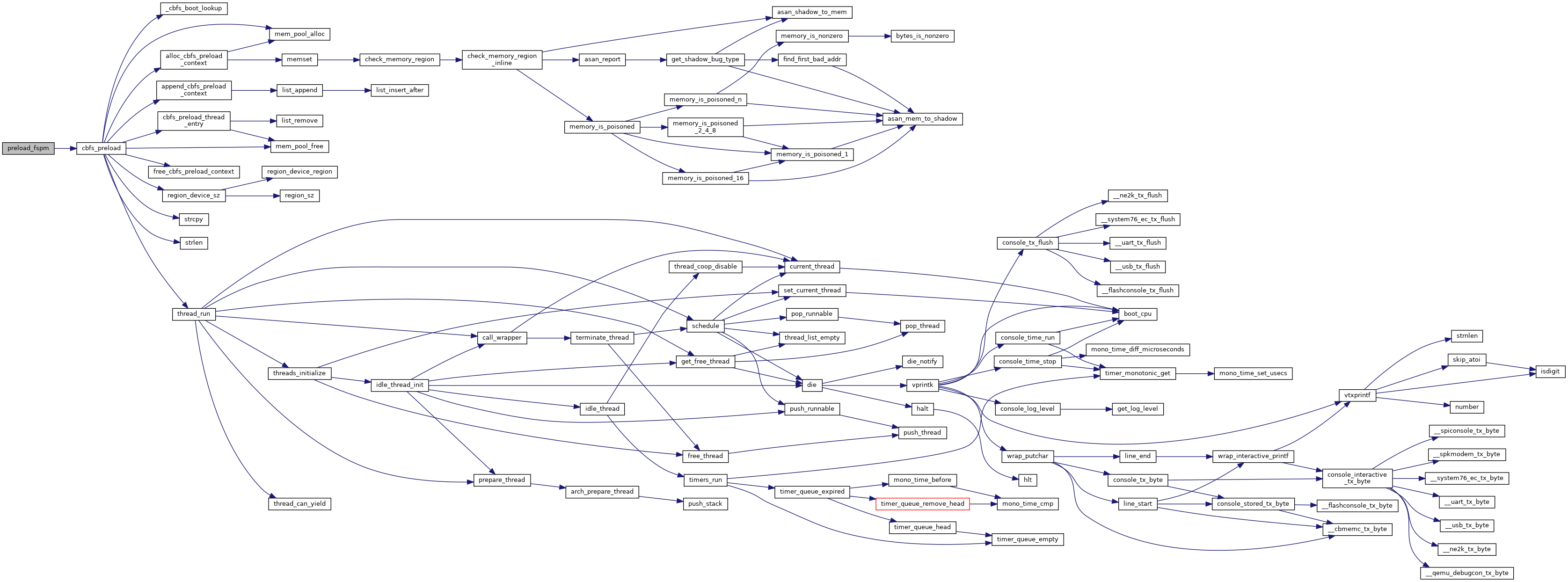

| void | preload_fspm (void) |

| void | fsp_memory_init (bool s3wake) |

| void | preload_fsps (void) |

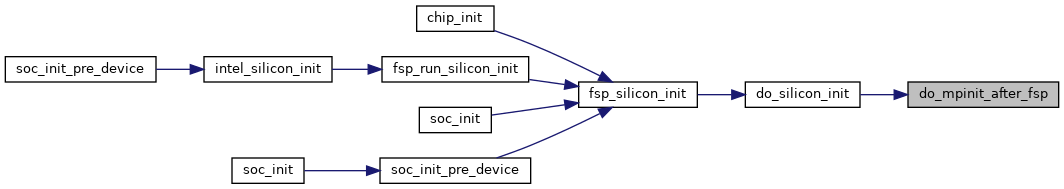

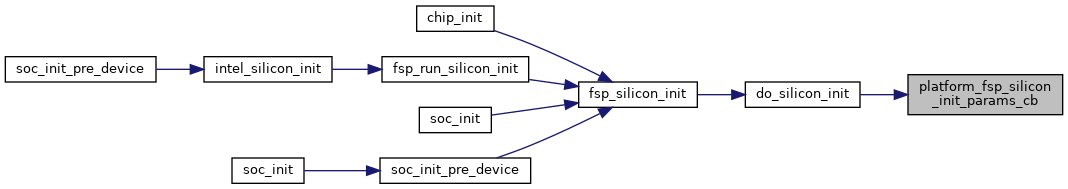

| void | fsp_silicon_init (void) |

| void | fsps_load (void) |

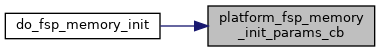

| void | platform_fsp_memory_init_params_cb (FSPM_UPD *mupd, uint32_t version) |

| void | platform_fsp_silicon_init_params_cb (FSPS_UPD *supd) |

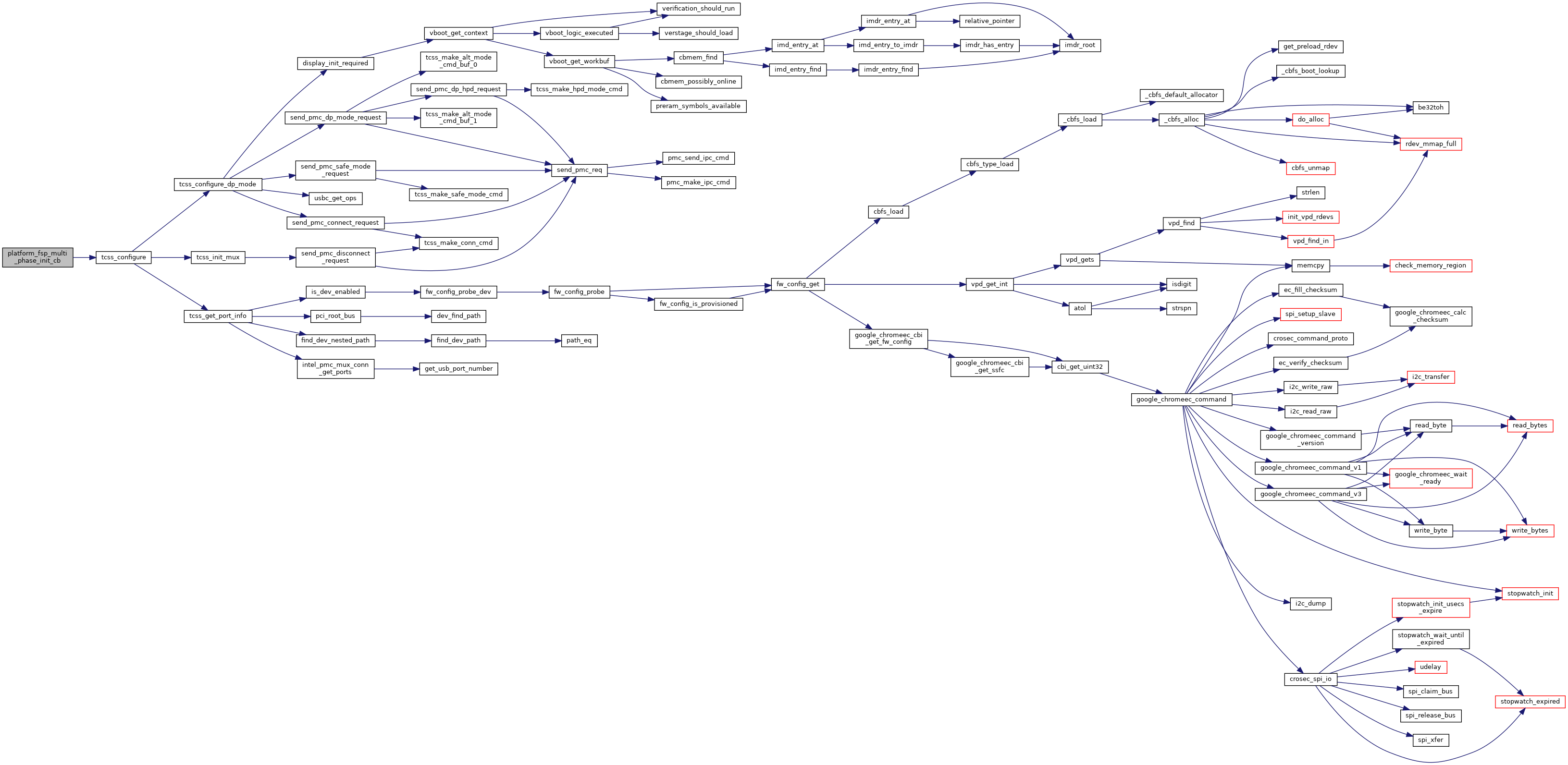

| void | platform_fsp_multi_phase_init_cb (uint32_t phase_index) |

| bool | fsp_is_multi_phase_init_enabled (void) |

| uint8_t | fsp_memory_mainboard_version (void) |

| uint8_t | fsp_memory_soc_version (void) |

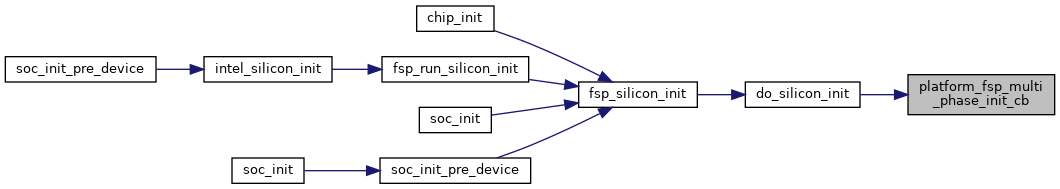

| void | platform_fsp_notify_status (enum fsp_notify_phase phase) |

| void | setup_mma (FSP_M_CONFIG *memory_cfg) |

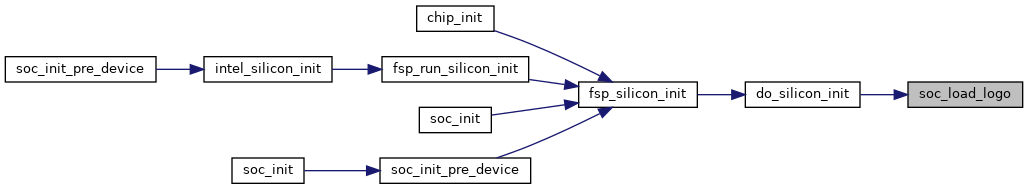

| void | soc_load_logo (FSPS_UPD *supd) |

| void | soc_update_memory_params_for_mma (FSP_M_CONFIG *memory_cfg, struct mma_config_param *mma_cfg) |

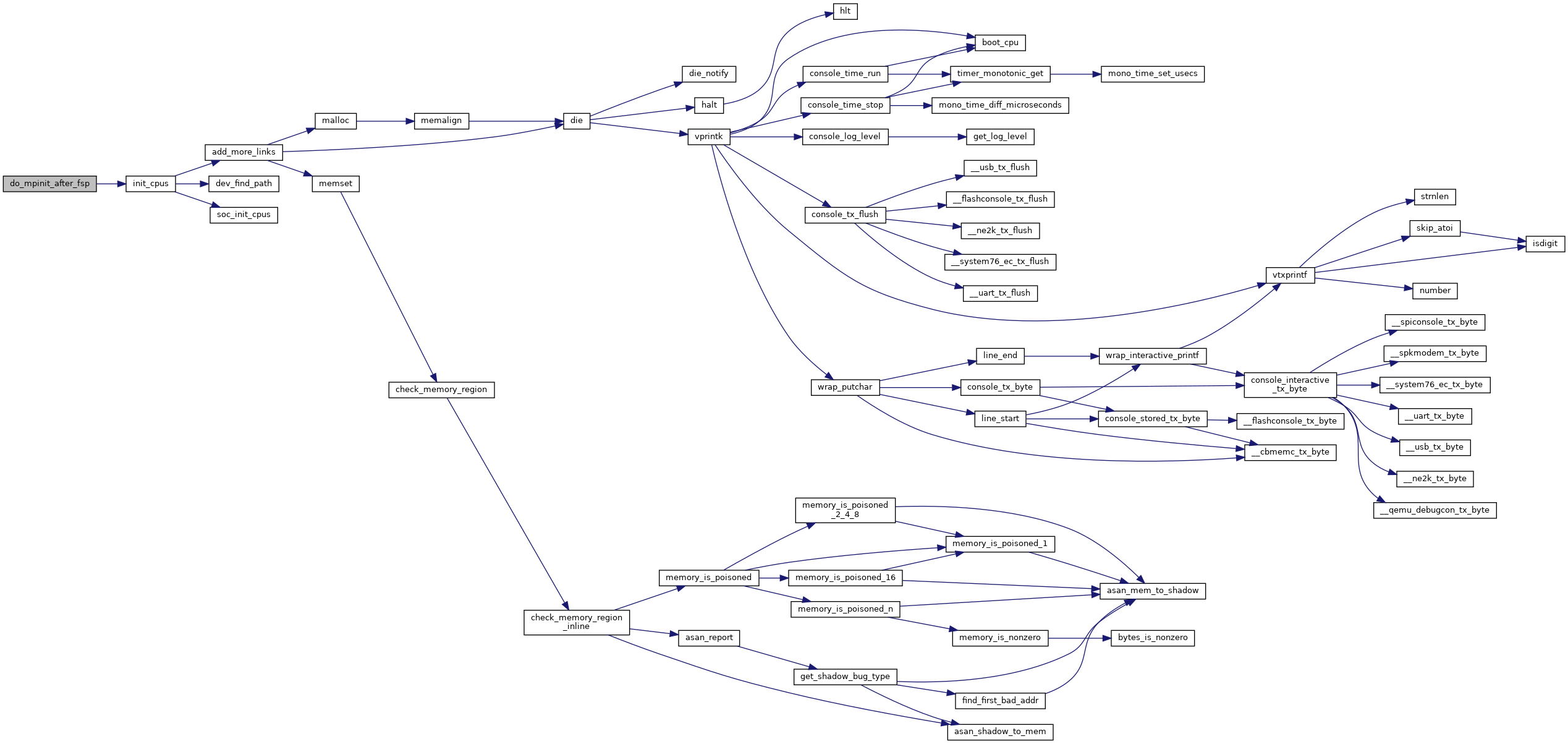

| void | do_mpinit_after_fsp (void) |

| enum fsp_boot_mode |

| enum fsp_notify_phase |

Definition at line 11 of file fsp_mpinit.c.

References init_cpus().

Referenced by do_silicon_init().

Definition at line 75 of file silicon_init.c.

References CONFIG, and fsps_hdr.

Referenced by do_silicon_init(), fsp_fill_common_arch_params(), and platform_fsp_silicon_init_params_cb().

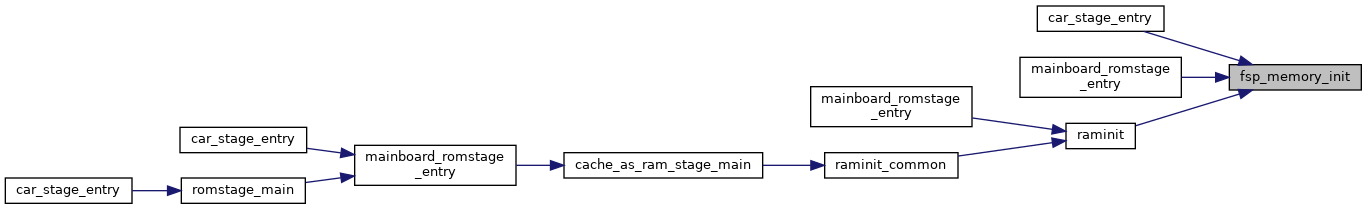

Definition at line 350 of file memory_init.c.

Referenced by car_stage_entry(), mainboard_romstage_entry(), and raminit().

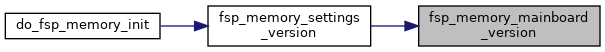

Definition at line 186 of file memory_init.c.

Referenced by fsp_memory_settings_version().

Definition at line 192 of file memory_init.c.

Referenced by fsp_memory_settings_version().

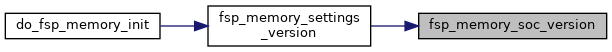

Definition at line 242 of file silicon_init.c.

References CONFIG, do_silicon_init(), fsp_display_timestamp(), fsps_hdr, fsps_load(), timestamp_add_now(), and TS_FSP_SILICON_INIT_LOAD.

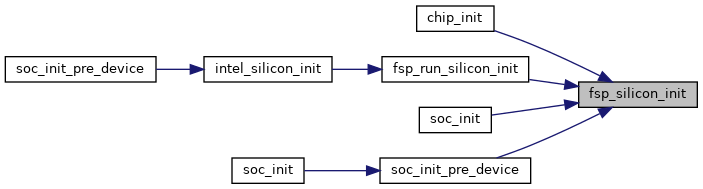

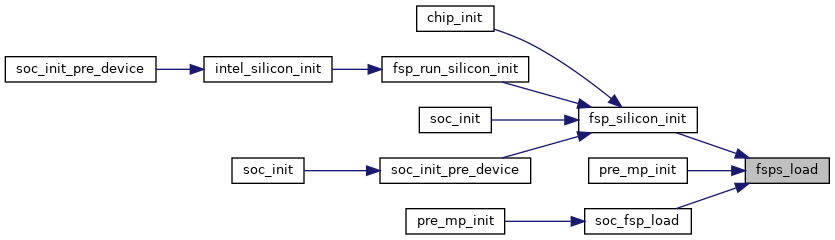

Referenced by chip_init(), fsp_run_silicon_init(), soc_init(), and soc_init_pre_device().

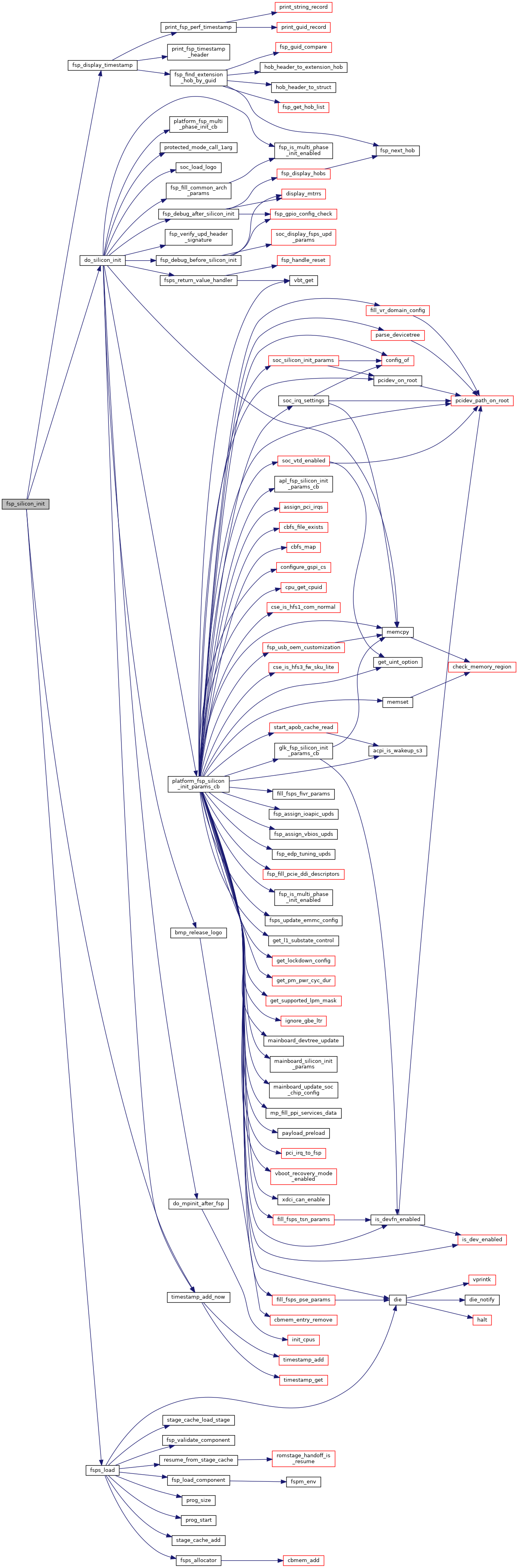

Definition at line 204 of file silicon_init.c.

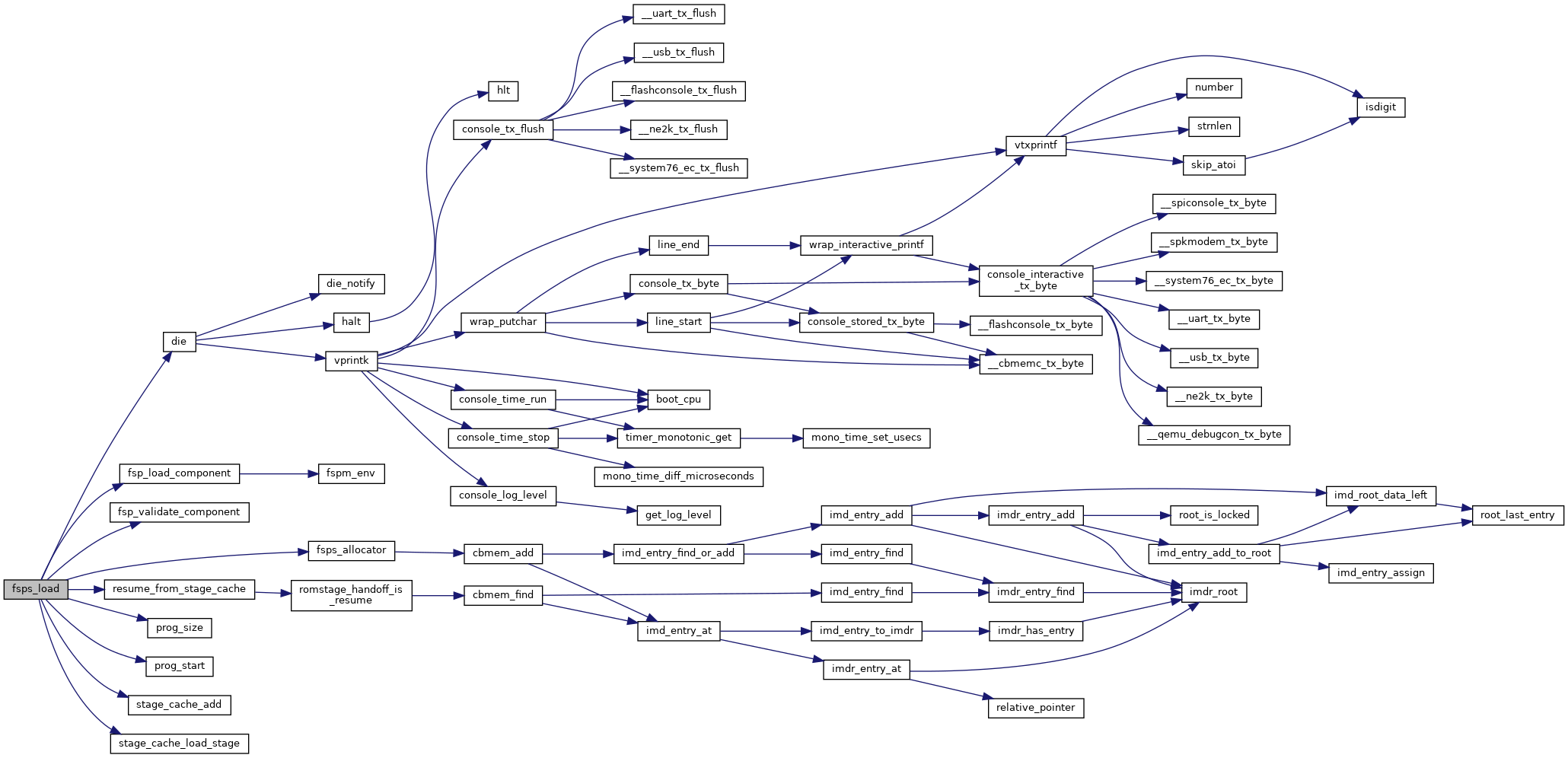

References BIOS_DEBUG, CB_SUCCESS, die(), fsp_load_component(), fsp_load_descriptor::fsp_prog, fsp_validate_component(), fsps_allocator(), fsps_hdr, printk, PROG_INIT, PROG_REFCODE, prog_size(), prog_start(), resume_from_stage_cache(), stage_cache_add(), stage_cache_load_stage(), and STAGE_REFCODE.

Referenced by fsp_silicon_init(), pre_mp_init(), and soc_fsp_load().

Definition at line 66 of file fsp_m_params.c.

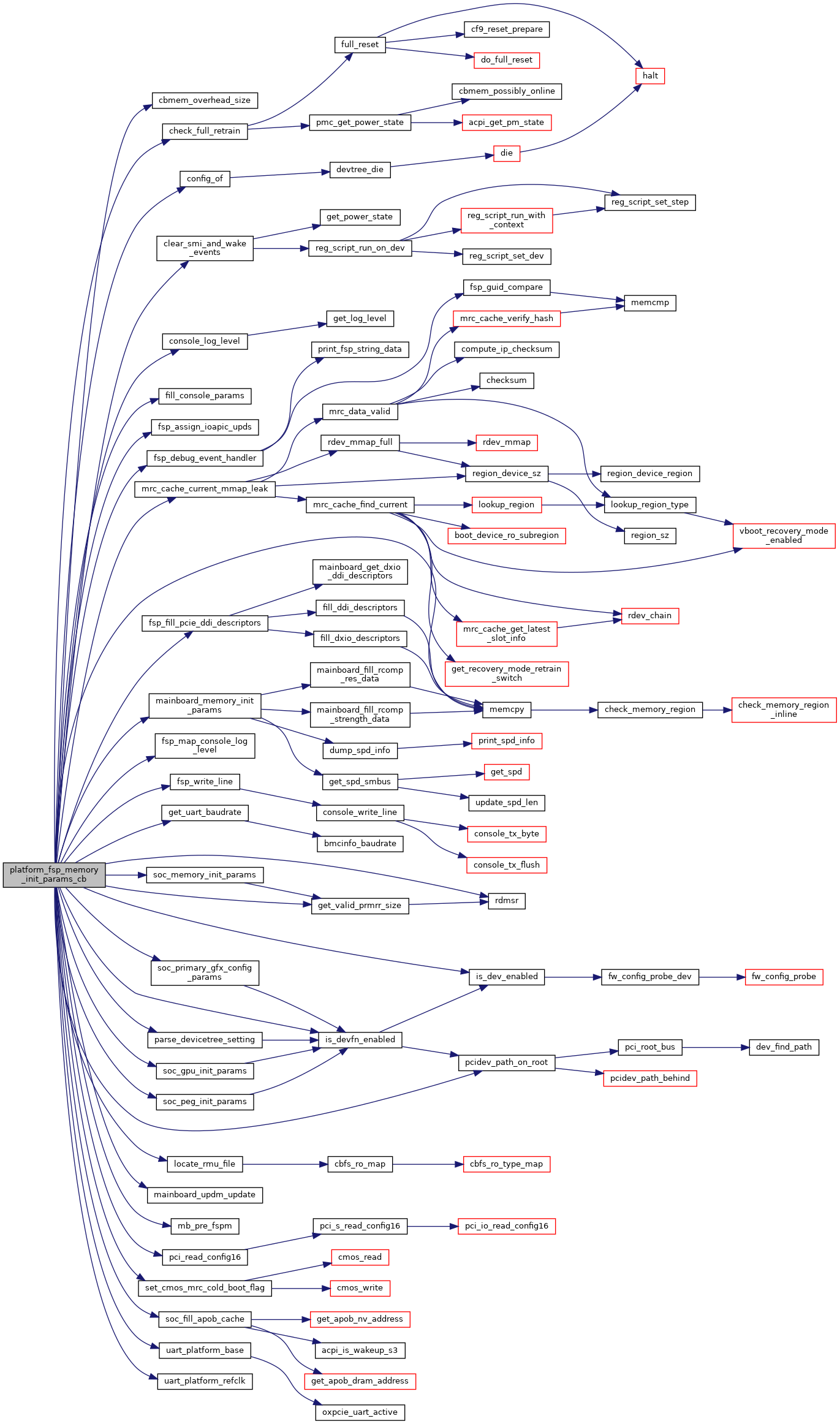

References _car_unallocated_start, _ecar_stack, ARRAY_SIZE, assert, BIOS_SPEW, BOARD_TYPE_DESKTOP, BOARD_TYPE_ULT_ULX, cbmem_overhead_size(), check_full_retrain(), clear_smi_and_wake_events(), config, CONFIG, config_of(), config_of_soc, console_log_level(), DEV_PTR, die_with_post_code, device::enabled, fill_console_params(), fsp_assign_ioapic_upds(), FSP_BOOT_WITH_FULL_CONFIGURATION, fsp_debug_event_handler(), fsp_fill_pcie_ddi_descriptors(), FSP_M_CONFIG, fsp_map_console_log_level(), fsp_version, fsp_write_line(), get_uart_baudrate(), get_valid_prmrr_size(), HECI1_BASE_ADDRESS, IOMMU_DEVFN, is_dev_enabled(), is_devfn_enabled(), msr_struct::lo, locate_rmu_file(), mainboard_memory_init_params(), mainboard_updm_update(), mask, mb_pre_fspm(), memcpy(), mrc_cache_current_mmap_leak(), MRC_VARIABLE_DATA, MSR_FLEX_RATIO, NULL, parse_devicetree_setting(), PCH_DEVFN_HDA, PCH_DEVFN_ISH, PCH_DEVFN_LPC, PCH_DEVFN_SMBUS, PCH_DEVFN_THERMAL, PCH_DEVFN_TRACEHUB, pci_read_config16(), PCI_VENDOR_ID, pcidev_path_on_root(), POST_INVALID_CBFS, printk, rdmsr(), SA_DEV_IGD, SA_DEVFN_IGD, SA_DEVFN_IPU, set_cmos_mrc_cold_boot_flag(), soc_fill_apob_cache(), soc_gpu_init_params(), SOC_INTEL_CML_SATA_DEV_MAX, soc_memory_init_params(), soc_peg_init_params(), soc_primary_gfx_config_params(), uart_platform_base(), uart_platform_refclk(), and version.

Referenced by do_fsp_memory_init().

Definition at line 27 of file silicon_init.c.

References BIOS_DEBUG, config, CONFIG, config_of_soc, printk, and tcss_configure().

Referenced by do_silicon_init().

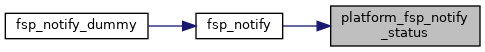

| void platform_fsp_notify_status | ( | enum fsp_notify_phase | phase | ) |

Definition at line 112 of file notify.c.

References resource::base, CFG_XHCLKGTEN, check_xdci_enable(), CONFIG, configure_xhci_host_mode_port0(), disable_xhci_lfps_pm(), drop_privilege_all(), END_OF_FIRMWARE, find_resource(), heci_cse_lockdown(), hide_hsuarts(), HSLTCGE, HSTCGE, HSUXDMIPLLSE, IOSFBTCGE, IOSFGBLCGE, IOSFSTCGE, p2sb_hide(), PCH_DEV_XHCI, PCI_BASE_ADDRESS_0, SRAMPGTEN, SSLSE, SSLTCGE, SSPLLSUE, SSTCGE, USB2PLLSE, write32(), XHCBBTCGIPISO, XHCBLCGE, XHCFTCLKSE, and XHCUSB2PLLSDLE.

Referenced by fsp_notify().

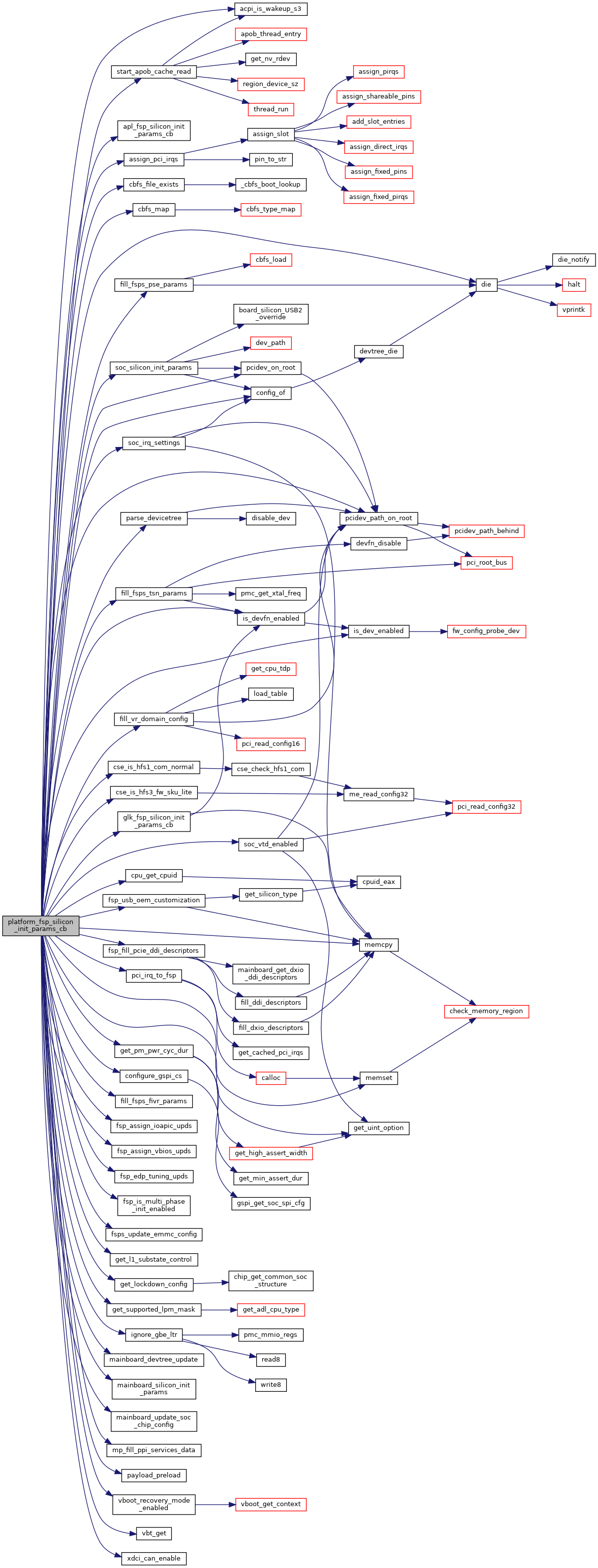

| void platform_fsp_silicon_init_params_cb | ( | FSPS_UPD * | supd | ) |

Definition at line 14 of file fsp_s_params.c.

References AC_LOADLINE_LANE_0_MAX, AC_LOADLINE_LANE_1_MAX, acpi_is_wakeup_s3(), apl_fsp_silicon_init_params_cb(), ARRAY_SIZE, assert, ASSERT, assign_pci_irqs(), BIOS_DEBUG, BIOS_INFO, cbfs_file_exists(), cbfs_map(), CHIPSET_LOCKDOWN_COREBOOT, CHIPSET_LOCKDOWN_FSP, config, CONFIG, config_of(), config_of_soc, configure_gspi_cs(), CORE_RATIO_LIMIT, cpu_get_cpuid(), cpu_id, CPUID_TIGERLAKE_A0, cse_is_hfs1_com_normal(), cse_is_hfs3_fw_sku_lite(), DC_LOADLINE_LANE_0_MAX, DC_LOADLINE_LANE_1_MAX, DEF_DITOVAL, DEF_DITOVAL_MS, DEF_DMVAL, device, die(), soc_intel_apollolake_config::DisableSataSalpSupport, soc_intel_apollolake_config::emmc_host_max_speed, soc_intel_apollolake_config::emmc_rx_cmd_data_cntl1, soc_intel_apollolake_config::emmc_rx_cmd_data_cntl2, soc_intel_apollolake_config::emmc_rx_strobe_cntl, soc_intel_apollolake_config::emmc_tx_cmd_cntl, soc_intel_apollolake_config::emmc_tx_data_cntl1, soc_intel_apollolake_config::emmc_tx_data_cntl2, soc_intel_apollolake_config::enable_vtd, EOP_DISABLE, fill_fsps_fivr_params(), fill_fsps_pse_params(), fill_fsps_tsn_params(), fill_vr_domain_config(), FSP_ARRAY_LOAD, fsp_assign_ioapic_upds(), fsp_assign_vbios_upds(), fsp_edp_tuning_upds(), fsp_fill_pcie_ddi_descriptors(), fsp_is_multi_phase_init_enabled(), FSP_S_CONFIG, fsp_usb_oem_customization(), fsps_update_emmc_config(), get_l1_substate_control(), get_lockdown_config(), get_pm_pwr_cyc_dur(), get_supported_lpm_mask(), get_uint_option(), GFXVT_BASE_ADDRESS, glk_fsp_silicon_init_params_cb(), GPIO_TERM_NATIVE, soc_intel_apollolake_config::hdaudio_bios_config_lockdown, soc_intel_apollolake_config::hdaudio_clk_gate_enable, soc_intel_apollolake_config::hdaudio_pwr_gate_enable, ICC_LIMIT_MAX, ignore_gbe_ltr(), IMON_OFFSET, IMON_SLOPE, irq_constraints, is_dev_enabled(), is_devfn_enabled(), soc_intel_apollolake_config::lpss_s0ix_enable, mainboard_devtree_update(), mainboard_silicon_init_params(), mainboard_update_soc_chip_config(), memcpy(), memset(), mp_fill_ppi_services_data(), NULL, OC_SKIP, params, parse_devicetree(), PAVP, payload_preload(), PCH_DEVFN_CIO, PCH_DEVFN_CNVI_WIFI, PCH_DEVFN_CNViWIFI, PCH_DEVFN_CSE_3, PCH_DEVFN_EMMC, PCH_DEVFN_GBE, PCH_DEVFN_HDA, PCH_DEVFN_ISH, PCH_DEVFN_SATA, PCH_DEVFN_SDCARD, PCH_DEVFN_SPI, PCH_DEVFN_THC0, PCH_DEVFN_THC1, PCH_DEVFN_THERMAL, PCH_DEVFN_UFS, PCH_DEVFN_USBOTG, PCH_DEVFN_XDCI, PCH_DEVFN_XHCI, PCI_FUNC, pci_irq_to_fsp(), PCI_SLOT, PCI_SUBSYSTEM_VENDOR_ID, pcidev_on_root(), pcidev_path_on_root(), PCIE_CLK_NOTUSED, PCIE_CLK_RP0, soc_intel_apollolake_config::pcie_rp_clkreq_pin, soc_intel_apollolake_config::pcie_rp_hotplug_enable, printk, soc_power_limits_config::psys_pmax, SA_DEV_SLOT_TBT, SA_DEVFN_CHAP, SA_DEVFN_DPTF, SA_DEVFN_GMM, SA_DEVFN_IGD, SA_DEVFN_IMGU, SA_DEVFN_ROOT, SA_DEVFN_TS, SA_DEVFN_VMD, SERIRQ_CONTINUOUS, soc_intel_apollolake_config::serirq_mode, SERIRQ_OFF, SERIRQ_QUIET, soc_irq_settings(), soc_silicon_init_params(), soc_vtd_enabled(), start_apob_cache_read(), device::subsystem_device, device::subsystem_vendor, TDC_CURRENT_LIMIT_MAX, THC_0, THC_1, THC_NONE, vboot_recovery_mode_enabled(), vbt_data, vbt_get(), VTVC0_BASE_ADDRESS, and xdci_can_enable().

Referenced by do_silicon_init().

Definition at line 341 of file memory_init.c.

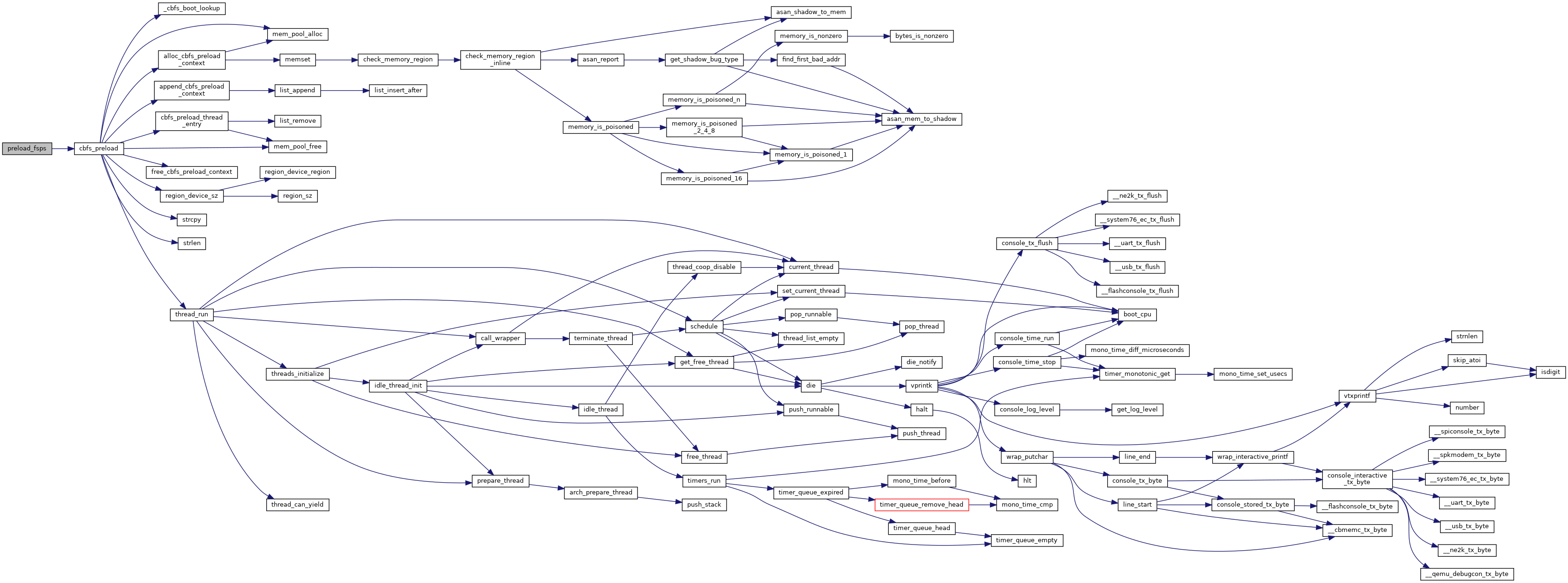

References BIOS_DEBUG, cbfs_preload(), CONFIG, and printk.

Definition at line 233 of file silicon_init.c.

References BIOS_DEBUG, cbfs_preload(), CONFIG, and printk.

Referenced by start_fsps_preload().

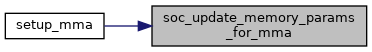

| void setup_mma | ( | FSP_M_CONFIG * | memory_cfg | ) |

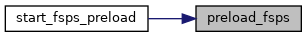

Definition at line 22 of file mma_core.c.

References BIOS_DEBUG, mma_map_param(), printk, and soc_update_memory_params_for_mma().

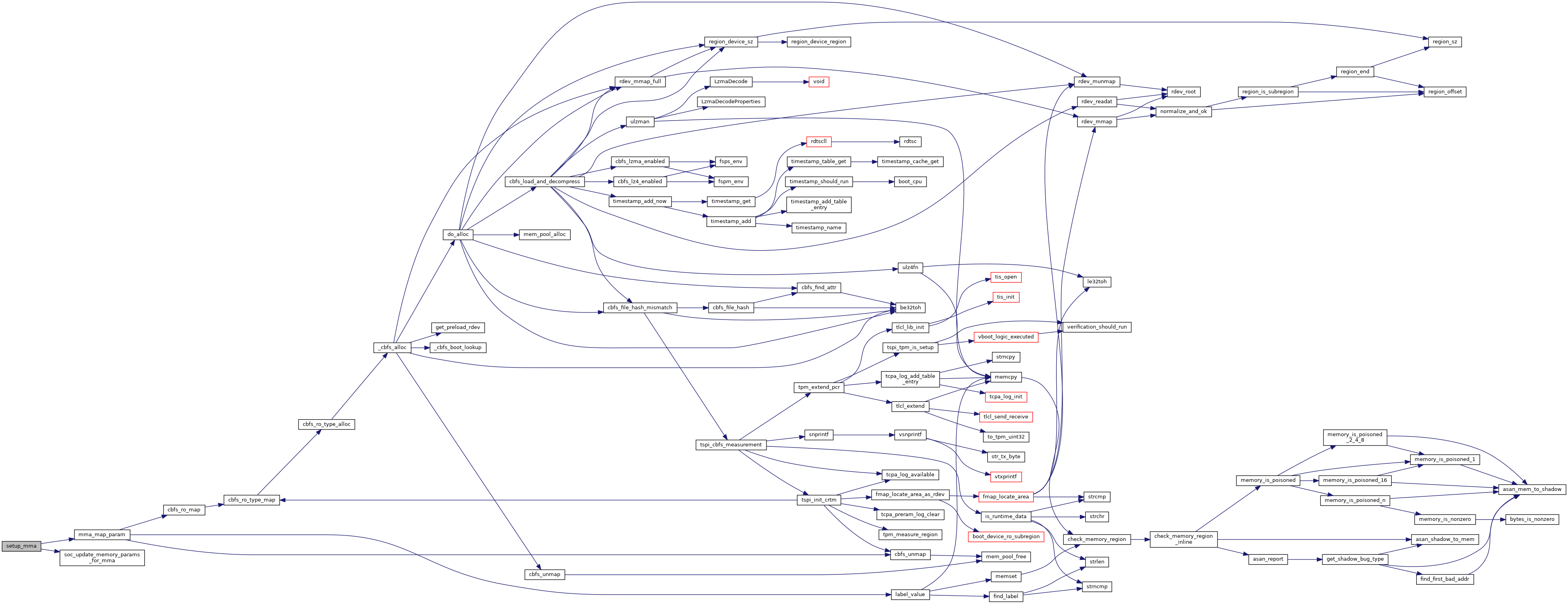

| void soc_load_logo | ( | FSPS_UPD * | supd | ) |

Definition at line 252 of file silicon_init.c.

References bmp_load_logo().

Referenced by do_silicon_init().

| void soc_update_memory_params_for_mma | ( | FSP_M_CONFIG * | memory_cfg, |

| struct mma_config_param * | mma_cfg | ||

| ) |

Definition at line 165 of file fsp_params.c.

References assert, CONFIG, mma_config_param::test_content, mma_config_param::test_content_size, mma_config_param::test_param, and mma_config_param::test_param_size.

Referenced by setup_mma().