|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

#include <types.h>

Go to the source code of this file.

Data Structures | |

| struct | msr_struct |

| struct | msrinit_struct |

Macros | |

| #define | IA32_EFER 0xC0000080 |

| #define | EFER_NXE (1 << 11) |

| #define | EFER_LMA (1 << 10) |

| #define | EFER_LME (1 << 8) |

| #define | EFER_SCE (1 << 0) |

| #define | TSC_MSR 0x10 |

| #define | IA32_PLATFORM_ID 0x17 |

| #define | IA32_APIC_BASE_MSR_INDEX 0x1B |

| #define | IA32_FEATURE_CONTROL 0x3a |

| #define | FEATURE_CONTROL_LOCK_BIT (1 << 0) |

| #define | FEATURE_ENABLE_VMX (1 << 2) |

| #define | SMRR_ENABLE (1 << 3) |

| #define | CPUID_VMX (1 << 5) |

| #define | CPUID_SMX (1 << 6) |

| #define | CPUID_DCA (1 << 18) |

| #define | CPUID_X2APIC (1 << 21) |

| #define | CPUID_AES (1 << 25) |

| #define | SGX_GLOBAL_ENABLE (1 << 18) |

| #define | PLATFORM_INFO_SET_TDP (1 << 29) |

| #define | IA32_BIOS_UPDT_TRIG 0x79 |

| #define | IA32_BIOS_SIGN_ID 0x8b |

| #define | IA32_MPERF 0xe7 |

| #define | IA32_APERF 0xe8 |

| #define | IA32_SMM_MONITOR_CTL_MSR 0x9B |

| #define | SMBASE_RO_MSR 0x98 |

| #define | IA32_SMM_MONITOR_VALID (1 << 0) |

| #define | IA32_MCG_CAP 0x179 |

| #define | MCG_CTL_P (1 << 8) |

| #define | MCA_BANKS_MASK 0xff |

| #define | IA32_PERF_STATUS 0x198 |

| #define | IA32_PERF_CTL 0x199 |

| #define | IA32_THERM_INTERRUPT 0x19b |

| #define | IA32_MISC_ENABLE 0x1a0 |

| #define | FAST_STRINGS_ENABLE_BIT (1 << 0) |

| #define | SPEED_STEP_ENABLE_BIT (1 << 16) |

| #define | IA32_ENERGY_PERF_BIAS 0x1b0 |

| #define | ENERGY_POLICY_PERFORMANCE 0 |

| #define | ENERGY_POLICY_NORMAL 6 |

| #define | ENERGY_POLICY_POWERSAVE 15 |

| #define | ENERGY_POLICY_MASK 0xf |

| #define | IA32_PACKAGE_THERM_INTERRUPT 0x1b2 |

| #define | SMRR_PHYSBASE_MSR 0x1F2 |

| #define | SMRR_PHYSMASK_MSR 0x1F3 |

| #define | IA32_PLATFORM_DCA_CAP 0x1f8 |

| #define | DCA_TYPE0_EN (1 << 0) |

| #define | IA32_PAT 0x277 |

| #define | IA32_MC0_CTL 0x400 |

| #define | IA32_MC_CTL(bank) (IA32_MC0_CTL + 4 * (bank)) |

| #define | IA32_MC0_STATUS 0x401 |

| #define | IA32_MC_STATUS(bank) (IA32_MC0_STATUS + 4 * (bank)) |

| #define | MCA_STATUS_HI_VAL (1UL << (63 - 32)) |

| #define | MCA_STATUS_HI_OVERFLOW (1UL << (62 - 32)) |

| #define | MCA_STATUS_HI_UC (1UL << (61 - 32)) |

| #define | MCA_STATUS_HI_EN (1UL << (60 - 32)) |

| #define | MCA_STATUS_HI_MISCV (1UL << (59 - 32)) |

| #define | MCA_STATUS_HI_ADDRV (1UL << (58 - 32)) |

| #define | MCA_STATUS_HI_PCC (1UL << (57 - 32)) |

| #define | MCA_STATUS_HI_COREID_VAL (1UL << (56 - 32)) |

| #define | MCA_STATUS_HI_CECC (1UL << (46 - 32)) |

| #define | MCA_STATUS_HI_UECC (1UL << (45 - 32)) |

| #define | MCA_STATUS_HI_DEFERRED (1UL << (44 - 32)) |

| #define | MCA_STATUS_HI_POISON (1UL << (43 - 32)) |

| #define | MCA_STATUS_HI_SUBLINK (1UL << (41 - 32)) |

| #define | MCA_STATUS_HI_ERRCOREID_MASK (0xf << 0) |

| #define | MCA_STATUS_LO_ERRCODE_EXT_SH 16 |

| #define | MCA_STATUS_LO_ERRCODE_EXT_MASK (0x3f << MCA_STATUS_LO_ERRCODE_EXT_SH) |

| #define | MCA_STATUS_LO_ERRCODE_MASK (0xffff << 0) |

| #define | IA32_MC0_ADDR 0x402 |

| #define | IA32_MC_ADDR(bank) (IA32_MC0_ADDR + 4 * (bank)) |

| #define | IA32_MC0_MISC 0x403 |

| #define | IA32_MC_MISC(bank) (IA32_MC0_MISC + 4 * (bank)) |

| #define | IA32_VMX_BASIC_MSR 0x480 |

| #define | VMX_BASIC_HI_DUAL_MONITOR (1UL << (49 - 32)) |

| #define | IA32_VMX_MISC_MSR 0x485 |

| #define | IA32_PM_ENABLE 0x770 |

| #define | HWP_ENABLE 0x1 |

| #define | IA32_HWP_CAPABILITIES 0x771 |

| #define | IA32_HWP_REQUEST 0x774 |

| #define | IA32_HWP_REQUEST_EPP_MASK 0xff000000 |

| #define | IA32_HWP_REQUEST_EPP_SHIFT 24 |

| #define | IA32_HWP_STATUS 0x777 |

| #define | IA32_L3_PROTECTED_WAYS 0xc85 |

| #define | IA32_SF_QOS_INFO 0xc87 |

| #define | IA32_SF_WAY_COUNT_MASK 0x3f |

| #define | IA32_PQR_ASSOC 0xc8f |

| #define | IA32_PQR_ASSOC_MASK (1 << 0 | 1 << 1) |

| #define | IA32_L3_MASK_1 0xc91 |

| #define | IA32_L3_MASK_2 0xc92 |

| #define | IA32_CR_SF_QOS_MASK_1 0x1891 |

| #define | IA32_CR_SF_QOS_MASK_2 0x1892 |

| #define | MCA_ERRCODE_TLB_DETECT 0xfff0 |

| #define | MCA_ERRCODE_TLB_TT_SH 2 /* Transaction Type */ |

| #define | MCA_ERRCODE_TLB_TT_MASK (0x3 << MCA_ERRCODE_TLB_TT_SH) |

| #define | MCA_ERRCODE_TLB_LL_SH 0 /* Cache Level */ |

| #define | MCA_ERRCODE_TLB_LL_MASK (0x3 << MCA_ERRCODE_TLB_LL_SH) |

| #define | MCA_ERRCODE_MEM_DETECT 0xff00 |

| #define | MCA_ERRCODE_MEM_RRRR_SH 4 /* Memory Transaction Type */ |

| #define | MCA_ERRCODE_MEM_RRRR_MASK (0xf << MCA_ERRCODE_MEM_RRRR_MASK) |

| #define | MCA_ERRCODE_MEM_TT_SH 2 /* Transaction Type */ |

| #define | MCA_ERRCODE_MEM_TT_MASK (0x3 << MCA_ERRCODE_MEM_TT_SH) |

| #define | MCA_ERRCODE_MEM_LL_SH 0 /* Cache Level */ |

| #define | MCA_ERRCODE_MEM_LL_MASK (0x3 << MCA_ERRCODE_MEM_LL_SH) |

| #define | MCA_ERRCODE_BUS_DETECT 0xf800 |

| #define | MCA_ERRCODE_BUS_PP_SH 9 /* Participation Processor */ |

| #define | MCA_ERRCODE_BUS_PP_MASK (0x3 << MCA_ERRCODE_BUS_PP_SH) |

| #define | MCA_ERRCODE_BUS_T_SH 8 /* Timeout */ |

| #define | MCA_ERRCODE_BUS_T_MASK (0x1 << MCA_ERRCODE_BUS_T_SH) |

| #define | MCA_ERRCODE_BUS_RRRR_SH 4 /* Memory Transaction Type */ |

| #define | MCA_ERRCODE_BUS_RRRR_MASK (0xf << MCA_ERRCODE_BUS_RRRR_SH) |

| #define | MCA_ERRCODE_BUS_II_SH 2 /* Memory or IO */ |

| #define | MCA_ERRCODE_BUS_II_MASK (0x3 << MCA_ERRCODE_BUS_II_SH) |

| #define | MCA_ERRCODE_BUS_LL_SH 0 /* Cache Level */ |

| #define | MCA_ERRCODE_BUS_LL_MASK (0x3 << MCA_ERRCODE_BUS_LL_SH) |

| #define | MCA_ERRCODE_INT_DETECT 0xfc00 |

| #define | MCA_ERRCODE_INT_UU_SH 8 /* Internal Error Type */ |

| #define | MCA_ERRCODE_INT_UU_MASK (0x3 << MCA_ERRCODE_INT_UU_SH) |

| #define | MCA_BANK_LS 0 /* Load-store, including DC */ |

| #define | MCA_BANK_IF 1 /* Instruction Fetch, including IC */ |

| #define | MCA_BANK_CU 2 /* Combined Unit, including L2 */ |

| #define | MCA_BANK_NB 4 /* Northbridge, including IO link */ |

| #define | MCA_BANK_EX 5 /* Execution Unit */ |

| #define | MCA_BANK_FP 6 /* Floating Point */ |

Typedefs | |

| typedef struct msr_struct | msr_t |

| typedef struct msrinit_struct | msrinit_t |

Enumerations | |

| enum | mca_err_code_types { MCA_ERRTYPE_UNKNOWN , MCA_ERRTYPE_TLB , MCA_ERRTYPE_MEM , MCA_ERRTYPE_BUS , MCA_ERRTYPE_INT } |

Functions | |

| static __always_inline msr_t | rdmsr (unsigned int index) |

| static __always_inline void | wrmsr (unsigned int index, msr_t msr) |

| static unsigned int | mca_get_bank_count (void) |

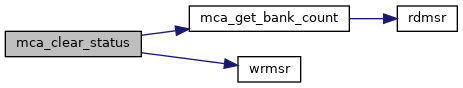

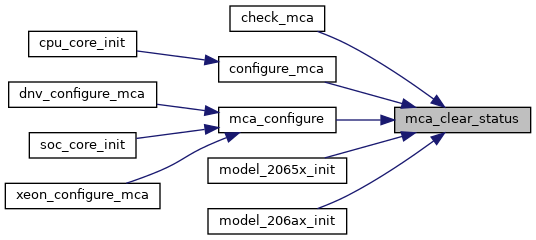

| static void | mca_clear_status (void) |

| static int | mca_valid (msr_t msr) |

| static int | mca_over (msr_t msr) |

| static int | mca_uc (msr_t msr) |

| static int | mca_en (msr_t msr) |

| static int | mca_miscv (msr_t msr) |

| static int | mca_addrv (msr_t msr) |

| static int | mca_pcc (msr_t msr) |

| static int | mca_idv (msr_t msr) |

| static int | mca_cecc (msr_t msr) |

| static int | mca_uecc (msr_t msr) |

| static int | mca_defd (msr_t msr) |

| static int | mca_poison (msr_t msr) |

| static int | mca_sublink (msr_t msr) |

| static uint16_t | mca_err_code (msr_t reg) |

| static uint16_t | mca_err_extcode (msr_t reg) |

| static enum mca_err_code_types | mca_err_type (msr_t reg) |

| static uint64_t | msr_read (unsigned int reg) |

| Helper for reading a MSR. More... | |

| static void | msr_write (unsigned int reg, uint64_t value) |

| Helper for writing a MSR. More... | |

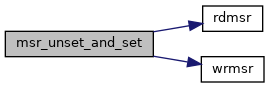

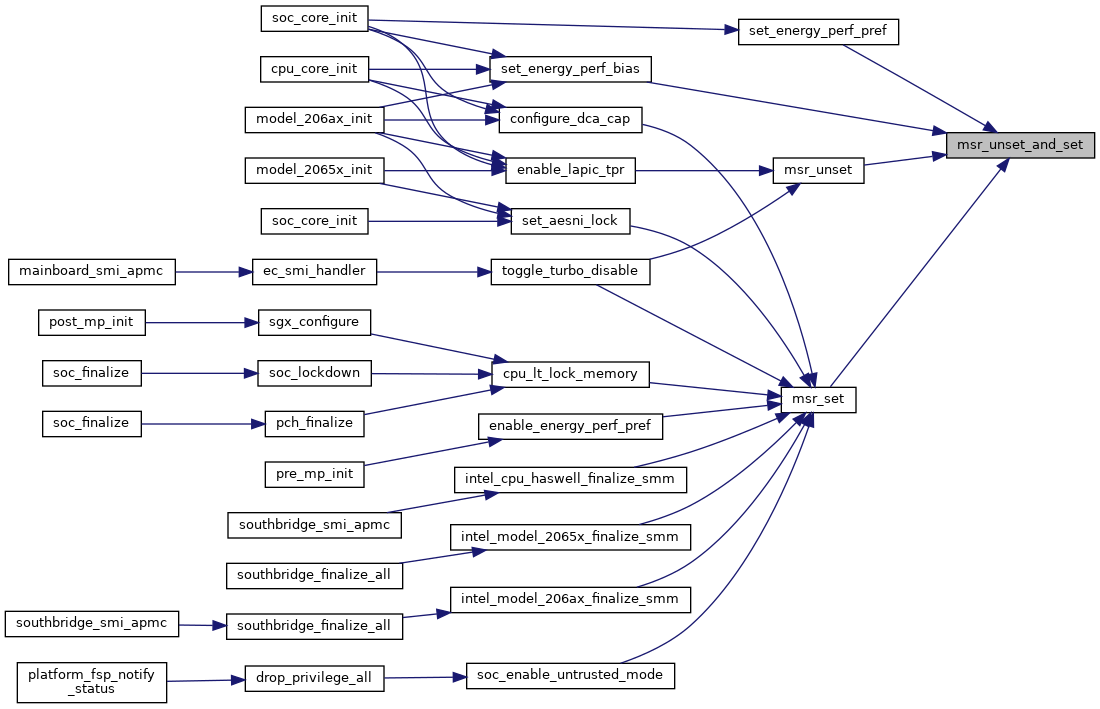

| static void | msr_unset_and_set (unsigned int reg, uint64_t unset, uint64_t set) |

| Helper for (un)setting MSR bitmasks. More... | |

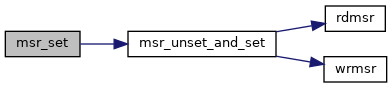

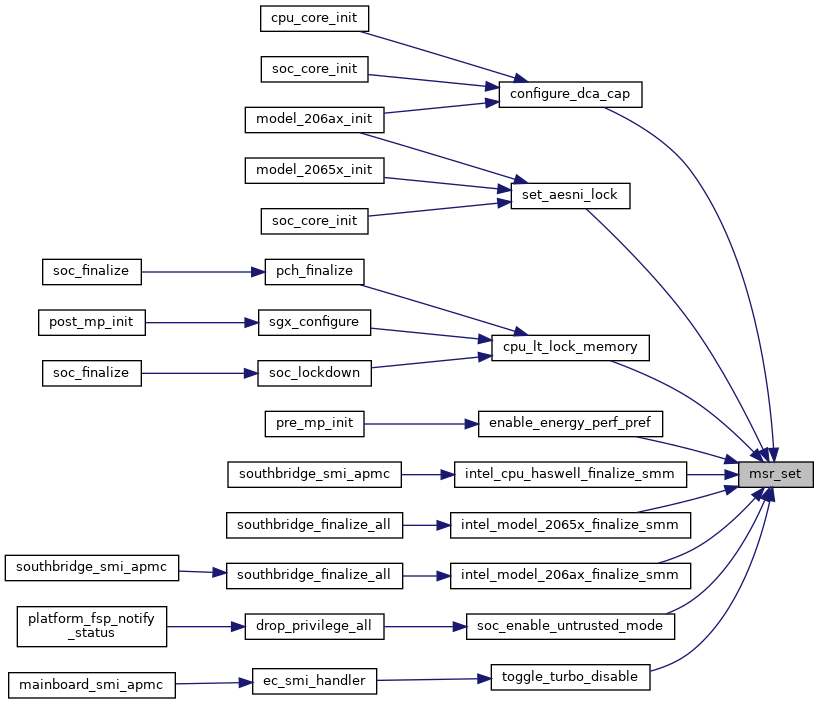

| static void | msr_set (unsigned int reg, uint64_t set) |

| Helper for setting MSR bitmasks. More... | |

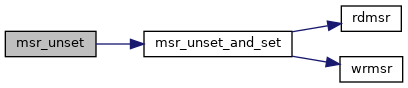

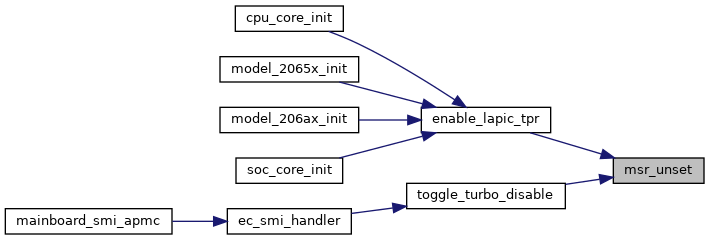

| static void | msr_unset (unsigned int reg, uint64_t unset) |

| Helper for unsetting MSR bitmasks. More... | |

| #define IA32_MC_ADDR | ( | bank | ) | (IA32_MC0_ADDR + 4 * (bank)) |

| #define IA32_MC_CTL | ( | bank | ) | (IA32_MC0_CTL + 4 * (bank)) |

| #define IA32_MC_MISC | ( | bank | ) | (IA32_MC0_MISC + 4 * (bank)) |

| #define IA32_MC_STATUS | ( | bank | ) | (IA32_MC0_STATUS + 4 * (bank)) |

| #define MCA_ERRCODE_BUS_II_MASK (0x3 << MCA_ERRCODE_BUS_II_SH) |

| #define MCA_ERRCODE_BUS_LL_MASK (0x3 << MCA_ERRCODE_BUS_LL_SH) |

| #define MCA_ERRCODE_BUS_PP_MASK (0x3 << MCA_ERRCODE_BUS_PP_SH) |

| #define MCA_ERRCODE_BUS_RRRR_MASK (0xf << MCA_ERRCODE_BUS_RRRR_SH) |

| #define MCA_ERRCODE_BUS_RRRR_SH 4 /* Memory Transaction Type */ |

| #define MCA_ERRCODE_BUS_T_MASK (0x1 << MCA_ERRCODE_BUS_T_SH) |

| #define MCA_ERRCODE_INT_UU_MASK (0x3 << MCA_ERRCODE_INT_UU_SH) |

| #define MCA_ERRCODE_MEM_LL_MASK (0x3 << MCA_ERRCODE_MEM_LL_SH) |

| #define MCA_ERRCODE_MEM_RRRR_MASK (0xf << MCA_ERRCODE_MEM_RRRR_MASK) |

| #define MCA_ERRCODE_MEM_RRRR_SH 4 /* Memory Transaction Type */ |

| #define MCA_ERRCODE_MEM_TT_MASK (0x3 << MCA_ERRCODE_MEM_TT_SH) |

| #define MCA_ERRCODE_TLB_LL_MASK (0x3 << MCA_ERRCODE_TLB_LL_SH) |

| #define MCA_ERRCODE_TLB_TT_MASK (0x3 << MCA_ERRCODE_TLB_TT_SH) |

| #define MCA_STATUS_LO_ERRCODE_EXT_MASK (0x3f << MCA_STATUS_LO_ERRCODE_EXT_SH) |

| typedef struct msr_struct msr_t |

| typedef struct msrinit_struct msrinit_t |

| enum mca_err_code_types |

|

inlinestatic |

Definition at line 212 of file msr.h.

References msr_struct::hi, and MCA_STATUS_HI_ADDRV.

|

inlinestatic |

Definition at line 227 of file msr.h.

References msr_struct::hi, and MCA_STATUS_HI_CECC.

Definition at line 176 of file msr.h.

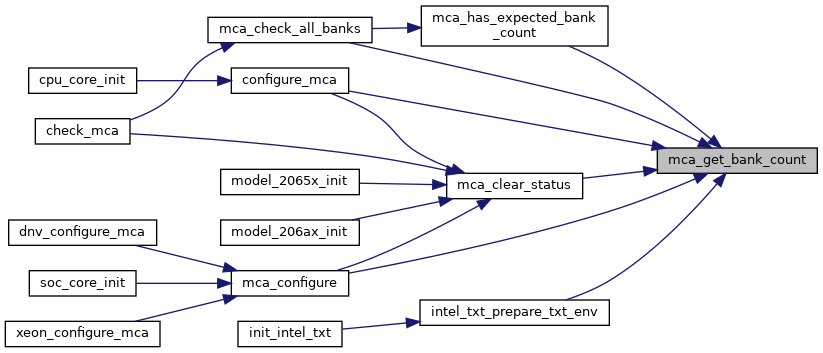

References IA32_MC_STATUS, msr_struct::lo, mca_get_bank_count(), and wrmsr().

Referenced by check_mca(), configure_mca(), mca_configure(), model_2065x_init(), and model_206ax_init().

|

inlinestatic |

Definition at line 237 of file msr.h.

References msr_struct::hi, and MCA_STATUS_HI_DEFERRED.

|

inlinestatic |

Definition at line 202 of file msr.h.

References msr_struct::hi, and MCA_STATUS_HI_EN.

Definition at line 252 of file msr.h.

References msr_struct::lo, and MCA_STATUS_LO_ERRCODE_MASK.

Definition at line 257 of file msr.h.

References msr_struct::lo, and MCA_STATUS_LO_ERRCODE_EXT_MASK.

|

inlinestatic |

Definition at line 257 of file msr.h.

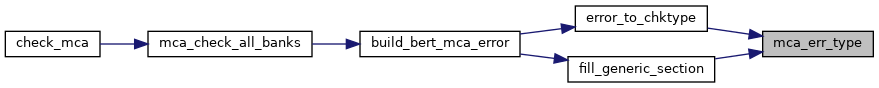

Referenced by error_to_chktype(), and fill_generic_section().

Definition at line 169 of file msr.h.

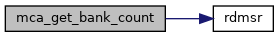

References IA32_MCG_CAP, msr_struct::lo, MCA_BANKS_MASK, and rdmsr().

Referenced by configure_mca(), intel_txt_prepare_txt_env(), mca_check_all_banks(), mca_clear_status(), mca_configure(), and mca_has_expected_bank_count().

|

inlinestatic |

Definition at line 222 of file msr.h.

References msr_struct::hi, and MCA_STATUS_HI_COREID_VAL.

|

inlinestatic |

Definition at line 207 of file msr.h.

References msr_struct::hi, and MCA_STATUS_HI_MISCV.

|

inlinestatic |

Definition at line 192 of file msr.h.

References msr_struct::hi, and MCA_STATUS_HI_OVERFLOW.

|

inlinestatic |

Definition at line 217 of file msr.h.

References msr_struct::hi, and MCA_STATUS_HI_PCC.

|

inlinestatic |

Definition at line 242 of file msr.h.

References msr_struct::hi, and MCA_STATUS_HI_POISON.

|

inlinestatic |

Definition at line 247 of file msr.h.

References msr_struct::hi, and MCA_STATUS_HI_SUBLINK.

|

inlinestatic |

Definition at line 197 of file msr.h.

References msr_struct::hi, and MCA_STATUS_HI_UC.

|

inlinestatic |

Definition at line 232 of file msr.h.

References msr_struct::hi, and MCA_STATUS_HI_UECC.

|

inlinestatic |

Definition at line 187 of file msr.h.

References msr_struct::hi, and MCA_STATUS_HI_VAL.

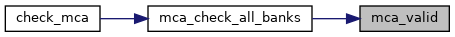

Referenced by mca_check_all_banks().

Helper for reading a MSR.

| [in] | reg | The MSR. |

Definition at line 335 of file msr.h.

References msr_struct::hi, msr_struct::lo, and rdmsr().

Helper for setting MSR bitmasks.

| [in] | reg | The MSR. |

| [in] | set | Bitmask with ones to the bits to set from the MSR. |

Definition at line 381 of file msr.h.

References msr_unset_and_set().

Referenced by configure_dca_cap(), cpu_lt_lock_memory(), enable_energy_perf_pref(), intel_cpu_haswell_finalize_smm(), intel_model_2065x_finalize_smm(), intel_model_206ax_finalize_smm(), set_aesni_lock(), soc_enable_untrusted_mode(), and toggle_turbo_disable().

Helper for unsetting MSR bitmasks.

| [in] | reg | The MSR. |

| [in] | unset | Bitmask with ones to the bits to unset from the MSR. |

Definition at line 392 of file msr.h.

References msr_unset_and_set().

Referenced by enable_lapic_tpr(), and toggle_turbo_disable().

Helper for (un)setting MSR bitmasks.

| [in] | reg | The MSR. |

| [in] | unset | Bitmask with ones to the bits to unset from the MSR. |

| [in] | set | Bitmask with ones to the bits to set from the MSR. |

Definition at line 363 of file msr.h.

References msr_struct::hi, msr_struct::lo, rdmsr(), and wrmsr().

Referenced by msr_set(), msr_unset(), set_energy_perf_bias(), and set_energy_perf_pref().

Helper for writing a MSR.

| [in] | reg | The MSR. |

| [in] | value | The value to be written to the MSR. |

Definition at line 347 of file msr.h.

References msr_struct::lo, value, and wrmsr().

|

static |

Definition at line 146 of file msr.h.

Referenced by acpi_fill_root_complex_tom(), activate_sgx(), add_simple_resources(), amd_initmmio(), amd_topmem(), amd_topmem2(), apply_microcode_patch(), backup_mtrr(), bsp_setup_msr_save_state(), bus_freq_khz(), calculate_l2_cache_size(), calculate_l2_latency(), calculate_l2_physical_address_range(), car_stage_entry(), cbmem_top_chipset(), clear_tvalid(), configure_c_states(), configure_emttm_tables(), configure_misc(), configure_p_states(), configure_pic_thermal_sensors(), configure_tcc_thermal_target(), configure_thermal_core(), configure_thermal_target(), cper_new_ia32x64_context_msr(), cpu_burst_mode(), cpu_bus_freq_khz(), cpu_config_tdp_levels(), cpu_flex_override(), cpu_get_burst_mode_state(), cpu_get_max_non_turbo_ratio(), cpu_get_max_ratio(), cpu_get_max_turbo_ratio(), cpu_get_min_ratio(), cpu_get_power_max(), cpu_get_tdp_nominal_ratio(), cpu_read_topology(), cpu_set_eist(), cpu_set_p_state_to_nominal_tdp_ratio(), cpu_set_p_state_to_turbo_ratio(), cpu_soc_is_in_untrusted_mode(), disable_lapic(), disable_turbo(), display_16k_mtrr(), display_4k_mtrr(), display_64k_mtrr(), display_mtrr_def_type(), display_mtrrcap(), display_variable_mtrr(), dnv_configure_mca(), domain_read_resources(), early_cache_setup(), early_cpu_init(), early_quickpath_init(), early_thermal_init(), enable_energy_perf_pref(), enable_fixed_mtrr(), enable_getsec_or_reset(), enable_lapic(), enable_sgx(), enable_turbo(), enable_var_mtrr(), fill_fspm_cpu_params(), fill_in_msr(), fill_in_pattrs(), find_cbfs_microcode(), fixed_mtrrs_expose_amd_rwdram(), fixed_mtrrs_hide_amd_rwdram(), flush_l1d_to_l2(), generate_cpu_entries(), generate_P_state_entries(), generate_p_state_entries(), get_cpu_count(), get_cpu_tdp(), get_free_var_mtrr(), get_fsb_tsc(), get_logical_cores_per_package(), get_platform_id(), get_pstate_info(), get_sku_tdp_config(), get_valid_prmrr_size(), get_var_mtrr_count(), get_vmcs_size(), getsec_enabled(), init_pm(), initialize_vr_config(), intel_cbnt_log_registers(), intel_txt_prepare_txt_env(), is_prmrr_approved(), is_prmrr_set(), is_sgx_supported(), is_x2apic_mode(), lapic_update32(), lock_sgx(), mainboard_enable(), max_cache_used(), mca_check_all_banks(), mca_get_bank_count(), mca_print_error(), msr_get_fsb(), msr_read(), msr_unset_and_set(), northbridge_fill_ssdt_generator(), northbridge_init(), p6_configure_l2_cache(), paging_set_nxe(), per_core_finalize(), per_cpu_smm_trigger(), platform_fsp_memory_init_params_cb(), prmrr_core_configure(), psp_notify_smm(), raminit(), read_cpu_topology(), read_l2(), read_msr_ppin(), recover_postcar_frame(), reg_script_read_msr(), restore_mtrr(), save_msr(), set_aesni_lock(), set_feature_ctrl_lock(), set_feature_ctrl_vmx_arg(), set_flex_ratio_to_tdp_nominal(), set_l2_ecc(), set_max_freq(), set_max_ratio(), set_max_turbo_freq(), set_power_limits(), set_range_uc(), signal_l2(), smbios_cpu_get_current_speed_mhz(), smbios_cpu_get_max_speed_mhz(), smbios_cpu_get_voltage(), smm_init(), smm_relocation_handler(), soc_get_mbox_address(), soc_get_psp_base_address(), soc_get_uncore_prmmr_base_and_mask(), soc_memory_init_params(), soc_power_states_generation(), soc_skip_ucode_update(), speedstep_get_limits(), stm_setup(), test_l2_address_alias(), timestamp_get(), tsc_freq_mhz(), udelay(), update_turbo_state(), write_mtrr(), write_smrr_alt(), x2apic_read(), x86_mtrr_check(), and xeon_configure_mca().

|

static |

Definition at line 157 of file msr.h.

References msr_struct::hi, and msr_struct::lo.

Referenced by activate_sgx(), apply_microcode_patch(), backup_mtrr(), bsp_setup_msr_save_state(), calculate_l2_cache_size(), calculate_l2_latency(), calculate_l2_physical_address_range(), car_stage_entry(), clear_all_var_mtrr(), clear_tvalid(), clear_var_mtrr(), commit_fixed_mtrrs(), commit_var_mtrrs(), configure_c_states(), configure_emttm_tables(), configure_mca(), configure_misc(), configure_p_states(), configure_pic_thermal_sensors(), configure_tcc_thermal_target(), configure_thermal_core(), configure_thermal_target(), cpu_burst_mode(), cpu_set_eist(), disable_cache_region(), disable_lapic(), disable_turbo(), dnv_configure_mca(), early_cache_setup(), early_cpu_init(), enable_cache_region(), enable_fixed_mtrr(), enable_getsec_or_reset(), enable_lapic(), enable_pci_mmconf(), enable_pm_timer_emulation(), enable_sgx(), enable_turbo(), enable_var_mtrr(), fixed_mtrrs_expose_amd_rwdram(), fixed_mtrrs_hide_amd_rwdram(), flush_l1d_to_l2(), init_dram_ddr3(), initialize_vr_config(), intel_microcode_load_unlocked(), lapic_update32(), lock_sgx(), mainboard_enable(), mca_clear_status(), mca_configure(), msr_unset_and_set(), msr_write(), owner_epoch_update(), p6_configure_l2_cache(), paging_set_nxe(), paging_set_pat(), per_core_finalize(), per_cpu_smm_trigger(), prmrr_core_configure(), read_msr_ppin(), reg_script_write_msr(), relocation_handler(), restore_mtrr(), set_cstate_io_addr(), set_feature_ctrl_lock(), set_feature_ctrl_vmx_arg(), set_flex_ratio_to_tdp_nominal(), set_insmm_sts(), set_l2_ecc(), set_max_freq(), set_max_ratio(), set_max_turbo_freq(), set_mtrr(), set_perf_control_msr(), set_power_limits(), set_range_uc(), set_var_mtrr(), signal_l2(), smm_init(), smm_relocation_handler(), stm_setup(), update_save_state(), write_prmrr(), write_resume_eip(), write_smrr(), write_smrr_alt(), write_uncore_prmrr(), x2apic_send_ipi(), x2apic_write(), and xeon_configure_mca().