|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

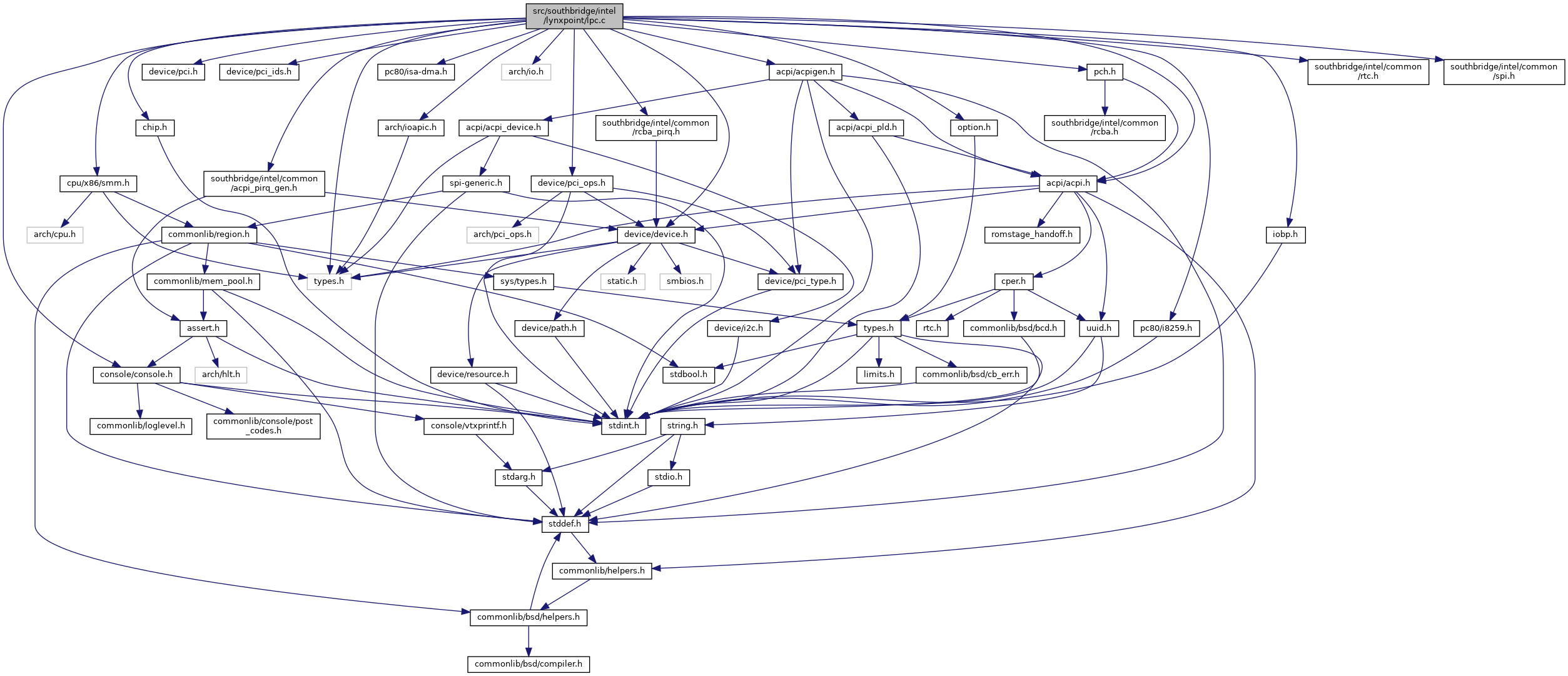

#include <console/console.h>#include <device/device.h>#include <device/pci.h>#include <device/pci_ids.h>#include <device/pci_ops.h>#include <option.h>#include <pc80/isa-dma.h>#include <pc80/i8259.h>#include <arch/io.h>#include <arch/ioapic.h>#include <acpi/acpi.h>#include <cpu/x86/smm.h>#include "chip.h"#include "iobp.h"#include "pch.h"#include <acpi/acpigen.h>#include <southbridge/intel/common/acpi_pirq_gen.h>#include <southbridge/intel/common/rcba_pirq.h>#include <southbridge/intel/common/rtc.h>#include <southbridge/intel/common/spi.h>#include <types.h>

Go to the source code of this file.

Macros | |

| #define | NMI_OFF 0 |

| #define | LPC_DEFAULT_IO_RANGE_LOWER 0 |

| #define | LPC_DEFAULT_IO_RANGE_UPPER 0x1000 |

Variables | |

| static struct device_operations | device_ops |

| static const unsigned short | pci_device_ids [] |

| static const struct pci_driver pch_lpc | __pci_driver |

Definition at line 278 of file lpc.c.

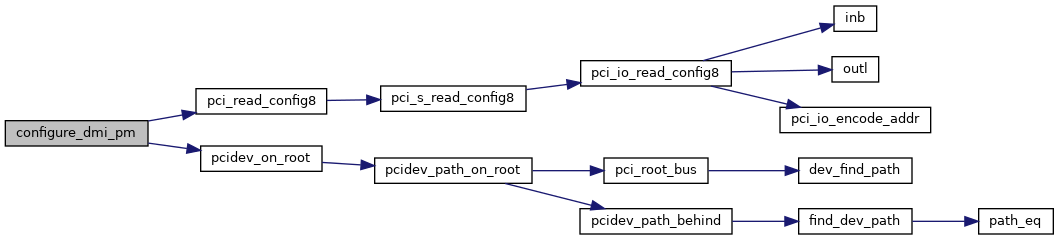

References pci_read_config8(), pcidev_on_root(), RCBA16, RCBA32_AND_OR, and RCBA32_OR.

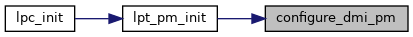

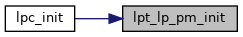

Referenced by lpt_pm_init().

Definition at line 484 of file lpc.c.

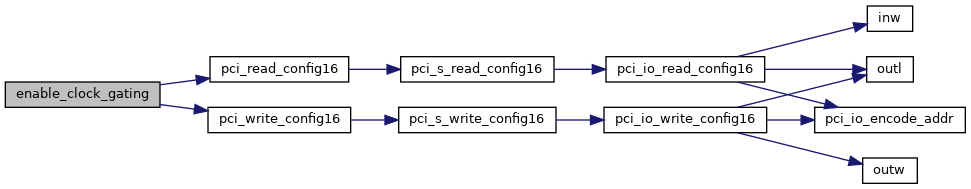

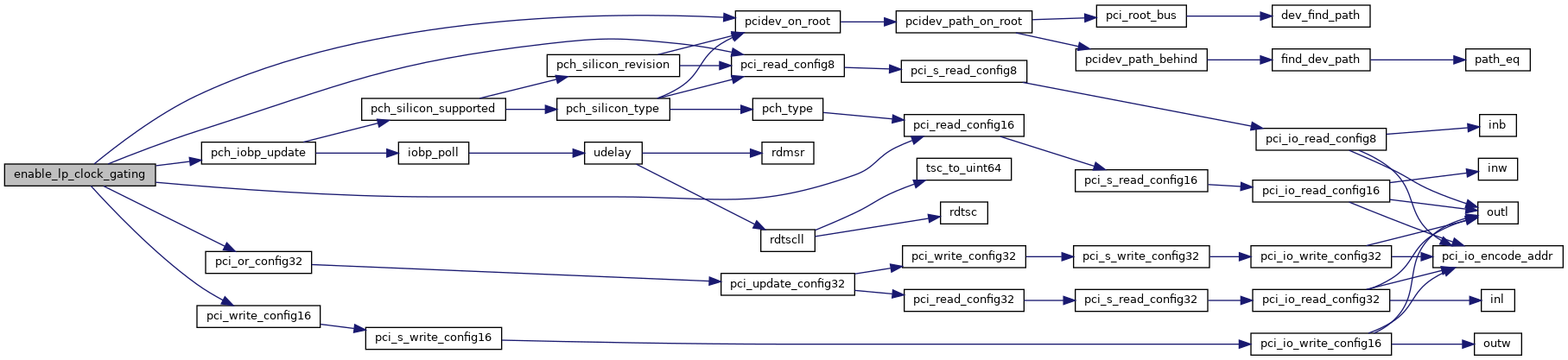

References CG, GEN_PMCON_1, pci_read_config16(), pci_write_config16(), RCBA32, RCBA32_AND_OR, and RCBA32_OR.

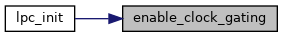

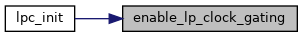

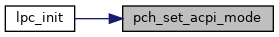

Referenced by lpc_init().

Definition at line 60 of file lpc.c.

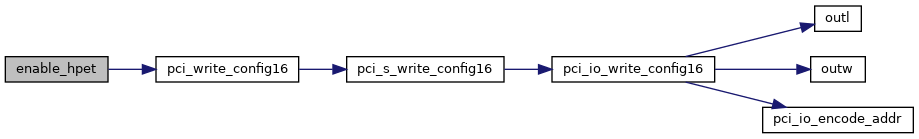

References HPTC, LPC_HnBDF, PCH_HPET_PCI_BUS, PCH_HPET_PCI_SLOT, pci_write_config16(), and RCBA32.

Referenced by lpc_init().

Definition at line 509 of file lpc.c.

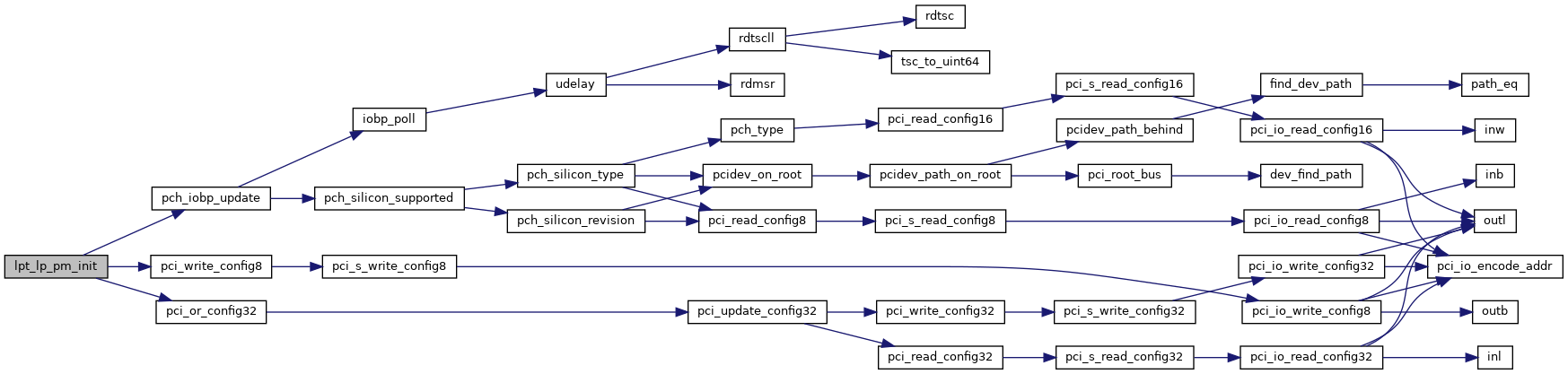

References BUC, CG, GEN_PMCON_1, PCH_DISABLE_GBE, pch_iobp_update(), pci_or_config32(), pci_read_config16(), pci_read_config8(), pci_write_config16(), pcidev_on_root(), RCBA32, RCBA32_AND_OR, and RCBA32_OR.

Referenced by lpc_init().

|

static |

Definition at line 570 of file lpc.c.

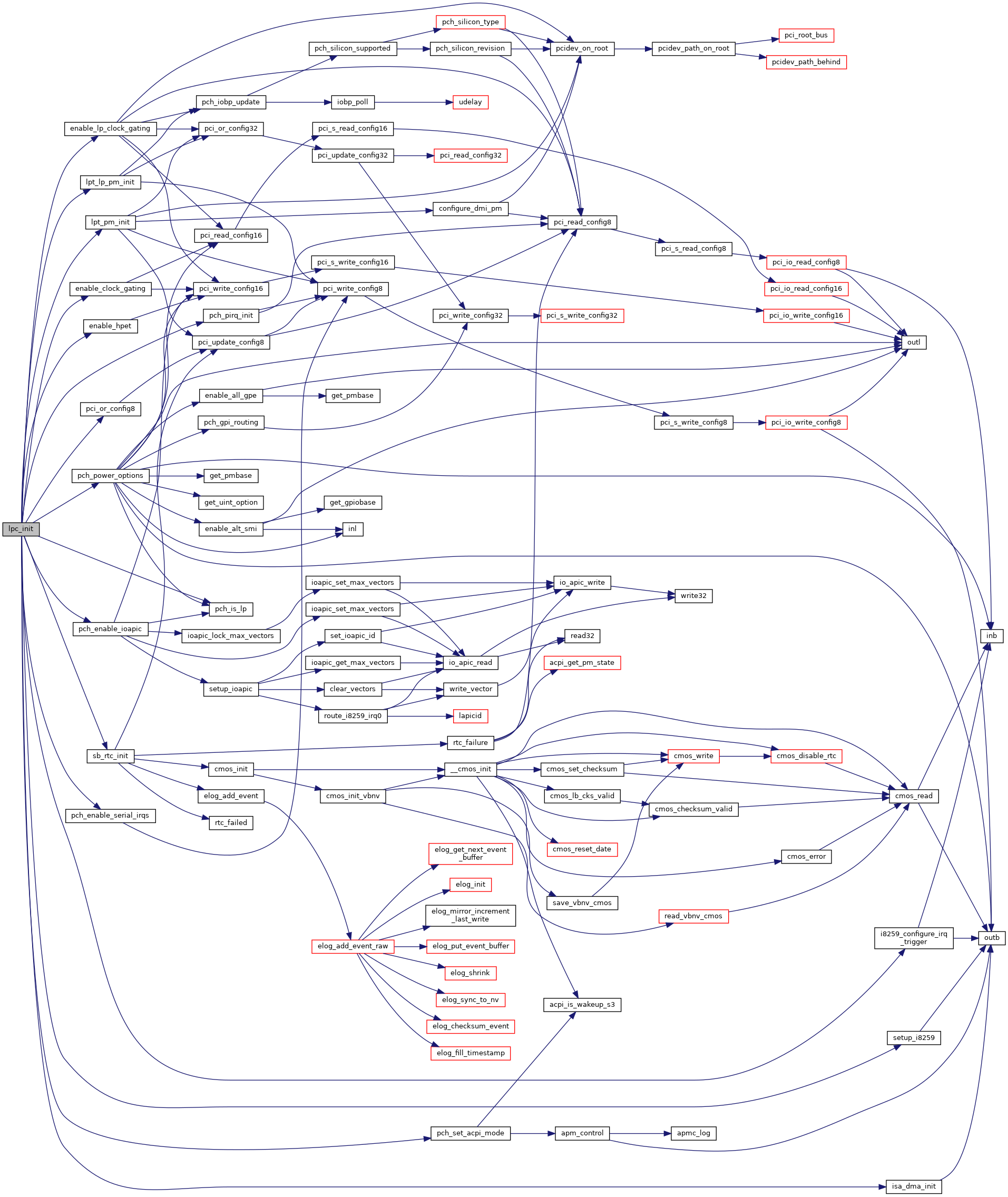

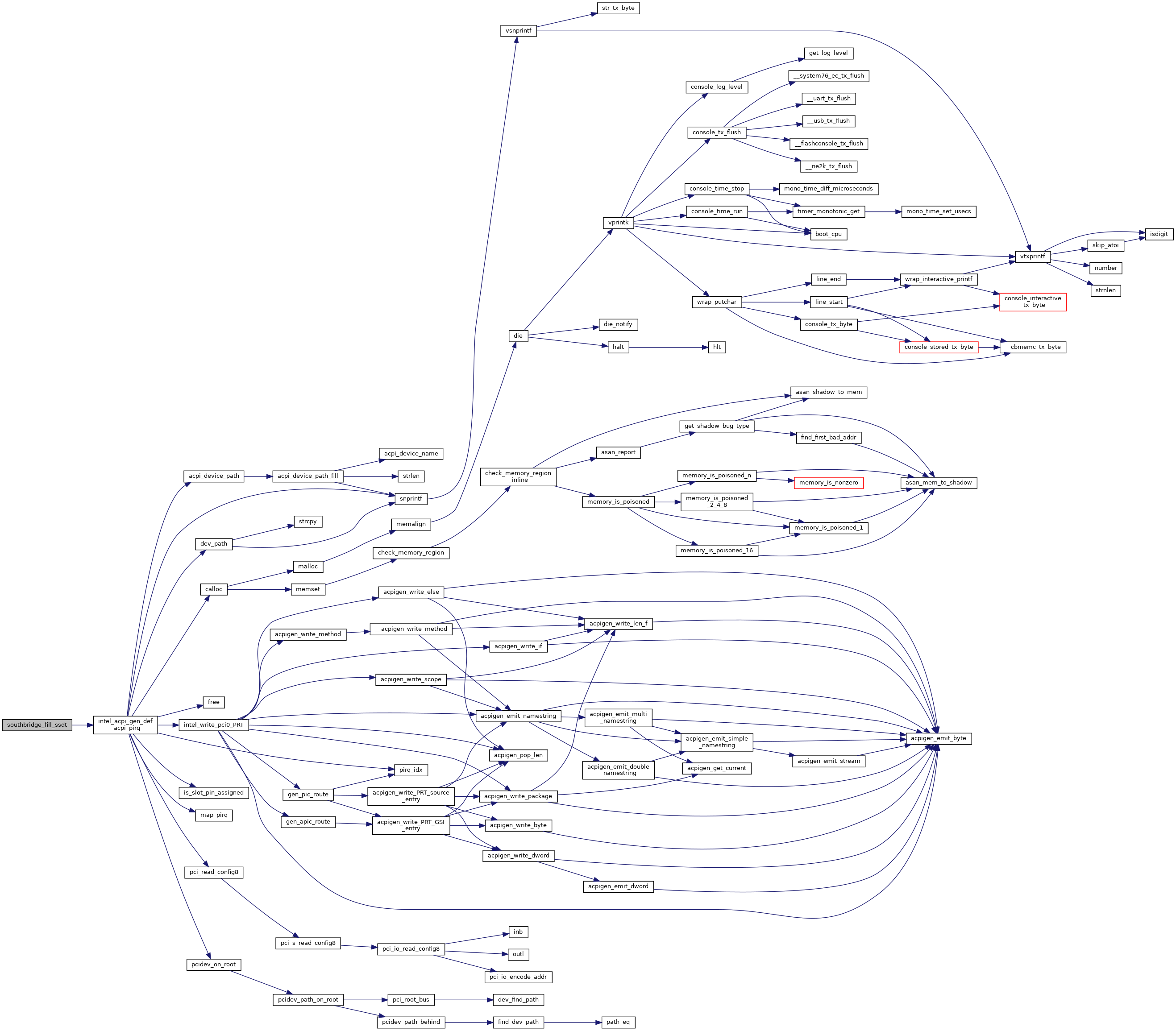

References BIOS_DEBUG, enable_clock_gating(), enable_hpet(), enable_lp_clock_gating(), GEN_PMCON_2, i8259_configure_irq_trigger(), isa_dma_init(), lpt_lp_pm_init(), lpt_pm_init(), pch_enable_ioapic(), pch_enable_serial_irqs(), pch_is_lp(), pch_pirq_init(), pch_power_options(), pch_set_acpi_mode(), pci_or_config8(), printk, sb_rtc_init(), and setup_i8259().

Definition at line 393 of file lpc.c.

References BIOS_DEBUG, device::chip_info, config, FD, PCH_DISABLE_ADSPD, pch_iobp_update(), pci_or_config32(), pci_write_config8(), printk, RCBA32, RCBA32_AND_OR, and RCBA32_OR.

Referenced by lpc_init().

Definition at line 309 of file lpc.c.

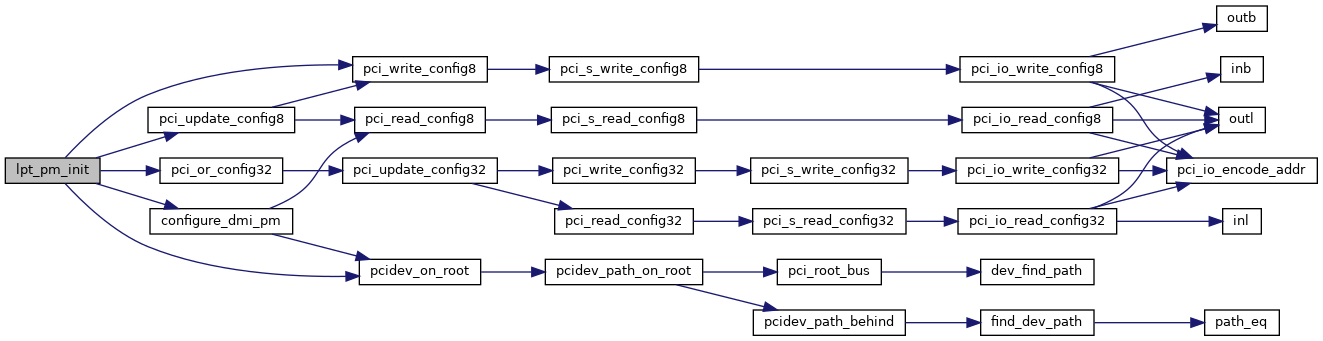

References BIOS_DEBUG, device::chip_info, config, configure_dmi_pm(), pci_or_config32(), pci_update_config8(), pci_write_config8(), pcidev_on_root(), PMIR, PMIR_CF9LOCK, printk, RCBA32, and RCBA32_OR.

Referenced by lpc_init().

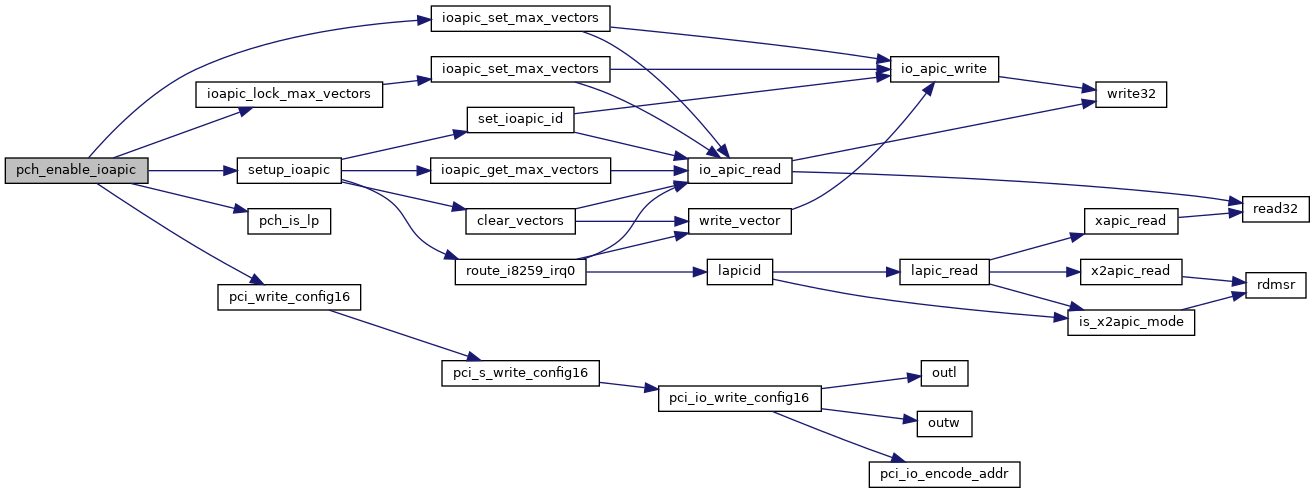

Set miscellaneous static southbridge features.

| dev | PCI device with I/O APIC control registers |

Definition at line 32 of file lpc.c.

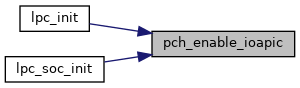

References ioapic_lock_max_vectors(), ioapic_set_max_vectors(), LPC_IBDF, PCH_IOAPIC_PCI_BUS, PCH_IOAPIC_PCI_SLOT, pch_is_lp(), pci_write_config16(), setup_ioapic(), and VIO_APIC_VADDR.

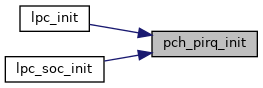

Referenced by lpc_init(), and lpc_soc_init().

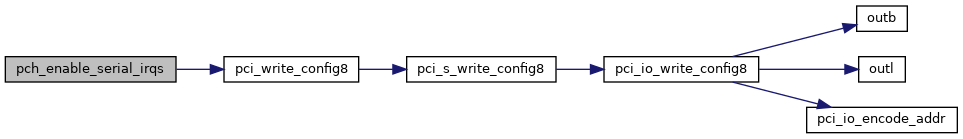

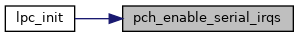

Definition at line 49 of file lpc.c.

References pci_write_config8(), and SERIRQ_CNTL.

Referenced by lpc_init().

|

static |

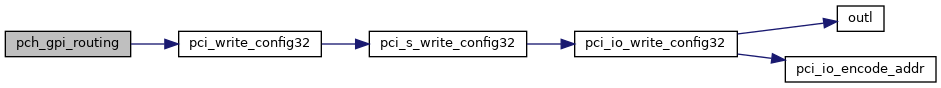

Definition at line 144 of file lpc.c.

References config, GPIO_ROUT, and pci_write_config32().

Referenced by pch_power_options().

|

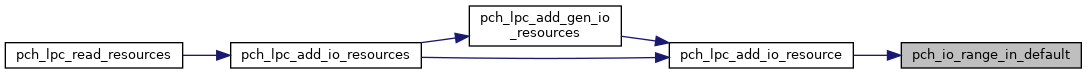

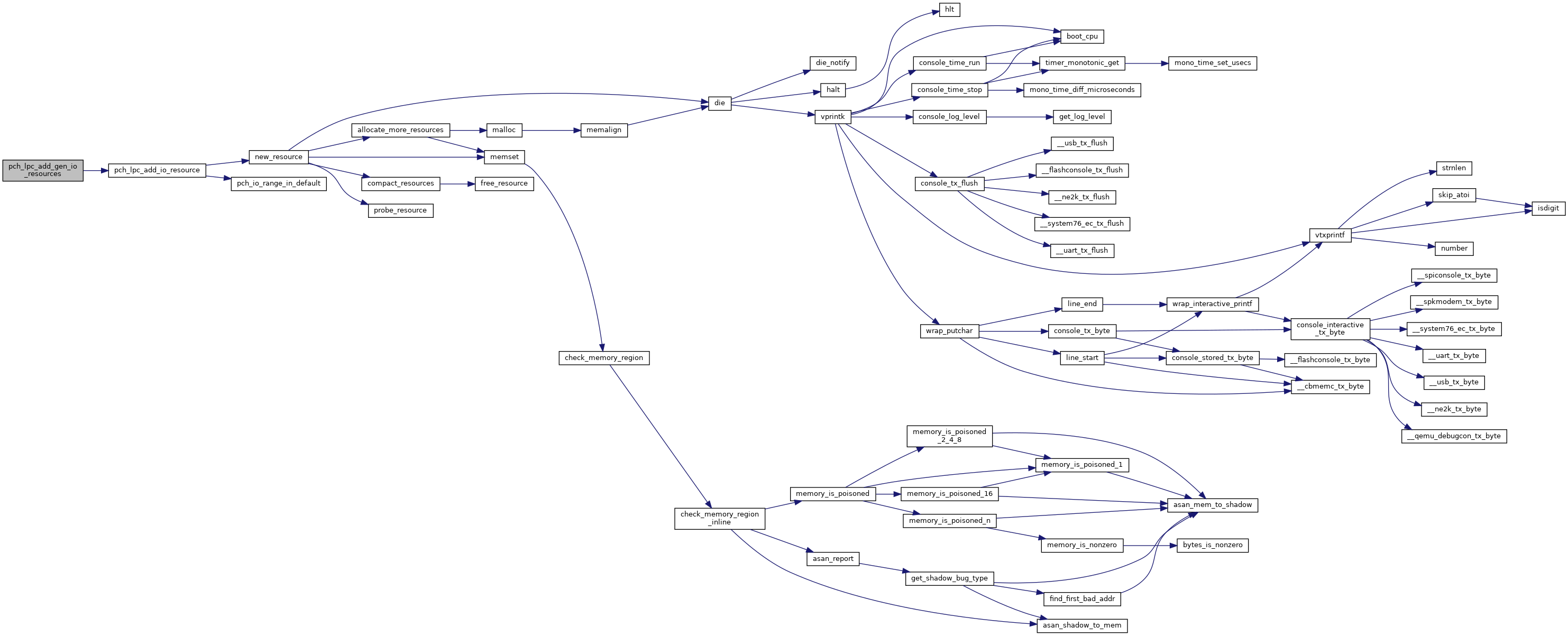

inlinestatic |

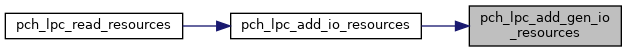

Definition at line 657 of file lpc.c.

References base, LPC_DEFAULT_IO_RANGE_LOWER, LPC_DEFAULT_IO_RANGE_UPPER, and resource::size.

Referenced by pch_lpc_add_io_resource().

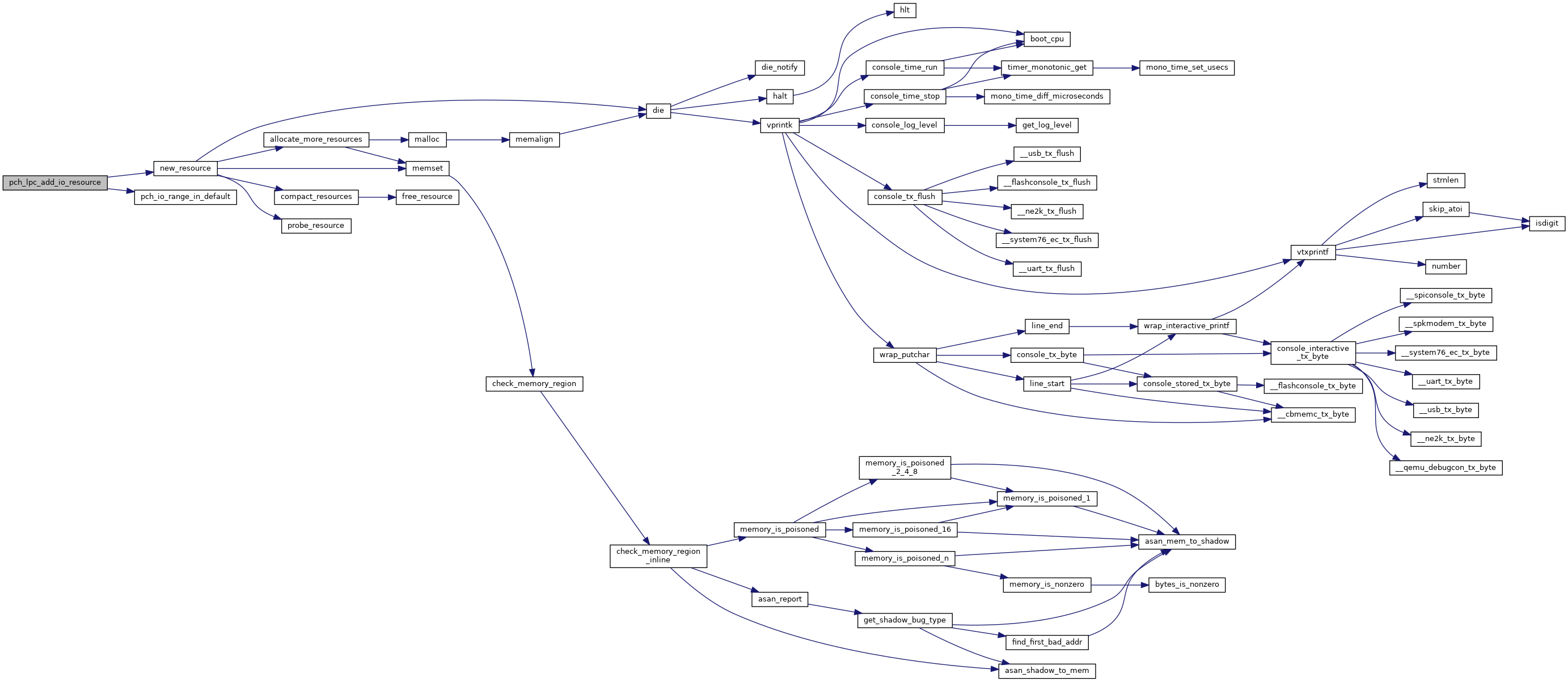

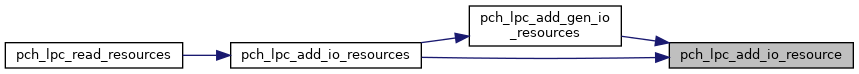

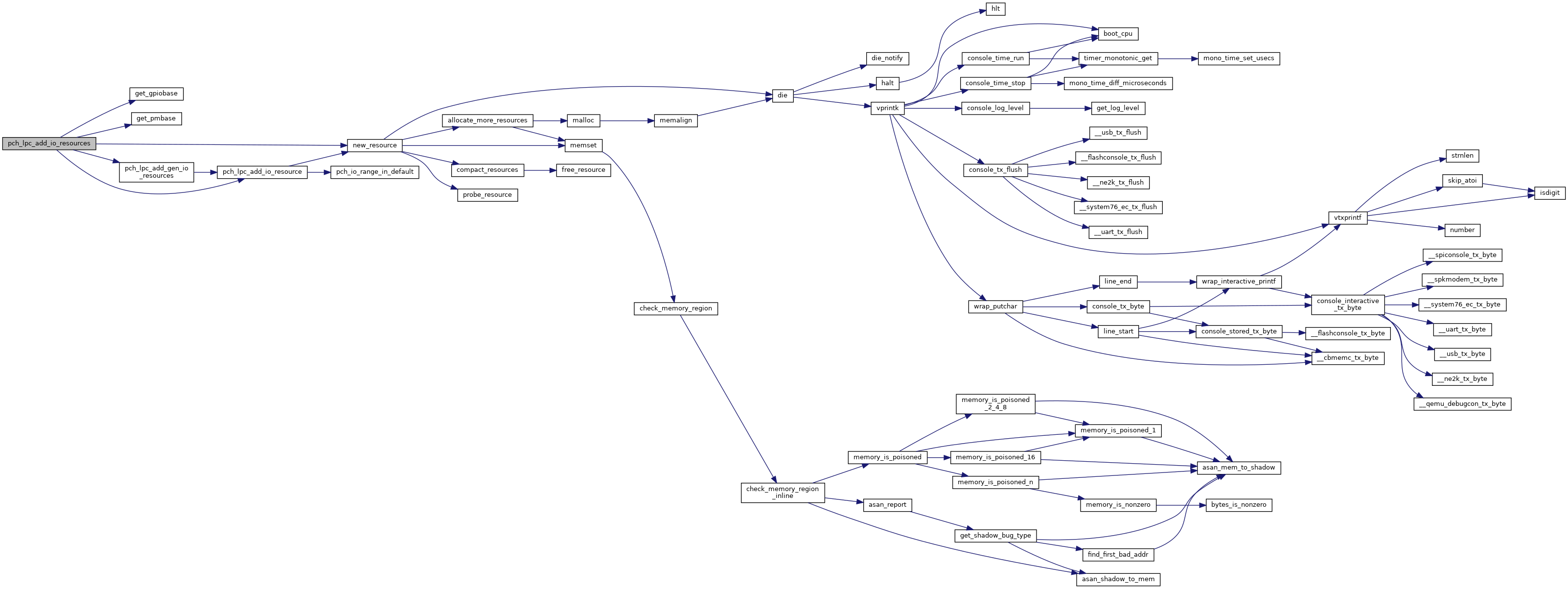

Definition at line 690 of file lpc.c.

References base, resource::index, pch_lpc_add_io_resource(), and resource::size.

Referenced by pch_lpc_add_io_resources().

Definition at line 676 of file lpc.c.

References resource::base, base, resource::flags, resource::index, IORESOURCE_ASSIGNED, IORESOURCE_FIXED, IORESOURCE_IO, new_resource(), pch_io_range_in_default(), and resource::size.

Referenced by pch_lpc_add_gen_io_resources(), and pch_lpc_add_io_resources().

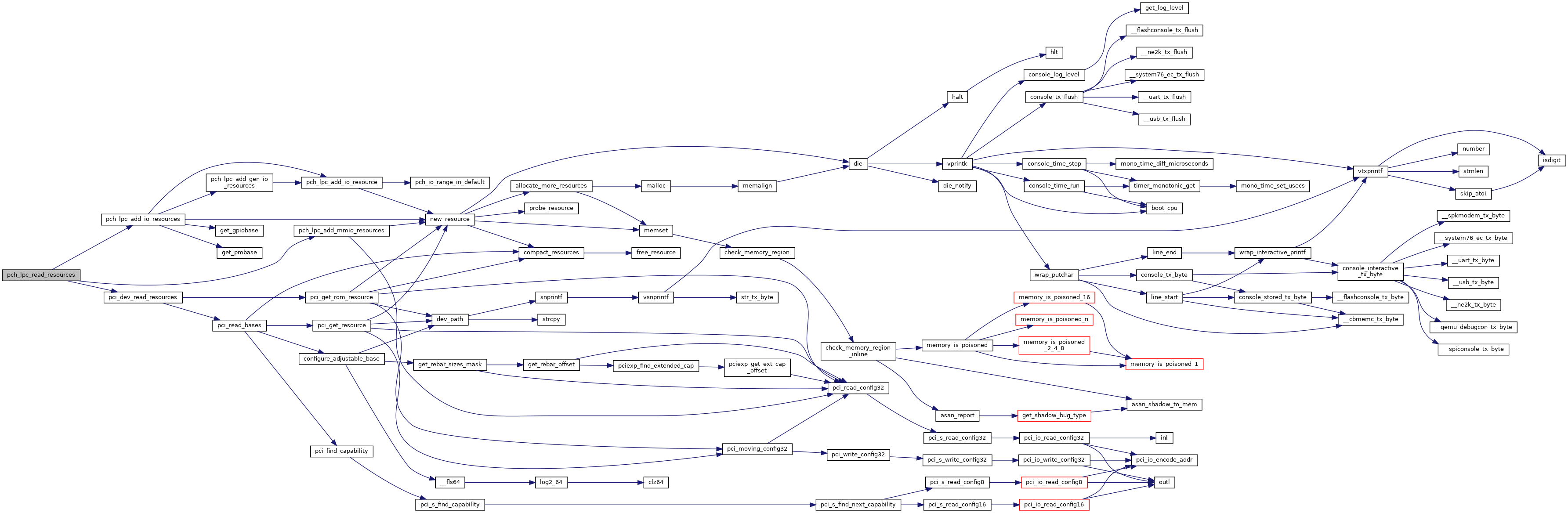

Definition at line 704 of file lpc.c.

References resource::base, device::chip_info, config, DEFAULT_GPIOSIZE, resource::flags, get_gpiobase(), get_pmbase(), GPIO_BASE, IORESOURCE_ASSIGNED, IORESOURCE_FIXED, IORESOURCE_IO, LPC_DEFAULT_IO_RANGE_LOWER, LPC_DEFAULT_IO_RANGE_UPPER, LPC_GEN1_DEC, LPC_GEN2_DEC, LPC_GEN3_DEC, LPC_GEN4_DEC, new_resource(), pch_lpc_add_gen_io_resources(), pch_lpc_add_io_resource(), PMBASE, and resource::size.

Referenced by pch_lpc_read_resources().

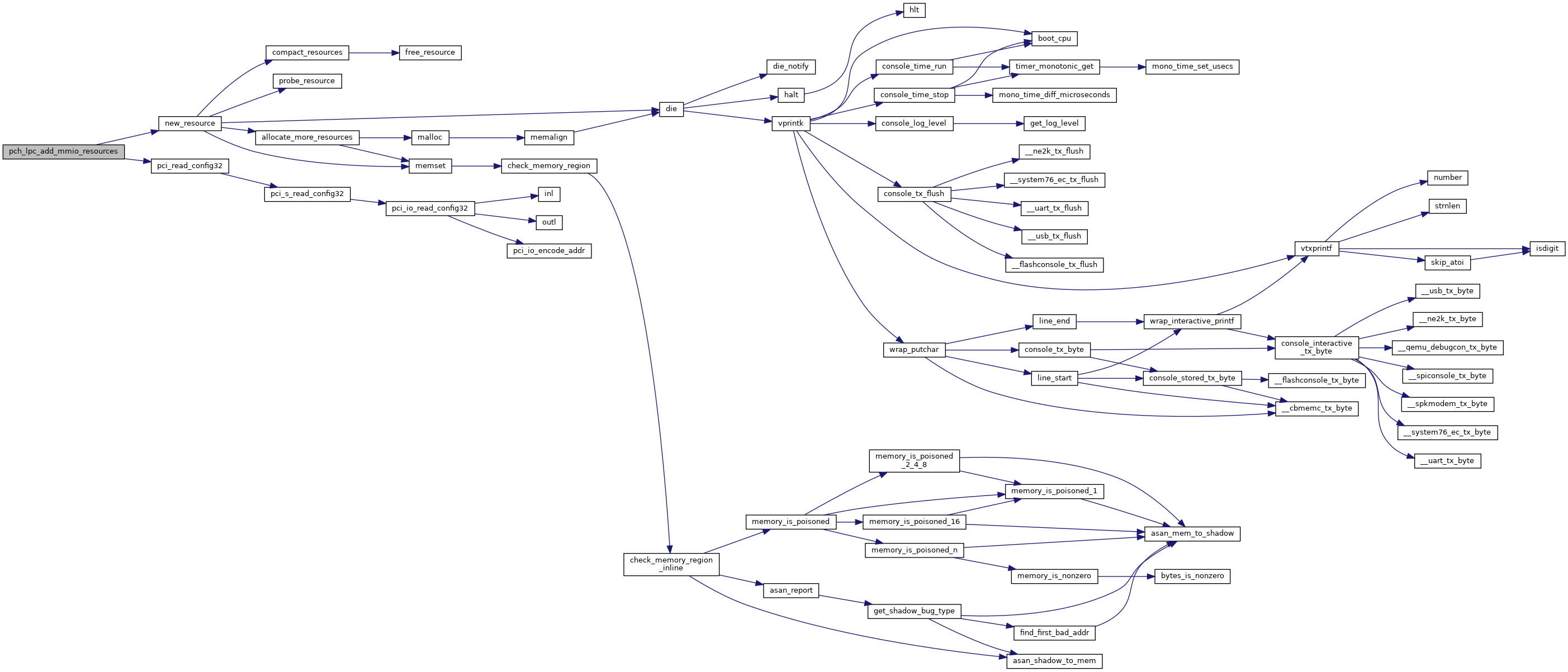

Definition at line 614 of file lpc.c.

References resource::base, resource::flags, IO_APIC_ADDR, IORESOURCE_ASSIGNED, IORESOURCE_FIXED, IORESOURCE_MEM, IORESOURCE_RESERVE, LGMR, new_resource(), OIC, pci_read_config32(), RCBA, and resource::size.

Referenced by pch_lpc_read_resources().

Definition at line 742 of file lpc.c.

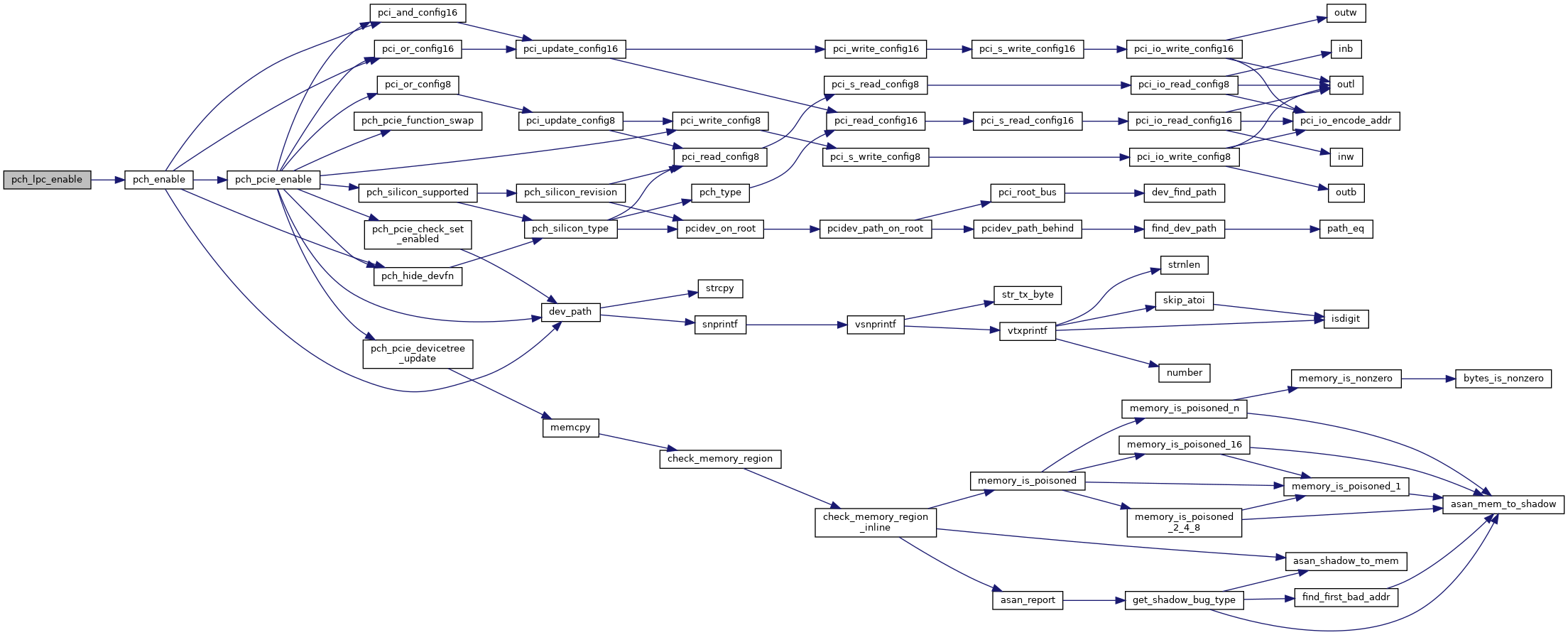

References DISPBDF, FD2, pch_enable(), PCH_ENABLE_DBDF, RCBA16, and RCBA32_OR.

Definition at line 730 of file lpc.c.

References pch_lpc_add_io_resources(), pch_lpc_add_mmio_resources(), and pci_dev_read_resources().

Definition at line 100 of file lpc.c.

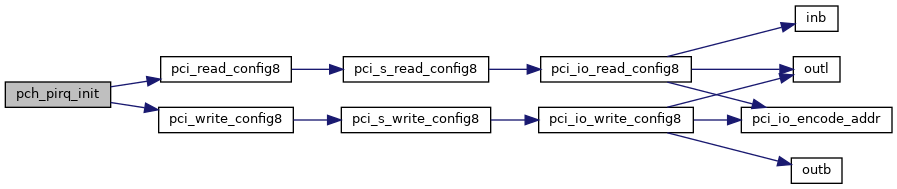

References all_devices, DEVICE_PATH_PCI, device::enabled, device::next, device::path, PCI_INTERRUPT_LINE, PCI_INTERRUPT_PIN, pci_read_config8(), pci_write_config8(), PIRQA_ROUT, PIRQB_ROUT, PIRQC_ROUT, PIRQD_ROUT, PIRQE_ROUT, PIRQF_ROUT, PIRQG_ROUT, PIRQH_ROUT, and device_path::type.

Referenced by lpc_init(), and lpc_soc_init().

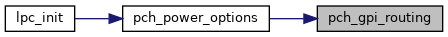

Definition at line 172 of file lpc.c.

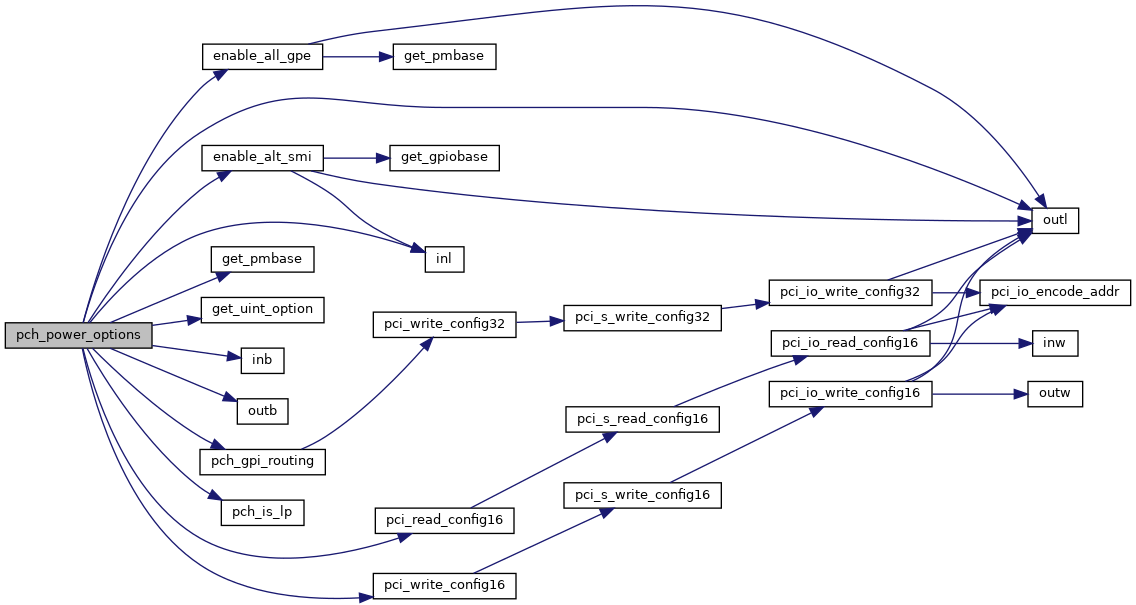

References BIOS_INFO, device::chip_info, config, enable_all_gpe(), enable_alt_smi(), GEN_PMCON_1, GEN_PMCON_3, get_pmbase(), get_uint_option(), inb(), inl(), MAINBOARD_POWER_KEEP, MAINBOARD_POWER_OFF, MAINBOARD_POWER_ON, NMI_OFF, outb(), outl(), pch_gpi_routing(), pch_is_lp(), pci_read_config16(), pci_write_config16(), pmbase, printk, RCBA16, and RCBA32.

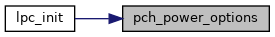

Referenced by lpc_init().

Definition at line 564 of file lpc.c.

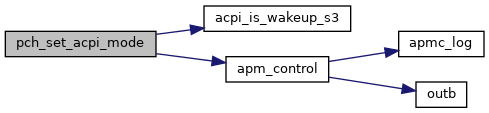

References acpi_is_wakeup_s3(), APM_CNT_ACPI_DISABLE, and apm_control().

Referenced by lpc_init().

Definition at line 756 of file lpc.c.

References intel_acpi_gen_def_acpi_pirq().

|

static |

Definition at line 761 of file lpc.c.

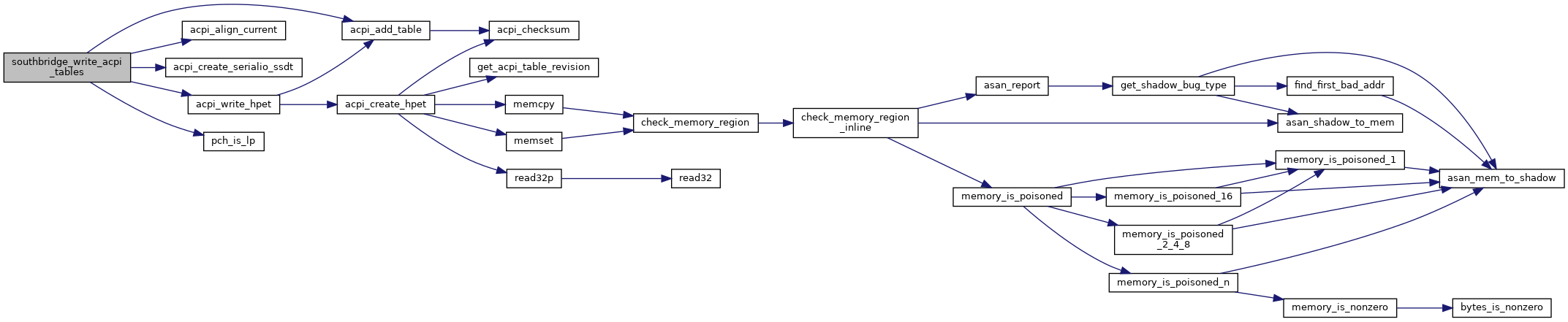

References acpi_add_table(), acpi_align_current(), acpi_create_serialio_ssdt(), acpi_write_hpet(), BIOS_DEBUG, acpi_table_header::length, pch_is_lp(), and printk.

|

static |

|

static |

|

static |