|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

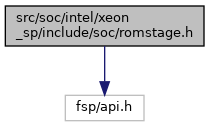

#include <fsp/api.h>

Go to the source code of this file.

Functions | |

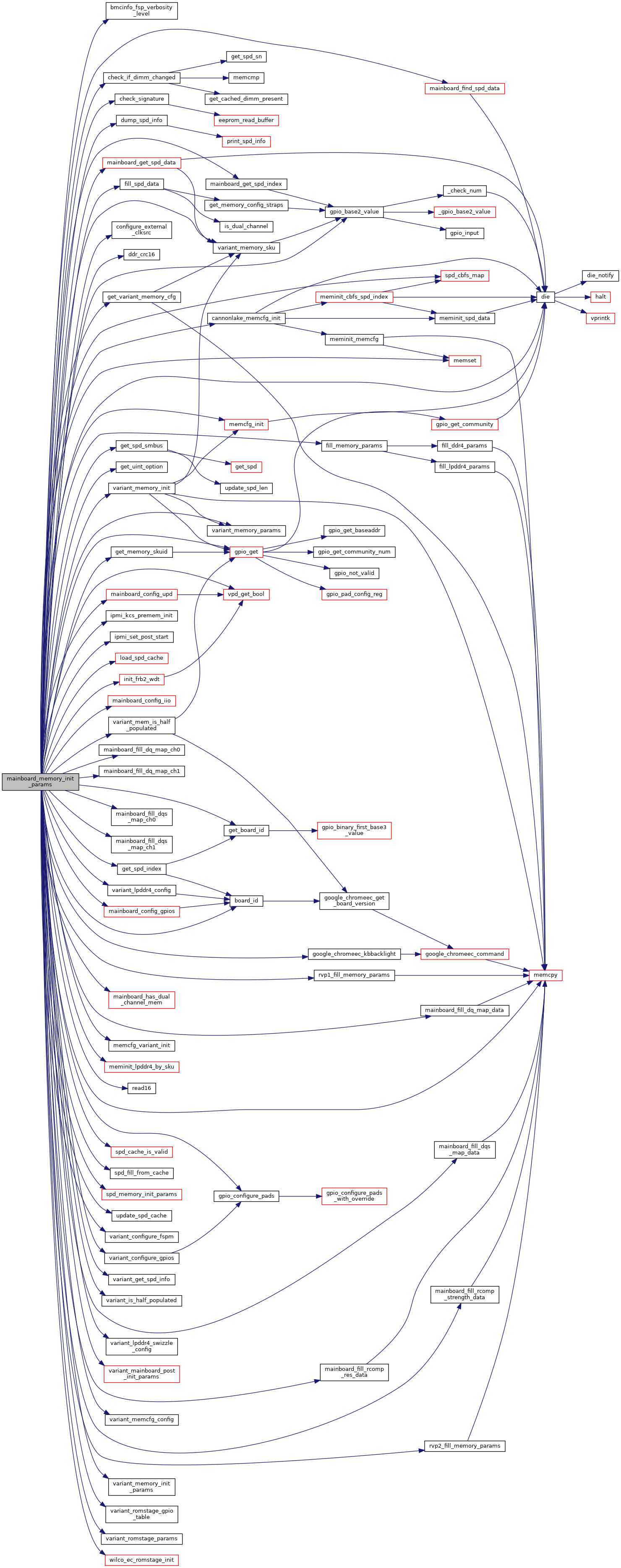

| void | mainboard_memory_init_params (FSPM_UPD *mupd) |

| void | mainboard_rtc_failed (void) |

| void | save_dimm_info (void) |

| void mainboard_memory_init_params | ( | FSPM_UPD * | mupd | ) |

Definition at line 22 of file romstage.c.

References spd_block::addr_map, ADL_M_LP4, ADL_M_LP5, ADL_N_LP5, ADL_P_DDR4_1, ADL_P_DDR4_2, ADL_P_DDR5_1, ADL_P_DDR5_2, ADL_P_LP4_1, ADL_P_LP4_2, ADL_P_LP5_1, ADL_P_LP5_2, ARRAY_SIZE, assert, baseboard_mem_cfg, BIOS_DEBUG, BIOS_ERR, BIOS_INFO, BIOS_SPEW, BIOS_WARNING, bmcinfo_fsp_verbosity_level(), board_cfg, board_id(), BOARD_ID_KBL_RVP11, BOARD_ID_KBL_RVP8, board_memcfg, BOARD_TYPE_MOBILE, BOARD_TYPE_SERVER, cannonlake_memcfg_init(), CB_ERR, CB_SUCCESS, Ch0_Bit_swizzling, ch0_bit_swizzling, Ch1_Bit_swizzling, ch1_bit_swizzling, Ch2_Bit_swizzling, ch2_bit_swizzling, Ch3_Bit_swizzling, ch3_bit_swizzling, check_if_dimm_changed(), check_signature(), config, CONFIG, configure_external_clksrc(), ddr5_mem_config, ddr_crc16(), die(), DQ_BITS_PER_DQS, dq_map, memory_params::dq_map, memory_params::dq_map_size, cnl_mb_cfg::dq_pins_interleaved, lpddr4_chan_swizzle_cfg::dqs, dqs_map, memory_params::dqs_map, memory_params::dqs_map_size, dump_spd_info(), memory_params::enable_sa_oc_support, fill_memory_params(), fill_spd_data(), FSP_BOOT_ON_S3_RESUME, FSP_M_CONFIG, get_board_id(), get_memory_skuid(), get_spd_index(), get_spd_smbus(), get_uint_option(), get_variant_memory_cfg(), google_chromeec_kbbacklight(), gpio_base2_value(), gpio_configure_pads(), gpio_get(), GPIO_MEM_CH_SEL, GPIO_MEM_CONFIG_0, GPIO_MEM_CONFIG_1, GPIO_MEM_CONFIG_2, GPIO_MEM_CONFIG_3, gpio_table, init_frb2_wdt(), ipmi_kcs_premem_init(), ipmi_set_post_start(), jsl_ddr4, jsl_lpddr4, spd_block::len, load_spd_cache(), LP4_DQS0, LP4_DQS1, LP4_DQS2, LP4_DQS3, LP4_PHYS_CH0A, LP4_PHYS_CH0B, LP4_PHYS_CH1A, LP4_PHYS_CH1B, mainboard_config_gpios(), mainboard_config_iio(), mainboard_config_upd(), mainboard_fill_dq_map_ch0(), mainboard_fill_dq_map_ch1(), mainboard_fill_dq_map_data(), mainboard_fill_dqs_map_ch0(), mainboard_fill_dqs_map_ch1(), mainboard_fill_dqs_map_data(), mainboard_fill_rcomp_res_data(), mainboard_fill_rcomp_strength_data(), mainboard_find_spd_data(), mainboard_get_spd_data(), mainboard_get_spd_index(), mainboard_has_dual_channel_mem(), mem_config, MEM_TOPO_DIMM_MODULE, MEM_TOPO_MEMORY_DOWN, MEM_TOPO_MIXED, MEM_TRAIN_FORCE, MEM_TYPE_DDR4, memcfg, memcfg_init(), memcfg_variant_init(), memcpy(), meminit_lpddr4_by_sku(), MEMORY_COUNT, memset(), mMemoryDownConfig, NOT_EXISTING, NULL, offsetof, lpddr4_swizzle_cfg::phys, printk, cnl_mb_cfg::rcomp_resistor, rcomp_resistor, memory_params::rcomp_resistor, memory_params::rcomp_resistor_size, rcomp_resistors, rcomp_target, memory_params::rcomp_target, memory_params::rcomp_target_size, rcomp_targets, read16(), READ_EEPROM_FSP_M, READ_SMBUS, READ_SPD_CBFS, READ_SPD_MEMPTR, spd_info::read_type, rvp1_fill_memory_params(), rvp2_fill_memory_params(), memory_params::sa_voltage_offset_val, memory_params::single_channel, cnl_mb_cfg::spd, SPD_4X_2GB, SPD_4X_4GB, spd_block::spd_array, spd_cache_is_valid(), spd_cbfs_map(), spd_data, spd_by_pointer::spd_data_len, spd_by_pointer::spd_data_ptr, spd_info::spd_data_by::spd_data_ptr_info, spd_fill_from_cache(), spd_index, spd_info::spd_data_by::spd_index, SPD_LEN, spd_memory_init_params(), spd_info::spd_data_by::spd_smbus_address, spd_info::spd_spec, mem_spd::topo, memory_params::type, mb_cfg::type, update_spd_cache(), memory_params::use_sec_spd, val, variant_configure_fspm(), variant_configure_gpios(), variant_get_spd_info(), variant_is_half_populated(), variant_lpddr4_config(), variant_lpddr4_swizzle_config(), variant_mainboard_post_init_params(), variant_mem_is_half_populated(), variant_memcfg_config(), variant_memory_init(), variant_memory_init_params(), variant_memory_params(), variant_memory_sku(), variant_romstage_gpio_table(), variant_romstage_params(), vpd_get_bool(), VPD_RW_THEN_RO, cnl_mb_cfg::vref_ca_config, and wilco_ec_romstage_init().

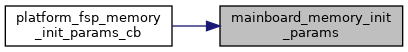

Referenced by platform_fsp_memory_init_params_cb().

Definition at line 209 of file romstage.c.

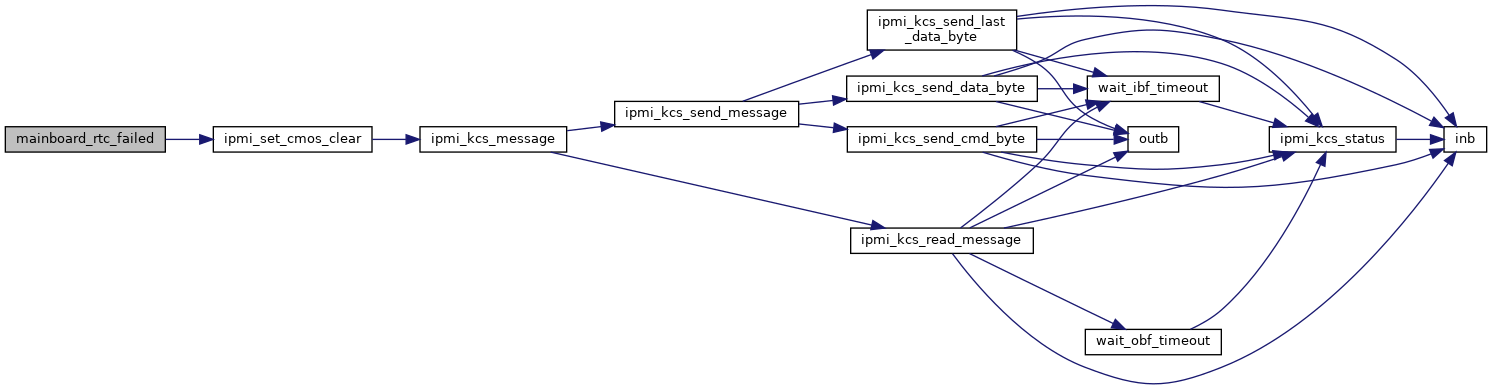

References BIOS_DEBUG, BIOS_ERR, CB_SUCCESS, ipmi_set_cmos_clear(), and printk.

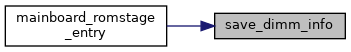

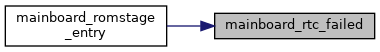

Referenced by mainboard_romstage_entry().

Definition at line 78 of file romstage.c.

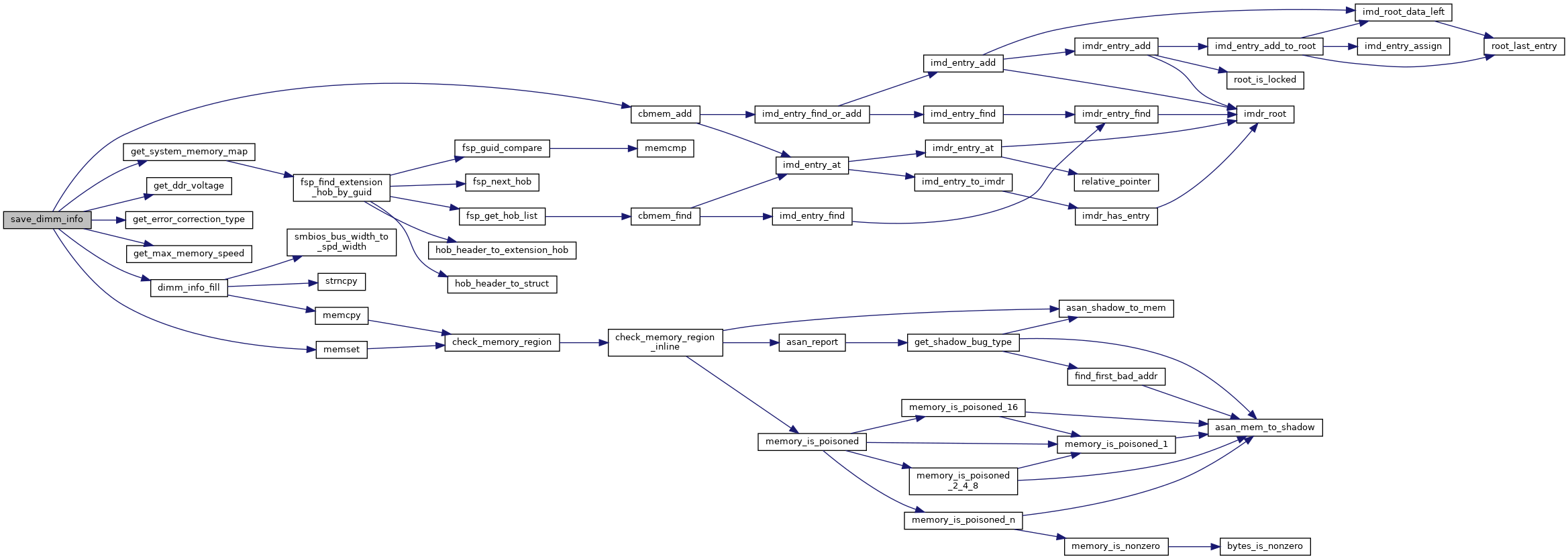

References ARRAY_SIZE, assert, BIOS_DEBUG, BIOS_ERR, BIOS_WARNING, cbmem_add(), CBMEM_ID_MEMINFO, ch, dimm_info::configured_speed_mts, memory_info::dimm, memory_info::dimm_cnt, dimm_info_fill(), memory_info::ecc_type, get_ddr_voltage(), get_error_correction_type(), get_max_memory_speed(), get_system_memory_map(), memory_info::max_capacity_mib, dimm_info::max_speed_mts, memset(), MiB, NULL, memory_info::number_of_devices, and printk.

Referenced by mainboard_romstage_entry().