|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

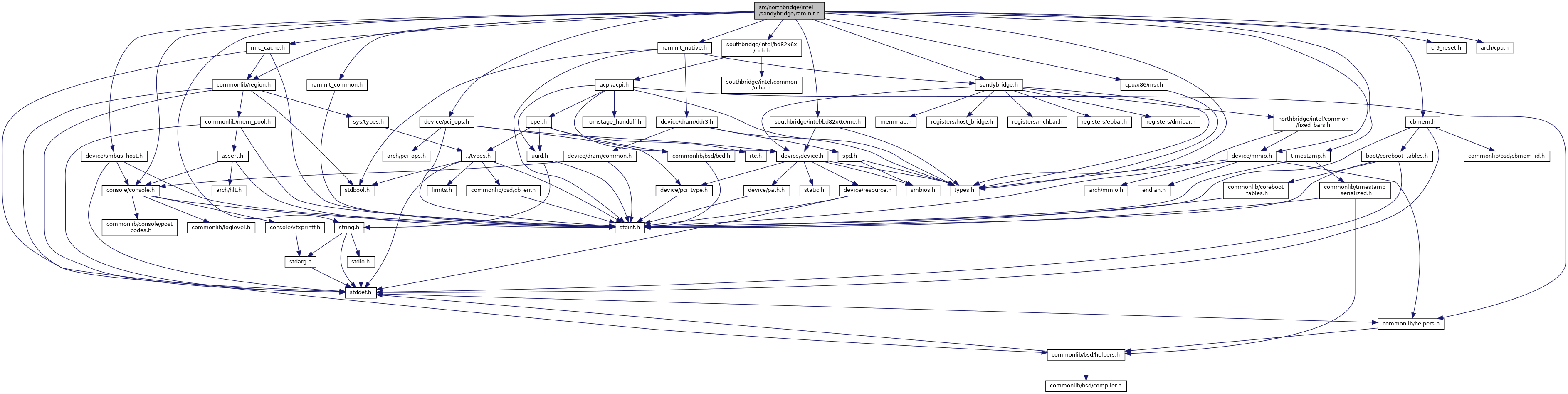

#include <console/console.h>#include <commonlib/region.h>#include <cf9_reset.h>#include <string.h>#include <arch/cpu.h>#include <device/mmio.h>#include <device/pci_ops.h>#include <device/smbus_host.h>#include <cbmem.h>#include <timestamp.h>#include <mrc_cache.h>#include <southbridge/intel/bd82x6x/me.h>#include <southbridge/intel/bd82x6x/pch.h>#include <cpu/x86/msr.h>#include <types.h>#include "raminit_native.h"#include "raminit_common.h"#include "sandybridge.h"

Go to the source code of this file.

Functions | |

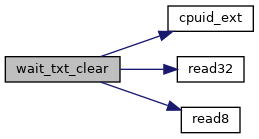

| static void | wait_txt_clear (void) |

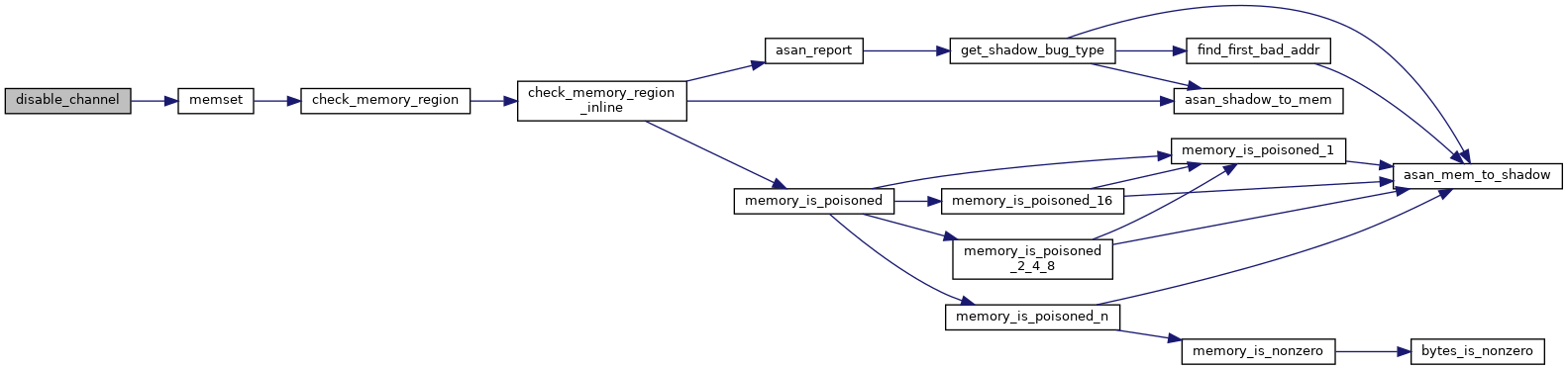

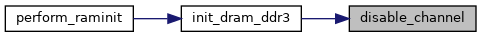

| static void | disable_channel (ramctr_timing *ctrl, int channel) |

| static uint8_t | nb_get_ecc_type (const uint32_t capid0_a) |

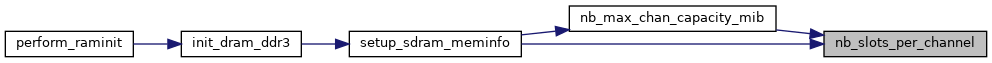

| static uint16_t | nb_slots_per_channel (const uint32_t capid0_a) |

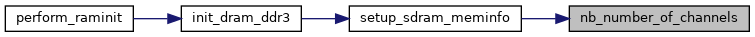

| static uint16_t | nb_number_of_channels (const uint32_t capid0_a) |

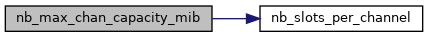

| static uint32_t | nb_max_chan_capacity_mib (const uint32_t capid0_a) |

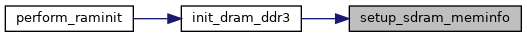

| static void | setup_sdram_meminfo (ramctr_timing *ctrl) |

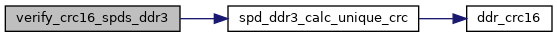

| static int | verify_crc16_spds_ddr3 (spd_raw_data *spd, ramctr_timing *ctrl) |

| void | read_spd (spd_raw_data *spd, u8 addr, bool id_only) |

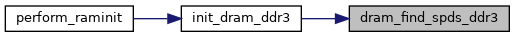

| static void | dram_find_spds_ddr3 (spd_raw_data *spd, ramctr_timing *ctrl) |

| static void | save_timings (ramctr_timing *ctrl) |

| static void | reinit_ctrl (ramctr_timing *ctrl, const u32 cpuid) |

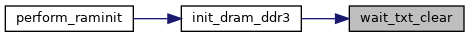

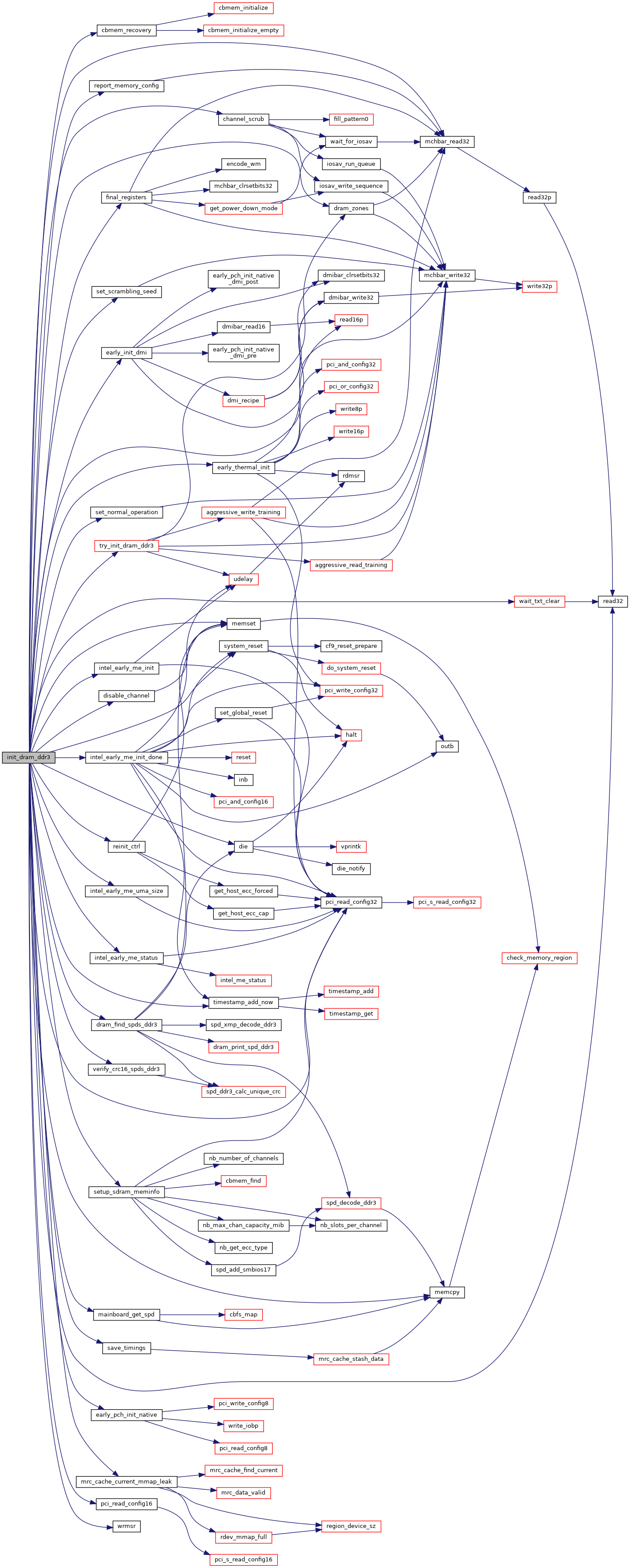

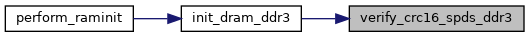

| static void | init_dram_ddr3 (int s3resume, const u32 cpuid) |

| void | perform_raminit (int s3resume) |

|

static |

Definition at line 43 of file raminit.c.

References ramctr_timing_st::channel_size_mb, ramctr_timing_st::cmd_stretch, ramctr_timing_st::info, ramctr_timing_st::mad_dimm, memset(), ramctr_timing_st::rank_mirror, ramctr_timing_st::rankmap, and ramctr_timing_st::timings.

Referenced by init_dram_ddr3().

|

static |

Definition at line 150 of file raminit.c.

References dimm_flags_ddr3_st::asr, ramctr_timing_st::auto_self_refresh, BIOS_DEBUG, BIOS_WARNING, ramctr_timing_st::channel_size_mb, CONFIG, DDR3_XMP_PROFILE_1, die(), dimm_attr_ddr3_st::dimms_per_channel, dram_print_spd_ddr3(), dimm_attr_ddr3_st::dram_type, ramctr_timing_st::ecc_enabled, ramctr_timing_st::ecc_forced, ramctr_timing_st::ecc_supported, dimm_flags_ddr3_st::ext_temp_refresh, ramctr_timing_st::extended_temperature_range, dimm_attr_ddr3_st::flags, FOR_ALL_CHANNELS, ramctr_timing_st::info, dimm_flags_ddr3_st::is_ecc, ramctr_timing_st::lanes, memset(), NUM_SLOTS, dimm_flags_ddr3_st::pins_mirrored, printk, printram, ramctr_timing_st::rank_mirror, ramctr_timing_st::rankmap, dimm_attr_ddr3_st::ranks, ramctr_timing_st::ref_card_offset, dimm_attr_ddr3_st::size_mb, ramctr_timing_st::spd_crc, spd_ddr3_calc_unique_crc(), spd_decode_ddr3(), SPD_MEMORY_TYPE, SPD_MEMORY_TYPE_SDRAM_DDR3, spd_xmp_decode_ddr3(), and dimm_attr_ddr3_st::voltage.

Referenced by init_dram_ddr3().

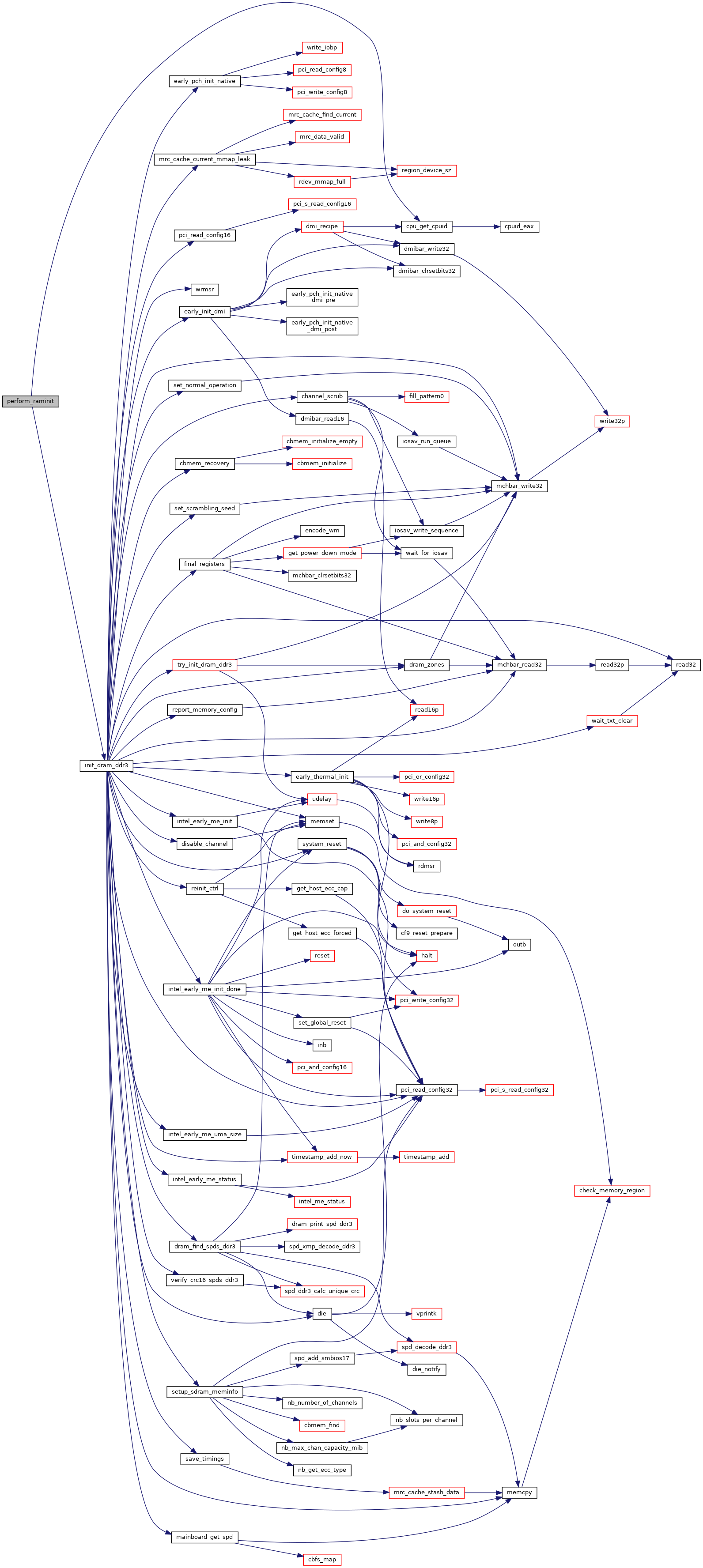

Definition at line 293 of file raminit.c.

References addr, BIOS_ALERT, BIOS_DEBUG, BIOS_ERR, BIOS_INFO, BIOS_NOTICE, cbmem_recovery(), CHANNEL_HASH, channel_scrub(), CONFIG, ramctr_timing_st::cpu, cpuid, die(), disable_channel(), dram_find_spds_ddr3(), dram_zones(), early_init_dmi(), early_pch_init_native(), early_thermal_init(), ramctr_timing_st::ecc_enabled, ramctr_timing_st::ecc_forced, ramctr_timing_st::ecc_supported, final_registers(), GET_ERR_CHANNEL, HOST_BRIDGE, intel_early_me_init(), intel_early_me_init_done(), intel_early_me_status(), intel_early_me_uma_size(), mainboard_get_spd(), mchbar_read32(), mchbar_setbits32, mchbar_write32(), ME_INIT_STATUS_SUCCESS, memcpy(), memset(), MiB, mrc_cache_current_mmap_leak(), MRC_CACHE_VERSION, MRC_TRAINING_DATA, NULL, pci_read_config16(), pci_read_config32(), printk, printram, read32(), reinit_ctrl(), report_memory_config(), SAPMCTL, save_timings(), set_normal_operation(), set_scrambling_seed(), setup_sdram_meminfo(), SOUTHBRIDGE, SSKPD, system_reset(), timestamp_add_now(), try_init_dram_ddr3(), TS_INITRAM_END, TS_INITRAM_START, TSEGMB, verify_crc16_spds_ddr3(), wait_txt_clear(), and wrmsr().

Referenced by perform_raminit().

Definition at line 56 of file raminit.c.

References CAPID_ECCDIS, MEMORY_ARRAY_ECC_NONE, and MEMORY_ARRAY_ECC_SINGLE_BIT.

Referenced by setup_sdram_meminfo().

Definition at line 71 of file raminit.c.

References CAPID_DDRSZ, and nb_slots_per_channel().

Referenced by setup_sdram_meminfo().

Definition at line 66 of file raminit.c.

References CAPID_PDCD.

Referenced by setup_sdram_meminfo().

Definition at line 61 of file raminit.c.

References CAPID_DDPCD.

Referenced by nb_max_chan_capacity_mib(), and setup_sdram_meminfo().

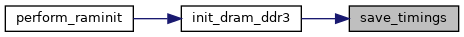

| void perform_raminit | ( | int | s3resume | ) |

Definition at line 477 of file raminit.c.

References cpu_get_cpuid(), init_dram_ddr3(), and post_code.

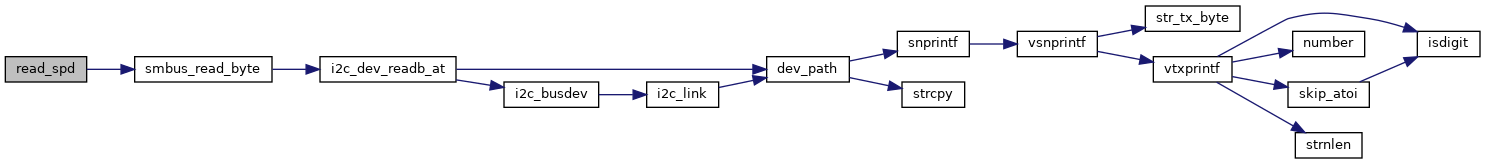

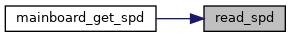

| void read_spd | ( | spd_raw_data * | spd, |

| u8 | addr, | ||

| bool | id_only | ||

| ) |

Definition at line 138 of file raminit.c.

References addr, and smbus_read_byte().

Referenced by mainboard_get_spd().

|

static |

Definition at line 277 of file raminit.c.

References BIOS_DEBUG, ramctr_timing_st::cpu, cpuid, ramctr_timing_st::ecc_forced, ramctr_timing_st::ecc_supported, get_host_ecc_cap(), get_host_ecc_forced(), memset(), and printk.

Referenced by init_dram_ddr3().

|

static |

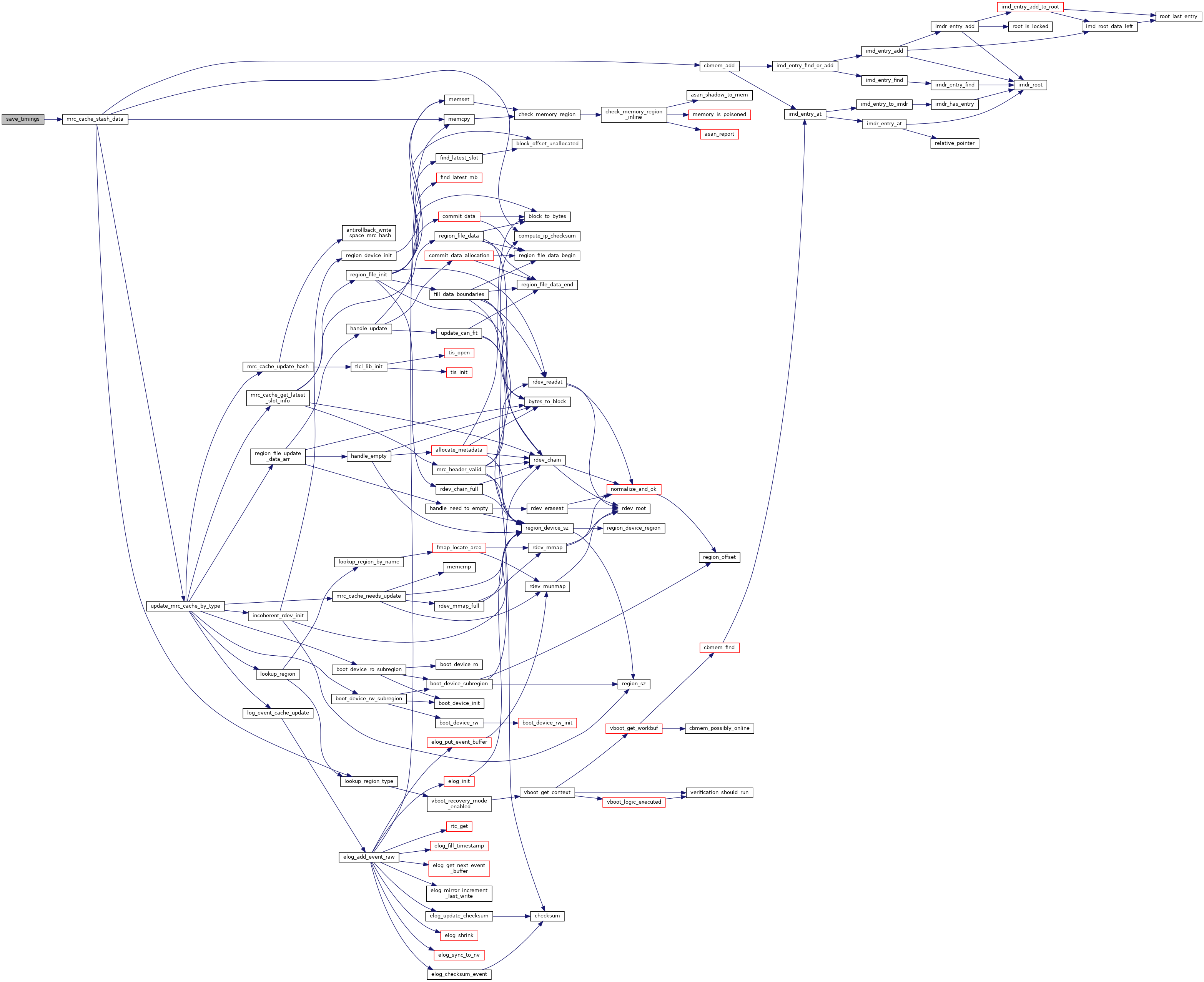

Definition at line 271 of file raminit.c.

References mrc_cache_stash_data(), MRC_CACHE_VERSION, and MRC_TRAINING_DATA.

Referenced by init_dram_ddr3().

|

static |

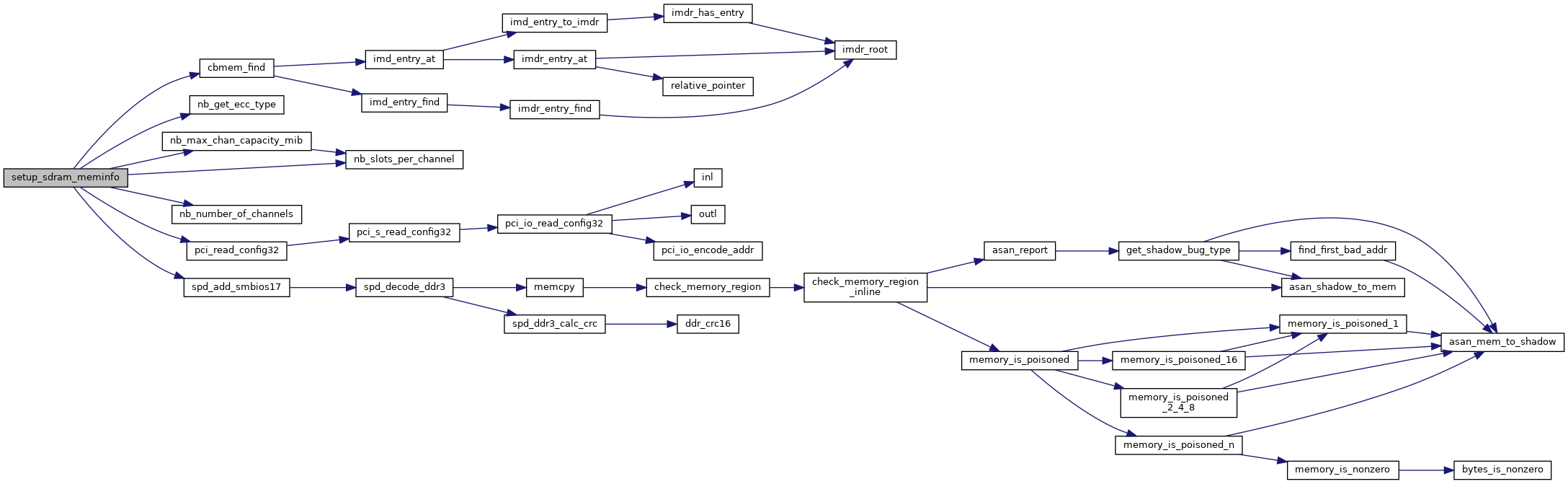

Definition at line 96 of file raminit.c.

References BIOS_ERR, CAPID0_A, CB_SUCCESS, cbmem_find(), CBMEM_ID_MEMINFO, FOR_ALL_CHANNELS, HOST_BRIDGE, ramctr_timing_st::info, m, nb_get_ecc_type(), nb_max_chan_capacity_mib(), nb_number_of_channels(), nb_slots_per_channel(), NULL, NUM_SLOTS, pci_read_config32(), printk, spd_add_smbios17(), and ramctr_timing_st::tCK.

Referenced by init_dram_ddr3().

|

static |

Definition at line 123 of file raminit.c.

References FOR_ALL_CHANNELS, NUM_SLOTS, ramctr_timing_st::spd_crc, and spd_ddr3_calc_unique_crc().

Referenced by init_dram_ddr3().

Definition at line 25 of file raminit.c.

References cpuid_ext(), cpuid_result::ecx, read32(), and read8().

Referenced by init_dram_ddr3().