|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

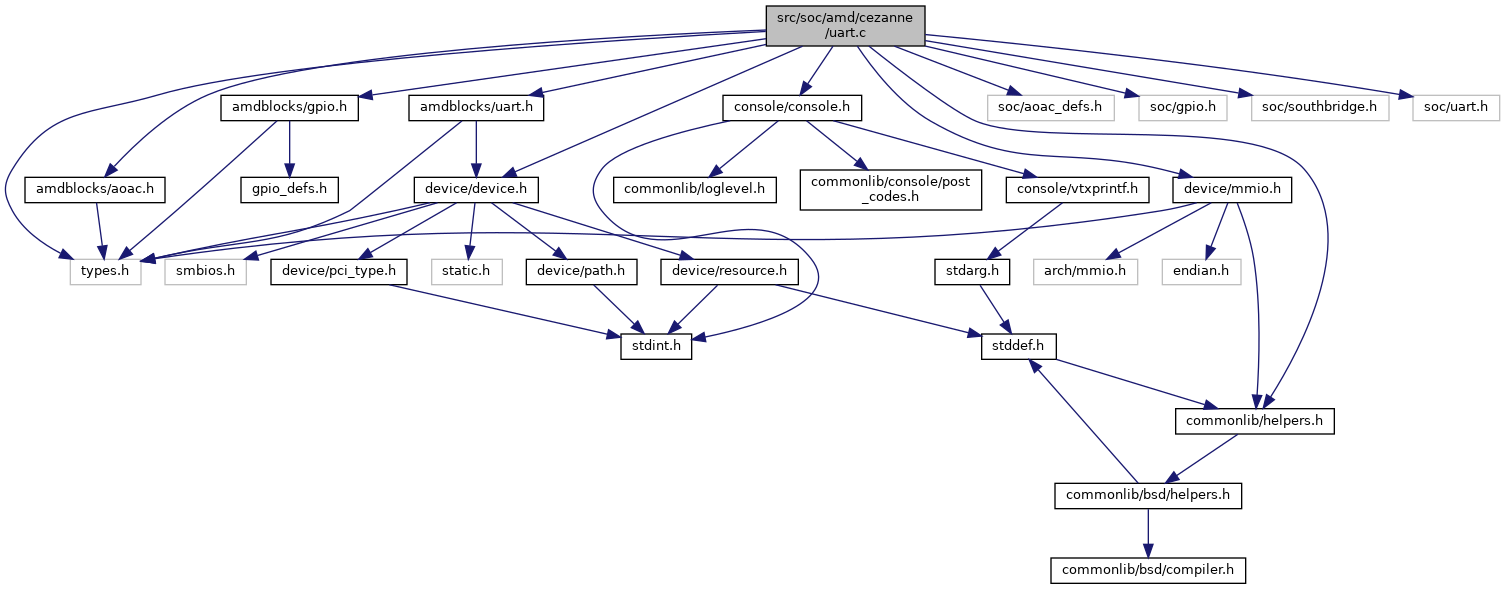

#include <amdblocks/aoac.h>#include <amdblocks/gpio.h>#include <amdblocks/uart.h>#include <commonlib/helpers.h>#include <console/console.h>#include <device/device.h>#include <device/mmio.h>#include <soc/aoac_defs.h>#include <soc/gpio.h>#include <soc/southbridge.h>#include <soc/uart.h>#include <types.h>

Go to the source code of this file.

Functions | |

| uintptr_t | get_uart_base (unsigned int idx) |

| void | clear_uart_legacy_config (void) |

| void | set_uart_config (unsigned int idx) |

| static const char * | uart_acpi_name (const struct device *dev) |

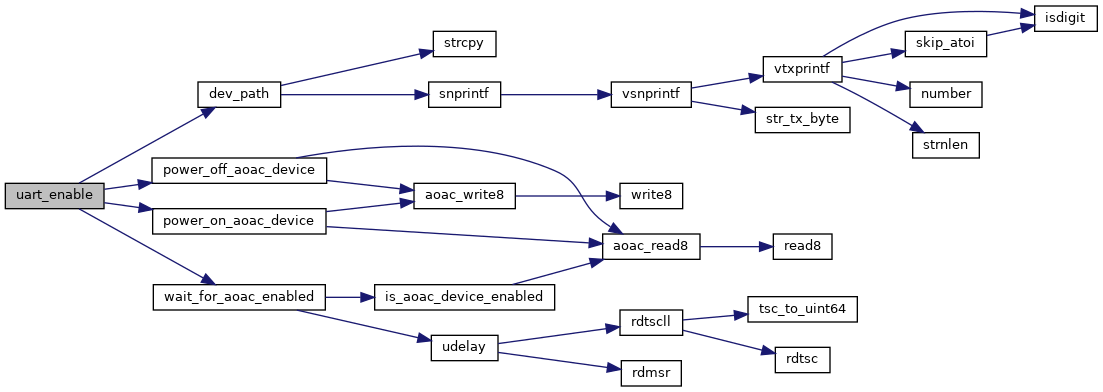

| static void | uart_enable (struct device *dev) |

| static void | uart_read_resources (struct device *dev) |

Variables | |

| struct { | |

| uintptr_t base | |

| struct soc_amd_gpio mux [2] | |

| } | uart_info [] |

| struct device_operations | cezanne_uart_mmio_ops |

Definition at line 30 of file uart.c.

References ARRAY_SIZE, and uart_info.

|

static |

Definition at line 51 of file uart.c.

References mmio_path::addr, APU_UART0_BASE, APU_UART1_BASE, device_path::mmio, NULL, and device::path.

Definition at line 64 of file uart.c.

References mmio_path::addr, APU_UART0_BASE, APU_UART1_BASE, BIOS_ERR, dev_id, dev_path(), device::enabled, FCH_AOAC_DEV_UART0, FCH_AOAC_DEV_UART1, device_path::mmio, device::path, power_off_aoac_device(), power_on_aoac_device(), printk, and wait_for_aoac_enabled().

| uintptr_t base |

Definition at line 17 of file uart.c.

Referenced by __allocate_resources(), __ubsan_handle_pointer_overflow(), _paging_identity_map_addr(), acpi_create_mcfg_mmconfig(), acpi_dmar_atsr_fixup(), acpi_dmar_drhd_fixup(), acpi_dmar_rmrr_fixup(), acpi_dmar_satc_fixup(), acpi_ssdt_write_cbtable(), acpigen_add_mainboard_rsvd_io(), acpigen_write_mem32fixed(), amd_initcpuio(), aspeed_early_config(), ast_get_index_reg(), ast_get_index_reg_mask(), ast_set_index_reg(), ast_set_index_reg_mask(), azalia_audio_init(), azalia_codec_init(), azalia_codecs_init(), azalia_enter_reset(), azalia_exit_reset(), azalia_init(), azalia_pch_init(), azalia_program_verb_table(), azalia_write_verb(), bios_mmap_init(), block_cmd_loop(), blsp_i2c_init(), bootmem_arch_add_ranges(), calc_var_mtrr_range(), car_stage_entry(), clock_sdram(), codec_detect(), complete_command(), compute_resources(), config_pllu(), configure_child_lpc_windows(), controller_read8(), controller_write8(), dapc_init(), data_fabric_set_mmio_np(), ddr3_read_io_init(), decode_sib_address(), disable_microphone(), do_action(), do_i2c_block_write(), do_i2c_eeprom_read(), do_smbus_block_read(), do_smbus_block_write(), do_smbus_process_call(), do_smbus_read_byte(), do_smbus_read_word(), do_smbus_write_byte(), do_smbus_write_word(), domain_read_resources(), dp_controller_init(), dt_adjust_all_phandles(), dt_fixup_locals(), dump_fmem_ao(), dump_infra2_ao_apc(), dump_infra_ao_apc(), dump_mm_ao_apc(), dump_peri2_ao_apc(), dump_peri_ao_apc(), dump_peri_par_ao_apc(), dump_scp_master(), dw_i2c_base_address(), ehci_debug_hw_enable(), EmptyHeap(), enable_beeps(), enable_cache_region(), enable_fan(), enable_peci(), enable_smbus(), enable_tmpin(), espi_open_generic_io_window(), espi_open_mmio_window(), espi_std_io_decode(), execute_command(), extemp_force_idle_status(), fan_smartconfig(), fast_spi_cache_bios_region(), fast_spi_enable_cache_range(), fast_spi_ext_bios_cache_range(), fast_spi_get_ext_bios_window(), fch_smbus_enable_decode(), fill_pattern5(), find_image_with_overlays(), fixed_io_resource(), fmem_master_init(), fsp_print_guid(), fsp_print_resource_descriptor(), gcov_sync(), generate_pmp(), generate_pmp_napot(), generate_pmp_range(), get_bar(), get_bar_in_mchbar(), get_emif_rev(), get_pcie_bar(), get_uma_base(), getreg(), getreg_domain(), google_chromeec_ioport_range(), gpio_family_number(), graphics_soc_panel_init(), gspi_set_base_addr(), hda_codec_detect(), hda_codec_init(), hda_codec_write(), hda_init(), hda_pch_init(), hda_wait_for_ready(), hda_wait_for_valid(), host_and_or(), host_inb(), host_outb(), hudson_disable_4dw_burst(), hudson_lpc_enable_childrens_resources(), hudson_read_mode(), hudson_set_readspeed(), hudson_set_spi100(), hudson_spibase(), identity_map_one_page(), imd_region_used(), imr_resource(), infra2_init(), infra_init(), infra_master_init(), init_hwm(), init_pll(), io_range_in_default(), ite_ec_init(), ldn_gen_resources(), log_me_ro_write_protection_info(), lpc_ec_read_resources(), lpc_enable_childrens_resources(), lpc_get_spibase(), lpc_open_mmio_window(), lpc_open_pmio_window(), lpc_set_spibase(), lpc_spibase(), lpc_wideio_16_window(), lpc_wideio_512_window(), lpc_wideio_window(), lpss_clk_update(), lpss_i2c_early_init_bus(), lpss_is_controller_in_reset(), lpss_reset_release(), mainboard_azalia_program_runtime_verbs(), mainboard_r0x_configure_alc888(), mc_add_fixed_mmio_resources(), mec_emi_write_address(), mec_io_bytes(), mem_region_device_init(), mem_region_device_ro_init(), mem_region_device_rw_init(), memory_in_range(), memranges_create_hole(), memranges_find_entry(), memranges_insert(), memranges_steal(), minihd_init(), mm_init(), msdc_controller_init(), msm_boot_uart_dm_reset(), mtk_emmc_early_init(), mtk_pcie_get_controller_base(), ne2k_append_data(), number(), nuvoton_hwm_select_bank(), OemInitResume(), OemS3LateRestore(), optimize_var_mtrr_hole(), paging_identity_map_addr(), pch_io_range_in_default(), pch_lpc_add_gen_io_resources(), pch_lpc_add_io_resource(), pch_lpc_add_io_resources(), pch_lpc_add_new_resource(), pch_pmc_add_new_resource(), pci_ehci_base_regs(), pci_map_bus(), pci_s_bridge_set_mmio(), pci_store_bridge_resource(), peri2_init(), peri_init(), peri_master_init(), peri_par_init(), platform_prog_run(), pnp_read_hwm5_index(), pnp_unset_and_set_hwm5_index(), pnp_write_hwm5_index(), postcar_var_mtrr_set(), prep_var_mtrr(), primitive_memtest(), print_carveouts(), program_memory_map(), program_timings(), qclib_add_if_table_entry(), qemu_reserve_ports(), qscratch_write(), qscratch_write_readback(), rdev_chain_mem(), rdev_chain_mem_rw(), recover_postcar_frame(), relative_offset(), relative_pointer(), report_resource_stored(), reserve_dev_resources(), resource_end(), rl5c476_init(), rmodule_load(), rmodule_parse(), s5p_dp_config_video(), s5p_dp_config_video_slave_mode(), s5p_dp_enable_scramble(), s5p_dp_enable_video_master(), s5p_dp_hw_link_training(), s5p_dp_init_analog_func(), s5p_dp_init_aux(), s5p_dp_init_dp(), s5p_dp_init_video(), s5p_dp_is_slave_video_stream_clock_on(), s5p_dp_is_video_stream_on(), s5p_dp_read_byte_from_dpcd(), s5p_dp_reset(), s5p_dp_set_lane_lane_pre_emphasis(), s5p_dp_set_video_color_format(), s5p_dp_set_video_cr_mn(), s5p_dp_start_aux_transaction(), s5p_dp_wait_hw_link_training_done(), s5p_dp_write_byte_to_dpcd(), sa_add_fixed_mmio_resources(), sa_add_imr_resources(), sa_set_mch_bar(), sa_set_pci_bar(), sanity_check_pci_mmconf(), save_uma_base(), sc_add_io_resource(), scp_master_init(), set_infra_ao_apc(), set_mm_ao_apc(), set_module_apc(), set_mtrr(), set_peri2_ao_apc(), set_peri_ao_apc(), set_peri_par_ao_apc(), set_range_uc(), set_resource_base(), set_slave_apc(), set_slave_noc_dapc(), set_var_mtrr(), setup_command(), setup_pmp(), show_one_resource(), smbus_enable_iobar(), smbus_host_reset(), smbus_read_cmd(), smbus_set_slave_addr(), smbus_write_cmd(), smm_create_map(), smm_list_regions(), smm_load_module(), smm_module_setup_stub(), smm_save_state(), smm_stub_place_staggered_entry_points(), soc_enable_psp_early(), spi_fpr(), spi_get_wp_cse_ro_range(), spi_protection(), spi_set_base(), stage_cache_add_raw(), stage_cache_create_empty(), stage_cache_external_region(), stage_cache_get_raw(), stage_cache_recover(), timestamp_cache_init(), timestamp_init(), uart8250_mem_can_rx_byte(), uart8250_mem_can_tx_byte(), uart8250_mem_init(), uart8250_mem_rx_byte(), uart8250_mem_tx_byte(), uart8250_mem_tx_flush(), uart8250_read(), uart8250_write(), uart_init(), uart_is_controller_initialized(), uart_platform_base(), uart_rx_byte(), uart_tx_byte(), uart_tx_flush(), update_bridge_resource(), usb_ehci_init(), var_mtrr_set_with_cb(), void(), vtxprintf(), wait_for_ready(), wait_for_valid(), wilco_ec_resource(), write_testing(), X86EMU_setMemBase(), and xhci_port_wake_check().

| struct device_operations cezanne_uart_mmio_ops |

Definition at line 88 of file uart.c.

Referenced by set_mmio_dev_ops().

| struct soc_amd_gpio mux[2] |

| const { ... } uart_info[] |

Referenced by get_uart_base(), and set_uart_config().