|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

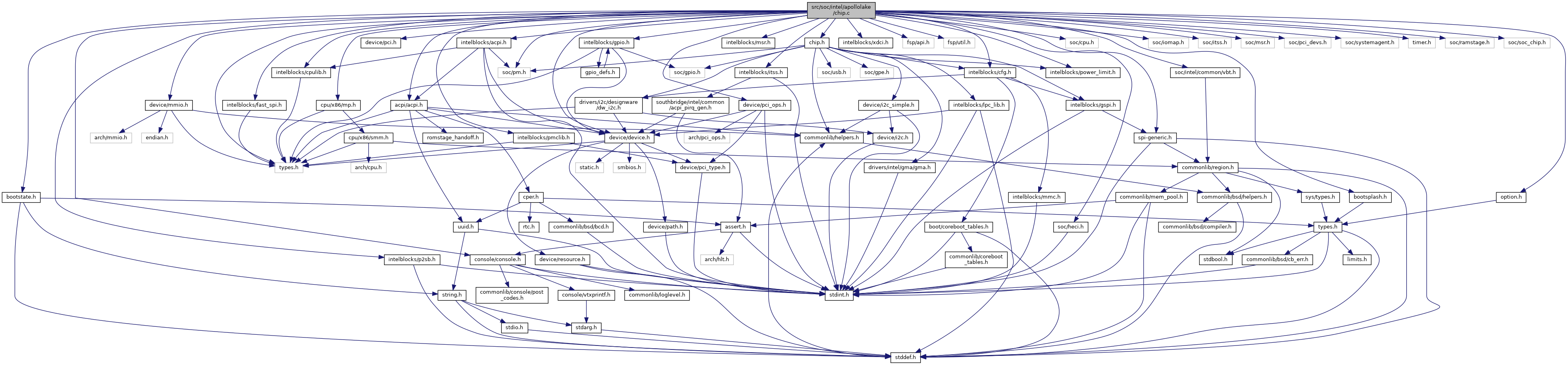

#include <acpi/acpi.h>#include <bootsplash.h>#include <bootstate.h>#include <console/console.h>#include <cpu/x86/mp.h>#include <device/mmio.h>#include <device/device.h>#include <device/pci.h>#include <device/pci_ops.h>#include <intelblocks/acpi.h>#include <intelblocks/cfg.h>#include <intelblocks/fast_spi.h>#include <intelblocks/msr.h>#include <intelblocks/p2sb.h>#include <intelblocks/power_limit.h>#include <intelblocks/xdci.h>#include <fsp/api.h>#include <fsp/util.h>#include <intelblocks/cpulib.h>#include <intelblocks/gpio.h>#include <intelblocks/itss.h>#include <intelblocks/pmclib.h>#include <option.h>#include <soc/cpu.h>#include <soc/heci.h>#include <soc/intel/common/vbt.h>#include <soc/iomap.h>#include <soc/itss.h>#include <soc/msr.h>#include <soc/pci_devs.h>#include <soc/pm.h>#include <soc/systemagent.h>#include <spi-generic.h>#include <timer.h>#include <soc/ramstage.h>#include <soc/soc_chip.h>#include <types.h>#include "chip.h"

Go to the source code of this file.

Macros | |

| #define | DUAL_ROLE_CFG0 0x80d8 |

| #define | SW_VBUS_VALID_MASK (1 << 24) |

| #define | SW_IDPIN_EN_MASK (1 << 21) |

| #define | SW_IDPIN_MASK (1 << 20) |

| #define | SW_IDPIN_HOST (0 << 20) |

| #define | DUAL_ROLE_CFG1 0x80dc |

| #define | DRD_MODE_MASK (1 << 29) |

| #define | DRD_MODE_HOST (1 << 29) |

| #define | CFG_XHCLKGTEN 0x8650 |

| #define | NUEFBCGPS (1 << 28) |

| #define | SRAMPGTEN (1 << 27) |

| #define | SSLSE (1 << 26) |

| #define | USB2PLLSE (1 << 25) |

| #define | IOSFSTCGE (1 << 24) |

| #define | HSTCGE (1 << 23 | 1 << 22) |

| #define | SSTCGE (1 << 19 | 1 << 18 | 1 << 17) |

| #define | XHCIGEU3S (1 << 15) |

| #define | XHCFTCLKSE (1 << 14) |

| #define | XHCBBTCGIPISO (1 << 13) |

| #define | XHCHSTCGU2NRWE (1 << 12) |

| #define | XHCUSB2PLLSDLE (1 << 11 | 1 << 10) |

| #define | HSUXDMIPLLSE (1 << 9) |

| #define | SSPLLSUE (1 << 6) |

| #define | XHCBLCGE (1 << 4) |

| #define | HSLTCGE (1 << 3) |

| #define | SSLTCGE (1 << 2) |

| #define | IOSFBTCGE (1 << 1) |

| #define | IOSFGBLCGE (1 << 0) |

| #define | CFG_XHCPMCTRL 0x80a4 |

| #define | LFPS_PM_DISABLE_MASK 0xFFFFFF0F |

Variables | |

| static struct device_operations | pci_domain_ops |

| static struct device_operations | cpu_bus_ops |

| struct chip_operations | soc_intel_apollolake_ops |

|

static |

Definition at line 481 of file chip.c.

References APOLLOLAKE_USB2_PORT_MAX, APOLLOLAKE_USB3_PORT_MAX, usb_port_config::enable, usb_port_config::oc_pin, usb2_eye_per_port::Usb20HsNpreDrvSel, usb2_eye_per_port::Usb20HsSkewSel, usb2_eye_per_port::Usb20IUsbTxEmphasisEn, usb2_eye_per_port::Usb20PerPortPeTxiSet, usb2_eye_per_port::Usb20PerPortRXISet, usb2_eye_per_port::Usb20PerPortTxiSet, usb2_eye_per_port::Usb20PerPortTxPeHalf, soc_intel_apollolake_config::usb2_port, soc_intel_apollolake_config::usb2eye, soc_intel_apollolake_config::usb3_port, and soc_intel_apollolake_config::usb_config_override.

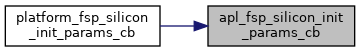

Referenced by platform_fsp_silicon_init_params_cb().

| BOOT_STATE_INIT_ENTRY | ( | BS_PRE_DEVICE | , |

| BS_ON_ENTRY | , | ||

| spi_flash_init_cb | , | ||

| NULL | |||

| ) |

|

static |

Definition at line 781 of file chip.c.

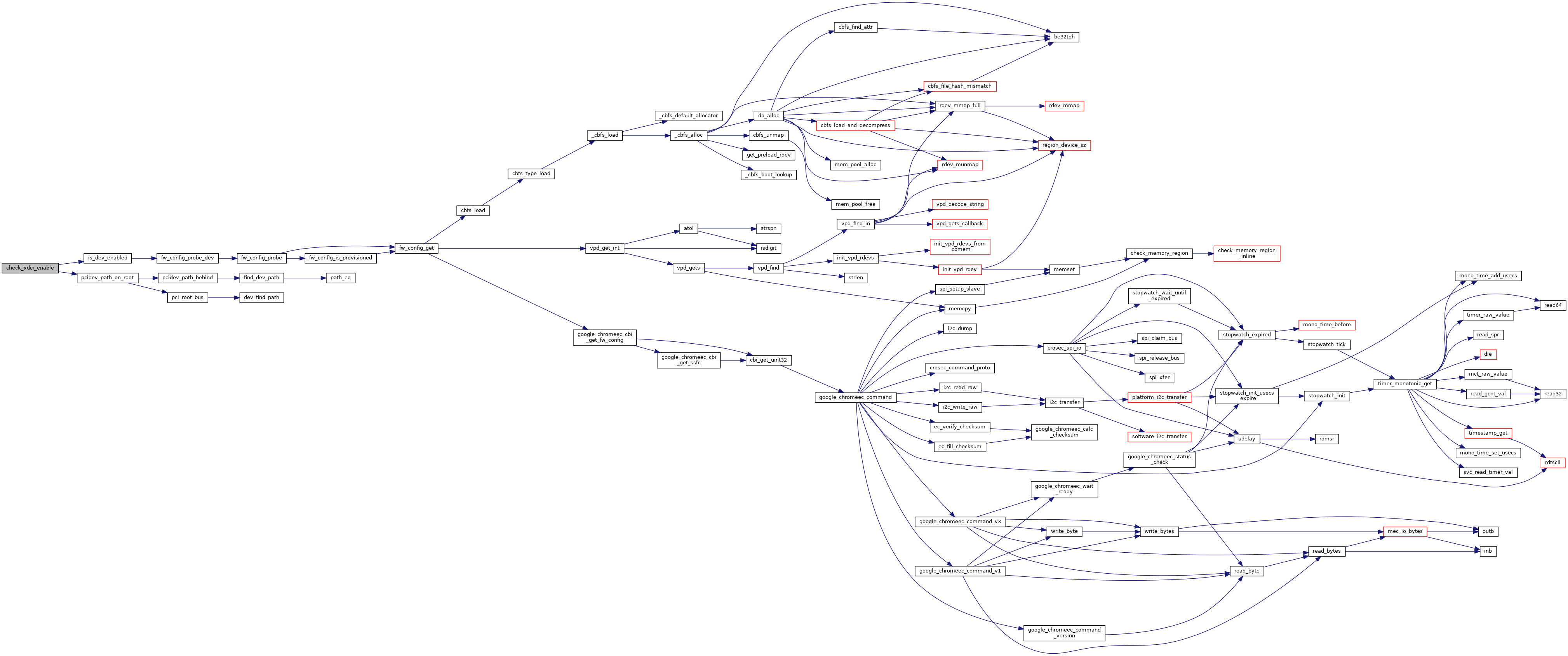

References is_dev_enabled(), PCH_DEVFN_XDCI, and pcidev_path_on_root().

Referenced by platform_fsp_notify_status().

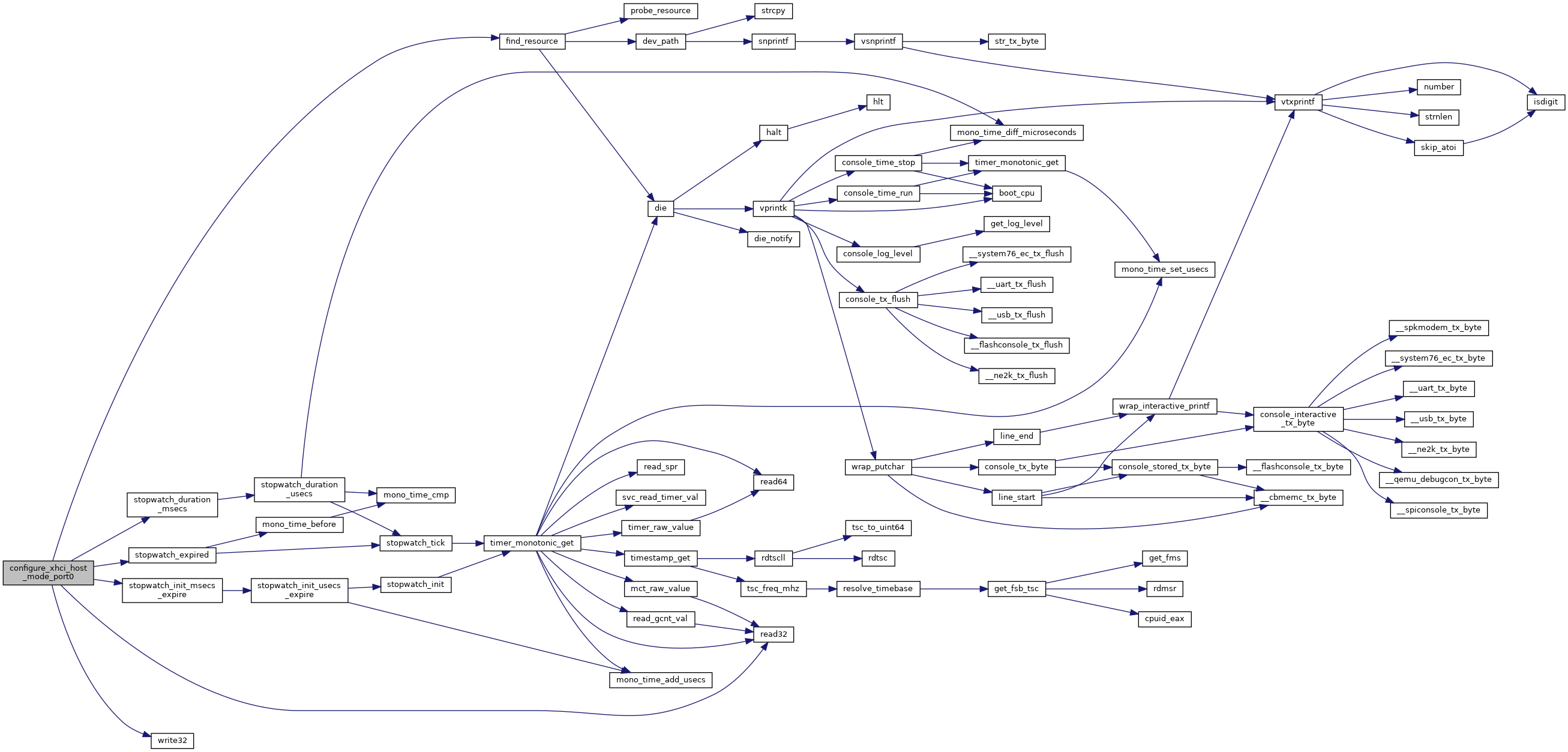

Definition at line 748 of file chip.c.

References resource::base, BIOS_ERR, BIOS_INFO, DRD_MODE_HOST, DRD_MODE_MASK, DUAL_ROLE_CFG0, DUAL_ROLE_CFG1, find_resource(), PCH_DEV_XHCI, PCI_BASE_ADDRESS_0, printk, read32(), stopwatch_duration_msecs(), stopwatch_expired(), stopwatch_init_msecs_expire(), SW_IDPIN_EN_MASK, SW_IDPIN_MASK, SW_VBUS_VALID_MASK, and write32().

Referenced by platform_fsp_notify_status().

|

static |

Definition at line 344 of file chip.c.

References BIOS_WARNING, pci_path::devfn, device::path, PCH_DEVFN_CNVI, PCH_DEVFN_EMMC, PCH_DEVFN_HDA, PCH_DEVFN_I2C0, PCH_DEVFN_I2C1, PCH_DEVFN_I2C2, PCH_DEVFN_I2C3, PCH_DEVFN_I2C4, PCH_DEVFN_I2C5, PCH_DEVFN_I2C6, PCH_DEVFN_I2C7, PCH_DEVFN_ISH, PCH_DEVFN_NPK, PCH_DEVFN_PCIE1, PCH_DEVFN_PCIE2, PCH_DEVFN_PCIE3, PCH_DEVFN_PCIE4, PCH_DEVFN_PCIE5, PCH_DEVFN_PCIE6, PCH_DEVFN_SATA, PCH_DEVFN_SDCARD, PCH_DEVFN_SDIO, PCH_DEVFN_SMBUS, PCH_DEVFN_SPI0, PCH_DEVFN_SPI1, PCH_DEVFN_SPI2, PCH_DEVFN_UART0, PCH_DEVFN_UART1, PCH_DEVFN_UART2, PCH_DEVFN_UART3, PCH_DEVFN_XDCI, PCH_DEVFN_XHCI, device_path::pci, PCI_FUNC, PCI_SLOT, printk, and SA_DEVFN_IPU.

Referenced by parse_devicetree().

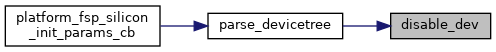

Definition at line 786 of file chip.c.

References addr, resource::base, BIOS_DEBUG, BIOS_INFO, CFG_XHCPMCTRL, config_of_soc, soc_intel_apollolake_config::disable_xhci_lfps_pm, find_resource(), LFPS_PM_DISABLE_MASK, PCH_DEV_XHCI, PCI_BASE_ADDRESS_0, printk, read32(), and write32().

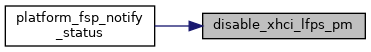

Referenced by platform_fsp_notify_status().

Definition at line 741 of file chip.c.

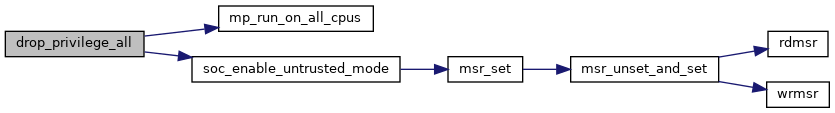

References BIOS_ERR, CB_SUCCESS, mp_run_on_all_cpus(), NULL, printk, and soc_enable_untrusted_mode().

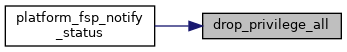

Referenced by platform_fsp_notify_status().

Definition at line 214 of file chip.c.

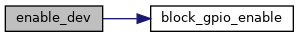

References block_gpio_enable(), cpu_bus_ops, DEVICE_PATH_CPU_CLUSTER, DEVICE_PATH_DOMAIN, DEVICE_PATH_GPIO, device::ops, device::path, pci_domain_ops, and device_path::type.

|

static |

Definition at line 537 of file chip.c.

References APOLLOLAKE_USB2_PORT_MAX, APOLLOLAKE_USB3_PORT_MAX, soc_intel_apollolake_config::DisableComplianceMode, usb_port_config::enable, is_devfn_enabled(), memcpy(), soc_intel_apollolake_config::ModPhyIfValue, soc_intel_apollolake_config::ModPhyVoltageBump, usb_port_config::oc_pin, soc_intel_apollolake_config::pcie_rp_deemphasis_enable, soc_intel_apollolake_config::PmicPmcIpcCtrl, soc_intel_apollolake_config::PmicVdd2Voltage, SA_GLK_DEVFN_GMM, usb2_eye_per_port::Usb20IUsbTxEmphasisEn, usb2_eye_per_port::Usb20OverrideEn, usb2_eye_per_port::Usb20PerPortPeTxiSet, usb2_eye_per_port::Usb20PerPortTxiSet, usb2_eye_per_port::Usb20PerPortTxPeHalf, soc_intel_apollolake_config::usb2_port, soc_intel_apollolake_config::usb2eye, soc_intel_apollolake_config::usb3_port, and soc_intel_apollolake_config::usb_config_override.

Referenced by platform_fsp_silicon_init_params_cb().

Definition at line 623 of file chip.c.

Referenced by platform_fsp_silicon_init_params_cb().

| __weak void mainboard_silicon_init_params | ( | FSP_S_CONFIG * | silconfig | ) |

Definition at line 875 of file chip.c.

References BIOS_DEBUG, and printk.

Referenced by platform_fsp_silicon_init_params_cb().

|

static |

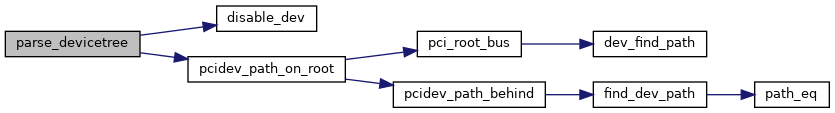

Definition at line 466 of file chip.c.

References BIOS_ERR, device::bus, bus::children, disable_dev(), device::enabled, pcidev_path_on_root(), printk, SA_DEVFN_ROOT, and device::sibling.

Referenced by platform_fsp_silicon_init_params_cb().

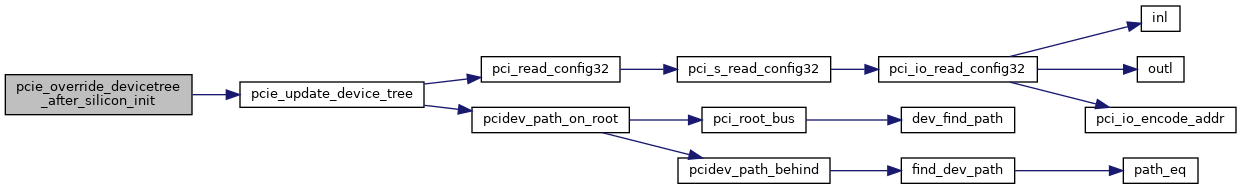

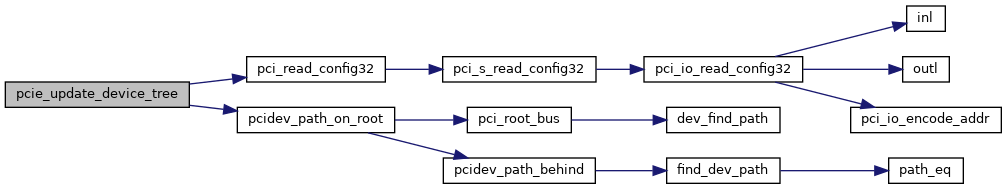

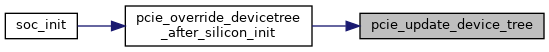

Definition at line 268 of file chip.c.

References PCH_DEVFN_PCIE1, PCH_DEVFN_PCIE5, and pcie_update_device_tree().

Referenced by soc_init().

Definition at line 232 of file chip.c.

References pci_path::devfn, device::enabled, NULL, device::path, device_path::pci, PCI_DEVFN, pci_read_config32(), PCI_VENDOR_ID, and pcidev_path_on_root().

Referenced by pcie_override_devicetree_after_silicon_init().

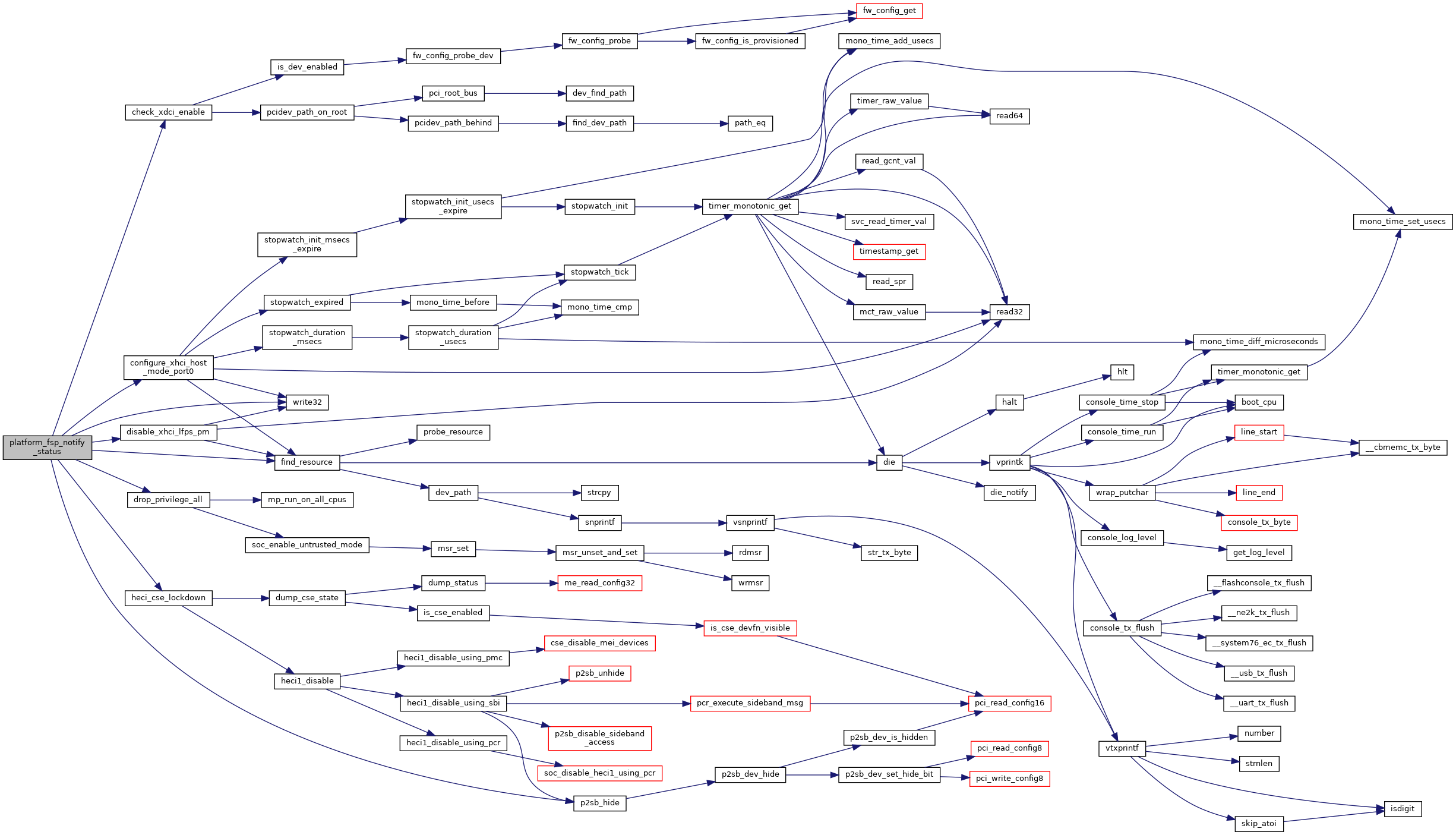

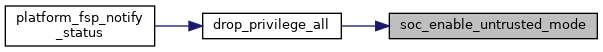

| void platform_fsp_notify_status | ( | enum fsp_notify_phase | phase | ) |

Definition at line 810 of file chip.c.

References resource::base, CFG_XHCLKGTEN, check_xdci_enable(), CONFIG, configure_xhci_host_mode_port0(), disable_xhci_lfps_pm(), drop_privilege_all(), END_OF_FIRMWARE, find_resource(), heci_cse_lockdown(), HSLTCGE, HSTCGE, HSUXDMIPLLSE, IOSFBTCGE, IOSFGBLCGE, IOSFSTCGE, p2sb_hide(), PCH_DEV_XHCI, PCI_BASE_ADDRESS_0, SRAMPGTEN, SSLSE, SSLTCGE, SSPLLSUE, SSTCGE, USB2PLLSE, write32(), XHCBBTCGIPISO, XHCBLCGE, XHCFTCLKSE, and XHCUSB2PLLSDLE.

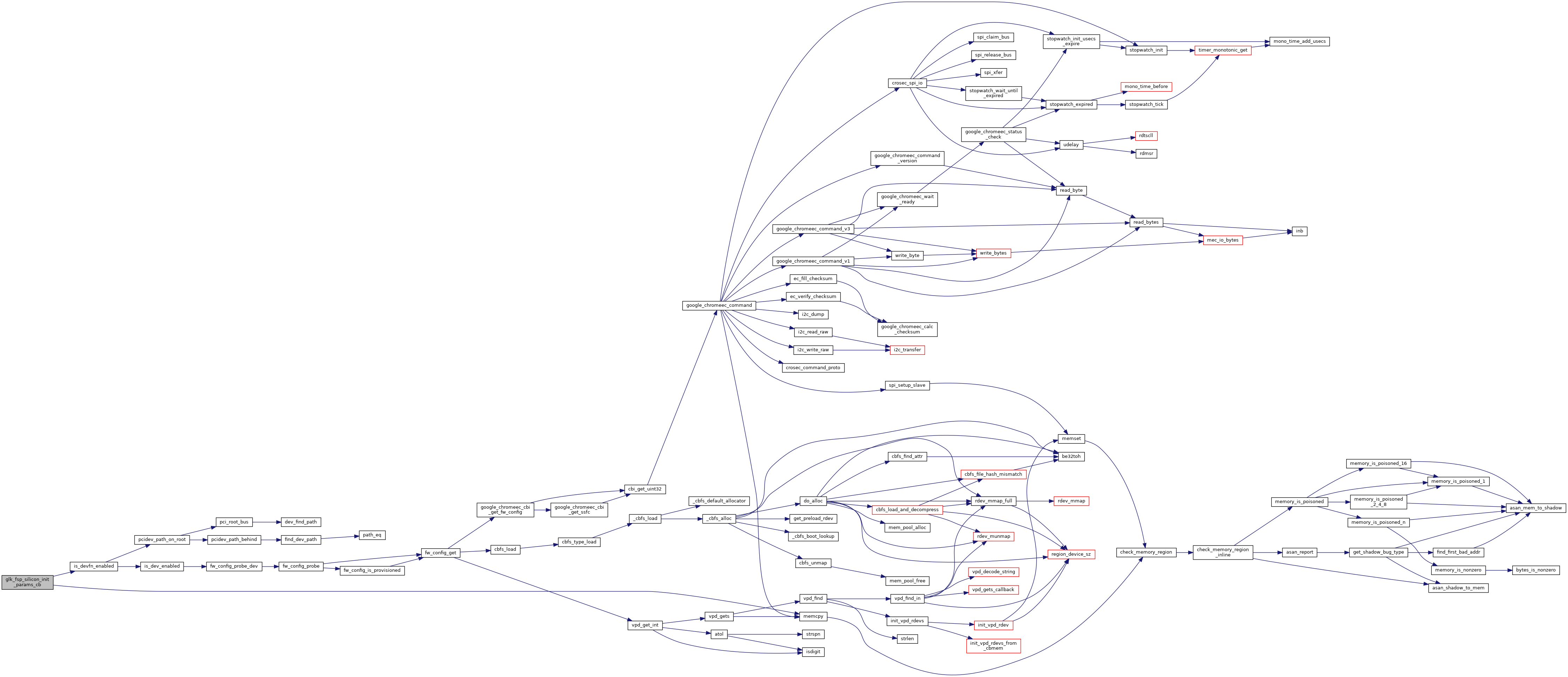

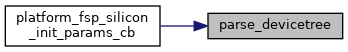

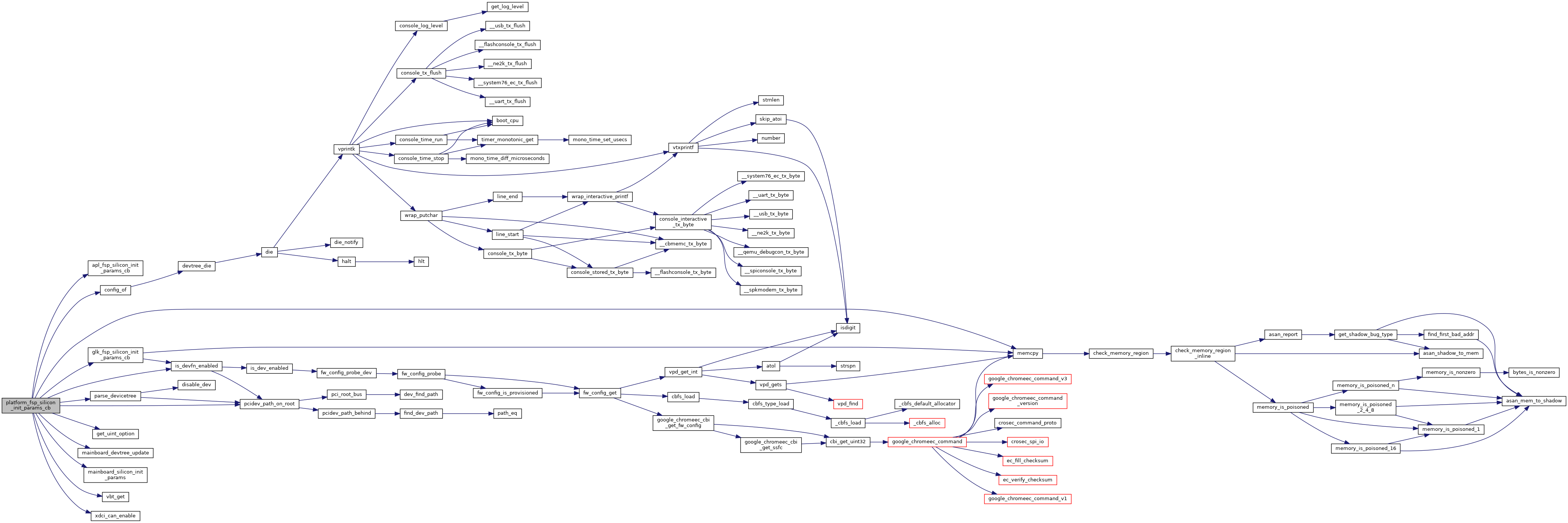

| void platform_fsp_silicon_init_params_cb | ( | FSPS_UPD * | silupd | ) |

Definition at line 628 of file chip.c.

References apl_fsp_silicon_init_params_cb(), CONFIG, config_of(), soc_intel_apollolake_config::DisableSataSalpSupport, soc_intel_apollolake_config::emmc_host_max_speed, soc_intel_apollolake_config::emmc_rx_cmd_data_cntl1, soc_intel_apollolake_config::emmc_rx_cmd_data_cntl2, soc_intel_apollolake_config::emmc_rx_strobe_cntl, soc_intel_apollolake_config::emmc_tx_cmd_cntl, soc_intel_apollolake_config::emmc_tx_data_cntl1, soc_intel_apollolake_config::emmc_tx_data_cntl2, soc_intel_apollolake_config::enable_vtd, FSP_S_CONFIG, get_uint_option(), glk_fsp_silicon_init_params_cb(), soc_intel_apollolake_config::hdaudio_bios_config_lockdown, soc_intel_apollolake_config::hdaudio_clk_gate_enable, soc_intel_apollolake_config::hdaudio_pwr_gate_enable, is_devfn_enabled(), soc_intel_apollolake_config::lpss_s0ix_enable, mainboard_devtree_update(), mainboard_silicon_init_params(), memcpy(), parse_devicetree(), PAVP, PCH_DEVFN_SATA, PCH_DEVFN_XDCI, pcidev_path_on_root(), soc_intel_apollolake_config::pcie_rp_clkreq_pin, soc_intel_apollolake_config::pcie_rp_hotplug_enable, SA_DEVFN_IGD, SA_DEVFN_ROOT, SERIRQ_CONTINUOUS, soc_intel_apollolake_config::serirq_mode, SERIRQ_OFF, SERIRQ_QUIET, vbt_get(), and xdci_can_enable().

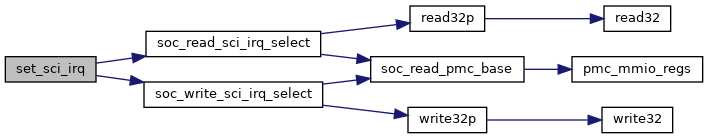

Definition at line 275 of file chip.c.

References config_of_soc, soc_intel_apollolake_config::sci_irq, SCI_IRQ_ADJUST, SCI_IRQ_SEL, soc_read_sci_irq_select(), and soc_write_sci_irq_select().

Referenced by soc_init().

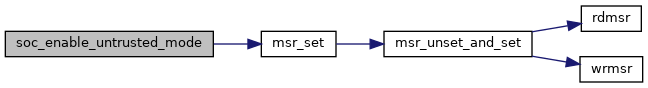

Definition at line 732 of file chip.c.

References ENABLE_IA_UNTRUSTED, MSR_POWER_MISC, and msr_set().

Referenced by drop_privilege_all().

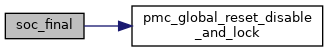

Definition at line 338 of file chip.c.

References pmc_global_reset_disable_and_lock().

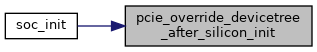

Definition at line 291 of file chip.c.

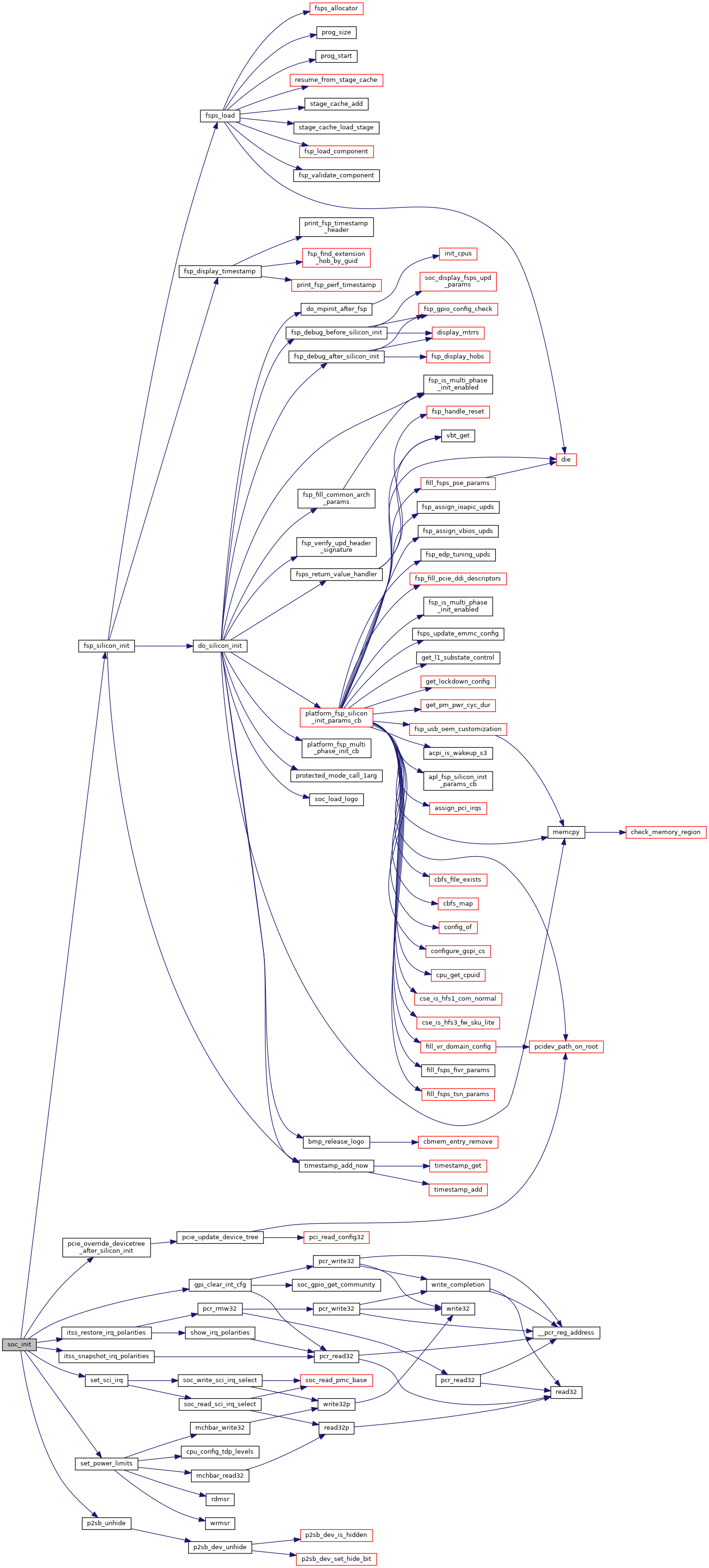

References BIOS_INFO, config, CONFIG, config_of_soc, fsp_silicon_init(), gpi_clear_int_cfg(), GPIO_IRQ_END, GPIO_IRQ_START, itss_restore_irq_polarities(), itss_snapshot_irq_polarities(), MOBILE_SKU_PL1_TIME_SEC, p2sb_unhide(), pcie_override_devicetree_after_silicon_init(), printk, set_power_limits(), and set_sci_irq().

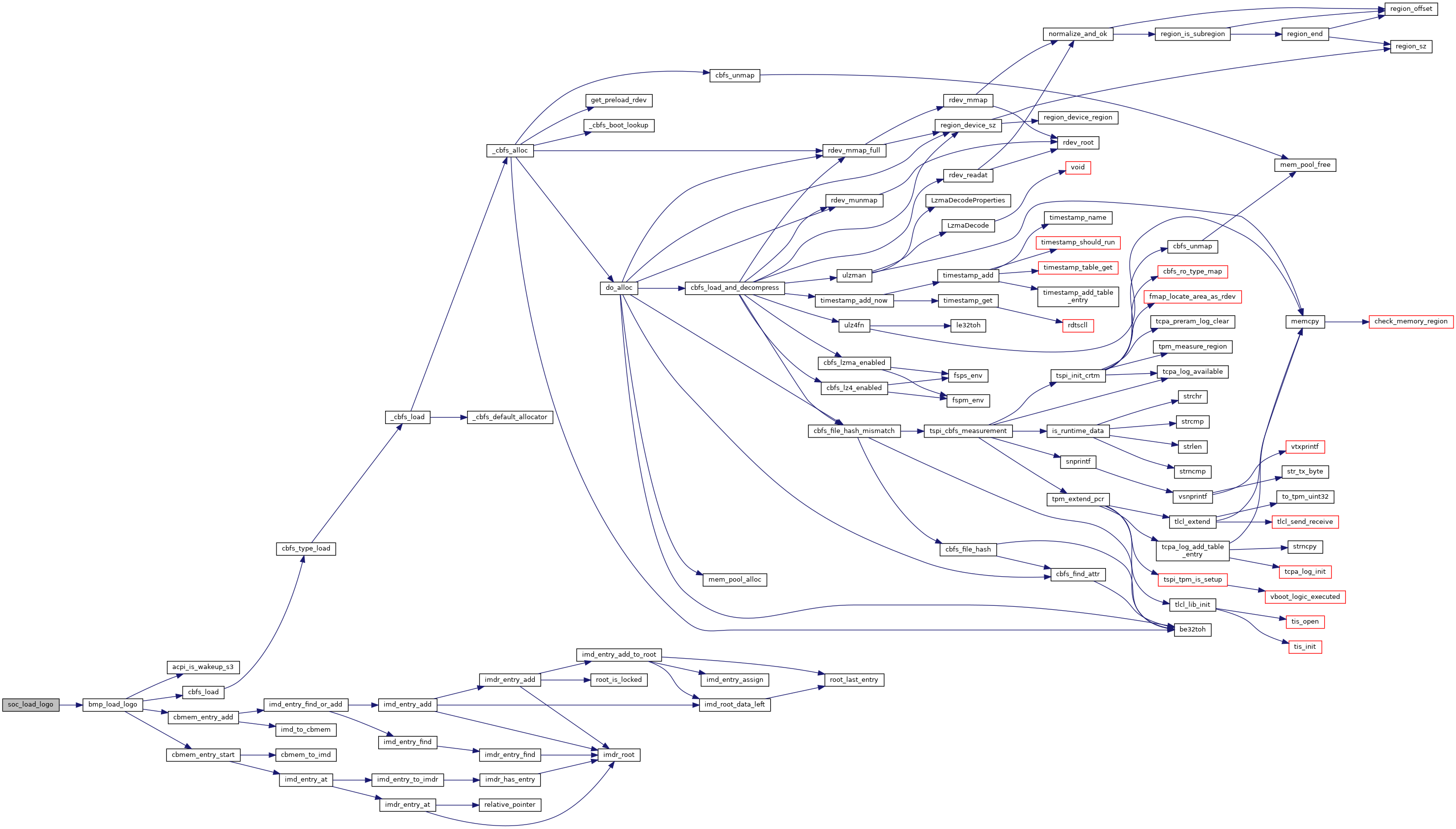

| void soc_load_logo | ( | FSPS_UPD * | supd | ) |

Definition at line 881 of file chip.c.

References bmp_load_logo().

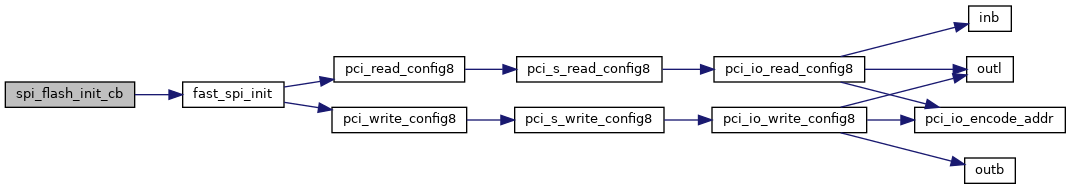

Definition at line 869 of file chip.c.

References fast_spi_init().

|

static |

|

static |

Definition at line 96 of file chip.c.

Referenced by enable_dev().

| struct chip_operations soc_intel_apollolake_ops |