|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

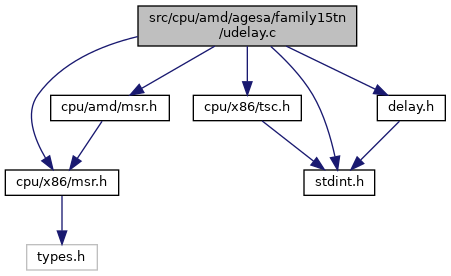

#include <cpu/x86/msr.h>#include <cpu/amd/msr.h>#include <cpu/x86/tsc.h>#include <delay.h>#include <stdint.h>

Go to the source code of this file.

Functions | |

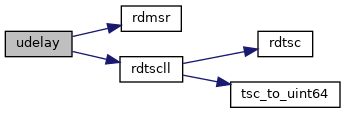

| void | udelay (uint32_t us) |

Definition at line 15 of file udelay.c.

References did, msr_struct::lo, PS_STS_REG, PSTATE_0_MSR, rdmsr(), and rdtscll().

Referenced by _gpio_base2_value(), _gpio_base3_value(), ac97_audio_init(), ast_init_dram_reg(), ast_software_i2c_read(), auto_refresh_cke_off(), auxadc_get_rawdata(), azalia_init(), backlight_off(), backlight_pwm(), backlight_vdd(), blsp_i2c_clock_config(), bootblock_mainboard_init(), bridge_ps8640_power_on(), cbt_dramc_dfs_direct_jump(), cbt_entry(), cbt_exit(), cbt_set_ca_clk_result(), cbt_set_vref(), check_bit_state(), check_ipc_sts(), clk_buf_init(), clock_early_uart(), clock_enable_clear_reset(), clock_grp_enable_clear_reset(), clock_reset_dev(), clock_reset_h(), clock_reset_l(), clock_reset_u(), clock_reset_v(), clock_reset_w(), clock_reset_x(), clock_sdram(), config_sdram(), configure_display(), configure_display_clocks(), configure_ext_buck(), configure_touchscreen(), cpu_cl_poll_mailbox_ready(), crosec_spi_io(), crport_handshake(), cse_wait_com_soft_temp_disable(), cse_wait_sec_override_mode(), data_training(), dcxo_init(), ddr2_init(), ddr3_calibrate_zq(), ddr3_init(), ddr3_mem_ctrl_init(), ddr_phy_init_2500(), ddr_phy_pll_setting(), disable_cse_idle(), disable_sor_periph_clocks(), display_startup(), div2_phase_sync(), dlpc_init(), dmc_config_mrs(), dmc_config_prech(), dmc_config_zq(), do_bus_clear(), do_ram_command(), do_raminit(), dock_connect(), dock_disconnect(), dock_superio_init(), dp_controller_init(), dqsosc_auto(), dram_dimm_set_mapping(), dram_freq(), dram_ioregs(), dram_jedecreset(), dram_phy_reset(), dram_powerup(), dramc_auto_refresh_switch(), dramc_cmd_bus_training(), dramc_engine2(), dramc_engine2_compare(), dramc_engine2_run(), dramc_gating_mode(), dramc_init(), dramc_mode_reg_read(), dramc_mode_reg_write(), dramc_phy_reset(), dramc_power_on_sequence(), dramc_rx_dqs_gating_cal_partial(), dramc_rx_dqs_gating_cal_pre(), dramc_set_gating_mode(), dramc_sw_impedance_cal(), dramc_zq_calibration(), drive_scl(), early_superio_config(), ec_clear_out_queue(), ec_ready(), enable_aoac_devices(), enable_ape_periph_clocks(), enable_sor_periph_clocks(), exynos_dp_bridge_init(), exynos_dp_bridge_setup(), exynos_dp_reset(), exynos_dp_reset_macro(), get_saradc_value(), gma_func0_init(), google_chromeec_status_check(), gpio_read_mvl3(), gpio_sc_sdcard_workaround(), gsbi_clock_init(), gspi_ctrlr_setup(), gtt_poll(), gtt_setup(), hda_wait_for_ready(), hda_wait_for_valid(), hdmi_ddc_wait_i2c_done(), hdmi_phy_configure(), hdmi_phy_wait_i2c_done(), hdmi_wait_for_hpd(), hs_usb_phy_init(), i2c_disable(), i2c_hw_reset(), i2c_read(), i2c_send_start(), i2c_send_stop(), i2c_wait_for_idle(), i2c_wait_for_int(), i2c_write(), ich_hwseq_wait_for_cycle_complete(), ich_status_poll(), iic_tpm_read(), iic_tpm_write_generic(), increment_to_dqs_edge(), init_dvs_outputs(), init_pllu(), init_utmip_pll(), input_buffer_empty(), intel_early_me_init(), intel_early_me_init_done(), intel_me_hsio_version(), intel_me_mbp_clear(), iobp_poll(), ipq_setup_tpm(), it8518_init(), jedec_ddr2(), jedec_ddr3(), jedec_init(), lapic_start_cpu(), late_quickpath_init(), lcc_enable_mi2s(), ledc_write_engctrl2(), legacy_io_init(), m3885_configure_multikey(), mainboard_enable(), mainboard_init(), mbist_workaround(), mdss_dsi_phy_reset(), mei_recv_msg(), mei_wait_for_me_ready(), mem_pll_init(), mem_pll_phase_cali(), memory_init(), mmc_complete_op_cond(), mrs_write(), msdc_poll_timeout(), msdc_wait_done(), msleep(), mt6315_wdt_enable(), mt6391_init_setting(), mt_pll_enable_ssusb_clk(), mt_pll_init(), mt_pll_raise_cci_freq(), mt_pll_raise_little_cpu_freq(), mt_pll_set_tvd_pll1_freq(), mtcmos_power_on(), mtk_dsi_configure_mipi_tx(), mtk_pcie_domain_enable(), nand_clock_config(), o1_path_on_off(), output_buffer_full(), parade_dp_bridge_setup(), pc87382_connect(), pc87382_init(), pci_s_early_mmio_window(), pciexp_retrain_link(), pcode_ready(), phy_init(), phy_pctrl_reset(), platform_i2c_read(), platform_i2c_transfer(), platform_i2c_write(), pmh7_dgpu_power_enable(), pmic_init(), pmic_read_efuse(), pmic_set_vcore_vol(), pmic_set_vddq_vol(), pmic_set_vdram1_vol(), pmic_set_vproc12_vol(), pmic_set_vsram_proc12_vol(), pmic_write_reg(), pmif_get_ulposc_freq_mhz(), pmif_init_ulposc(), poll_clk_stable(), prepare_training(), program_dll(), program_mac_address(), punit_init(), pwrap_init(), raise_little_cpu_freq(), raminit(), raminit_rcomp_calibration(), read_gpio(), recv_ec_data(), recv_ec_oem_data(), recv_kbd_data(), reg_script_run_step(), reg_write(), reset_edp(), reset_phy_ctrl(), restore_timings(), rk_edp_link_train_ce(), rk_edp_wait_hpd(), rk_hdmi_get_edid(), rk_mipi_prepare(), rkclk_configure_cpu(), rkclk_configure_ddr(), rkclk_configure_edp(), rkclk_configure_hdmi(), rkclk_configure_vop_dclk(), rkclk_init(), rkclk_set_dpllssc(), rkclk_set_pll(), rl5c476_init(), root_port_commit_config(), rtc_get(), rtc_get_frequency_meter(), rtc_hw_init(), s5p_dp_hw_link_training(), s5p_dp_init_dp(), s5p_dp_reset(), sampledqs(), sata_init(), sd_change_freq(), sd_mmc_send_status(), sd_send_op_cond(), sdhci_complete_adma(), sdhci_reset(), sdhci_send_command_bounced(), sdhci_set_clock(), sdhci_transfer_data(), sdram_configure_pmc(), sdram_deassert_clock_enable_signal(), sdram_deassert_sel_dpd(), sdram_enable(), sdram_enable_rcomp(), sdram_init(), sdram_init_emc(), sdram_init_lpddr3(), sdram_init_lpddr4(), sdram_init_zq_calibration(), sdram_rel_dpd(), sdram_set_clock_enable_signal(), sdram_set_ddr_control(), sdram_set_dli_trims(), sdram_set_dpd(), sdram_set_dpd3(), sdram_set_pad_macros(), sdram_set_zq_calibration(), sdram_start_clocks(), send_command(), send_ec_command(), send_ec_data(), send_ec_oem_command(), send_ec_oem_data(), send_jedec_cmd(), send_kbd_command(), send_kbd_data(), set_bandwidth_ratio(), set_mpll_2500(), set_write_vref(), setup_drd_phy(), setup_dwc3(), setup_phy(), setup_tpm(), setup_usb_host(), setup_usb_host_phy(), soc_configure_i2c6pad(), software_ddr3_reset(), speed_up_boot_cpu(), spi_bitbang_xfer(), spi_delay(), spi_dma_readat_dma(), spi_read_byte(), spi_reset(), spi_write_byte(), spm_kick_pcm_to_run(), srclken_rc_init(), start_cpu(), start_other_cpus(), systemagent_init(), tegra_dc_dp_fast_link_training(), tegra_dc_dpaux_poll_register(), tegra_dc_dpaux_read_chunk(), tegra_dc_dpaux_write_chunk(), tegra_dc_poll_register(), tegra_dc_sor_attach(), tegra_dc_sor_enable_dp(), tegra_dc_sor_io_set_dpd(), tegra_dc_sor_poll_register(), tegra_dc_sor_power_up(), tegra_dc_sor_set_lane_parm(), tegra_dp_hpd_plug(), tegra_dp_lt_config(), tegra_dp_wait_aux_training(), tegra_dsi_host_transfer(), tegra_dsi_transmit(), tegra_dsi_wait_for_response(), tegra_mipi_wait(), tegra_sor_precharge_lanes(), tegra_spi_pio_start(), tis_open(), tis_readresponse(), tis_senddata(), tis_sendrecv(), tis_wait_access(), tis_wait_sts(), toggle_io_reset(), tpm_vendor_probe(), tps65090_fet_enable(), tps65090_fet_set(), transfer_pll_to_spm_control(), try_init_dram_ddr3(), tsadc_init(), twsi_unblock(), uart8250_mem_rx_byte(), uart8250_mem_tx_byte(), uart8250_mem_tx_flush(), uart_clock_config(), uart_tx_byte(), uart_wait_hclk(), usb_clock_config(), usb_setup_utmip(), usb_xhci_reset_usb3(), vb2ex_hwcrypto_digest_init(), wait_ack(), wait_done(), wait_for_aoac_enabled(), wait_for_ipi_completion(), wait_for_ipi_completion_without_printk(), wait_for_ready(), wait_for_valid(), wait_heci_ready(), wait_nack(), wait_other_cpus_stop(), wait_rdy(), wait_read_slots(), wait_write_slots(), wfc_id(), winbond_flash_cmd_status(), and xfer().