|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

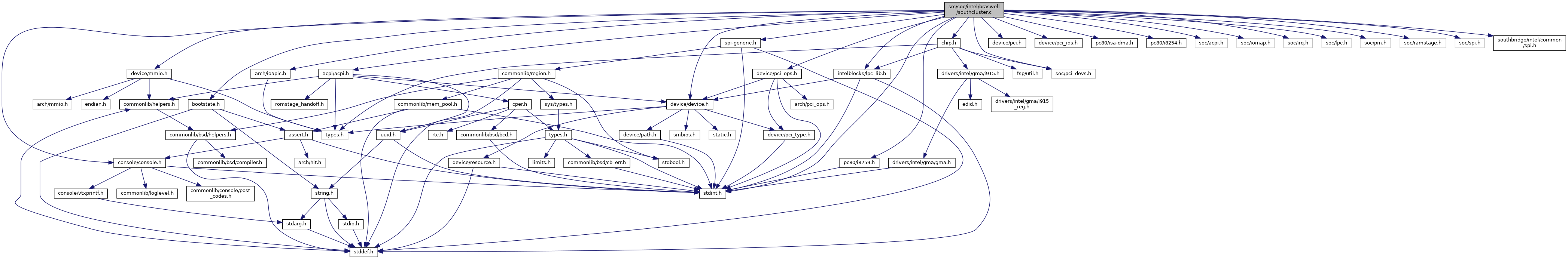

#include <device/mmio.h>#include <device/pci_ops.h>#include <acpi/acpi.h>#include <arch/ioapic.h>#include <bootstate.h>#include "chip.h"#include <console/console.h>#include <device/device.h>#include <device/pci.h>#include <device/pci_ids.h>#include <intelblocks/lpc_lib.h>#include <pc80/isa-dma.h>#include <pc80/i8254.h>#include <pc80/i8259.h>#include <soc/acpi.h>#include <soc/iomap.h>#include <soc/irq.h>#include <soc/lpc.h>#include <soc/pci_devs.h>#include <soc/pm.h>#include <soc/ramstage.h>#include <soc/spi.h>#include <spi-generic.h>#include <stdint.h>#include <southbridge/intel/common/spi.h>

Go to the source code of this file.

Macros | |

| #define | LPC_DEFAULT_IO_RANGE_LOWER 0 |

| #define | LPC_DEFAULT_IO_RANGE_UPPER 0x1000 |

| #define | SET_DIS_MASK(name_) |

| #define | SET_DIS_MASK2(name_) |

| #define | DEV_CASE(name_) case PCI_DEVFN(name_ ## _DEV, name_ ## _FUNC) |

Variables | |

| static struct device_operations | device_ops |

| static const struct pci_driver southcluster | __pci_driver |

| #define DEV_CASE | ( | name_ | ) | case PCI_DEVFN(name_ ## _DEV, name_ ## _FUNC) |

| #define LPC_DEFAULT_IO_RANGE_LOWER 0 |

Definition at line 71 of file southcluster.c.

| #define LPC_DEFAULT_IO_RANGE_UPPER 0x1000 |

Definition at line 72 of file southcluster.c.

| #define SET_DIS_MASK | ( | name_ | ) |

| #define SET_DIS_MASK2 | ( | name_ | ) |

|

inlinestatic |

Definition at line 48 of file southcluster.c.

References addr, and mmio_resource.

Referenced by sc_add_mmio_resources().

| BOOT_STATE_INIT_ENTRY | ( | BS_POST_DEVICE | , |

| BS_ON_EXIT | , | ||

| finalize_chipset | , | ||

| NULL | |||

| ) |

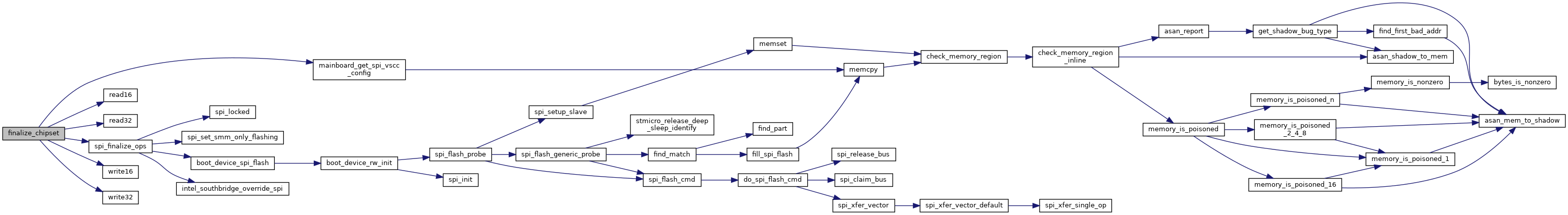

Definition at line 546 of file southcluster.c.

References BCR, BCR_LE, BILD, BIOS_DEBUG, CF9LOCK, ETR, FLOCKDN, GCS, GEN_PMCON2, HSFSTS, LVSCC, vscc_config::lvscc, mainboard_get_spi_vscc_config(), PMC_BASE_ADDRESS, printk, RCBA_BASE_ADDRESS, read16(), read32(), SLPSX_STR_POL_LOCK, SMI_LOCK, SPI_BASE_ADDRESS, spi_finalize_ops(), UVSCC, vscc_config::uvscc, VCL, write16(), and write32().

Definition at line 405 of file southcluster.c.

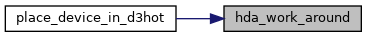

References PCI_BASE_ADDRESS_0, PCI_BASE_ADDRESS_1, PCI_COMMAND, PCI_COMMAND_MEMORY, pci_write_config16(), pci_write_config32(), pci_write_config8(), read32(), TEMP_BASE_ADDRESS, and write32().

Referenced by place_device_in_d3hot().

|

inlinestatic |

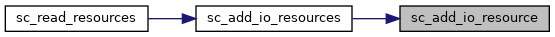

Definition at line 181 of file southcluster.c.

References base, LPC_DEFAULT_IO_RANGE_LOWER, and LPC_DEFAULT_IO_RANGE_UPPER.

Referenced by sc_add_io_resource().

|

static |

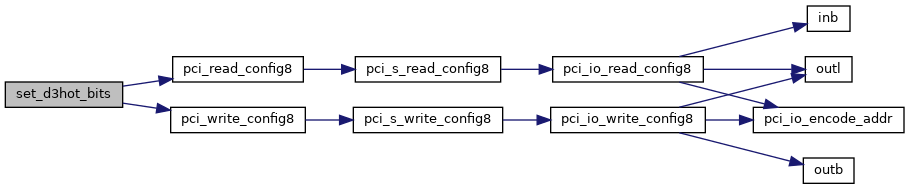

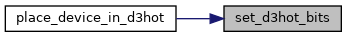

Definition at line 424 of file southcluster.c.

References DEV_CASE, pci_path::devfn, HDA_DEV, HDA_FUNC, hda_work_around(), I2C1, I2C2, I2C3, I2C4, I2C5, I2C6, I2C7, offset, device::path, device_path::pci, PCI_CAP_ID_PM, PCI_DEVFN, pci_find_capability(), SD, set_d3hot_bits(), and SMBUS.

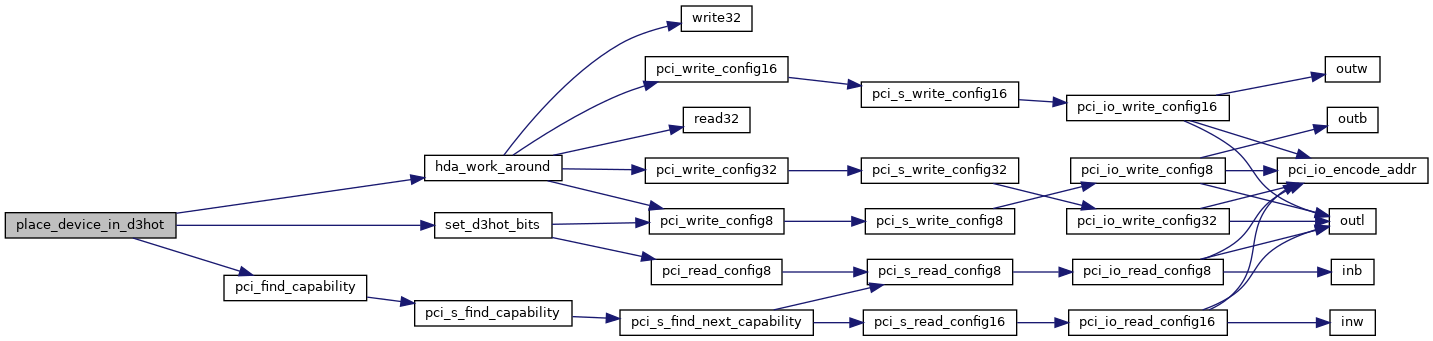

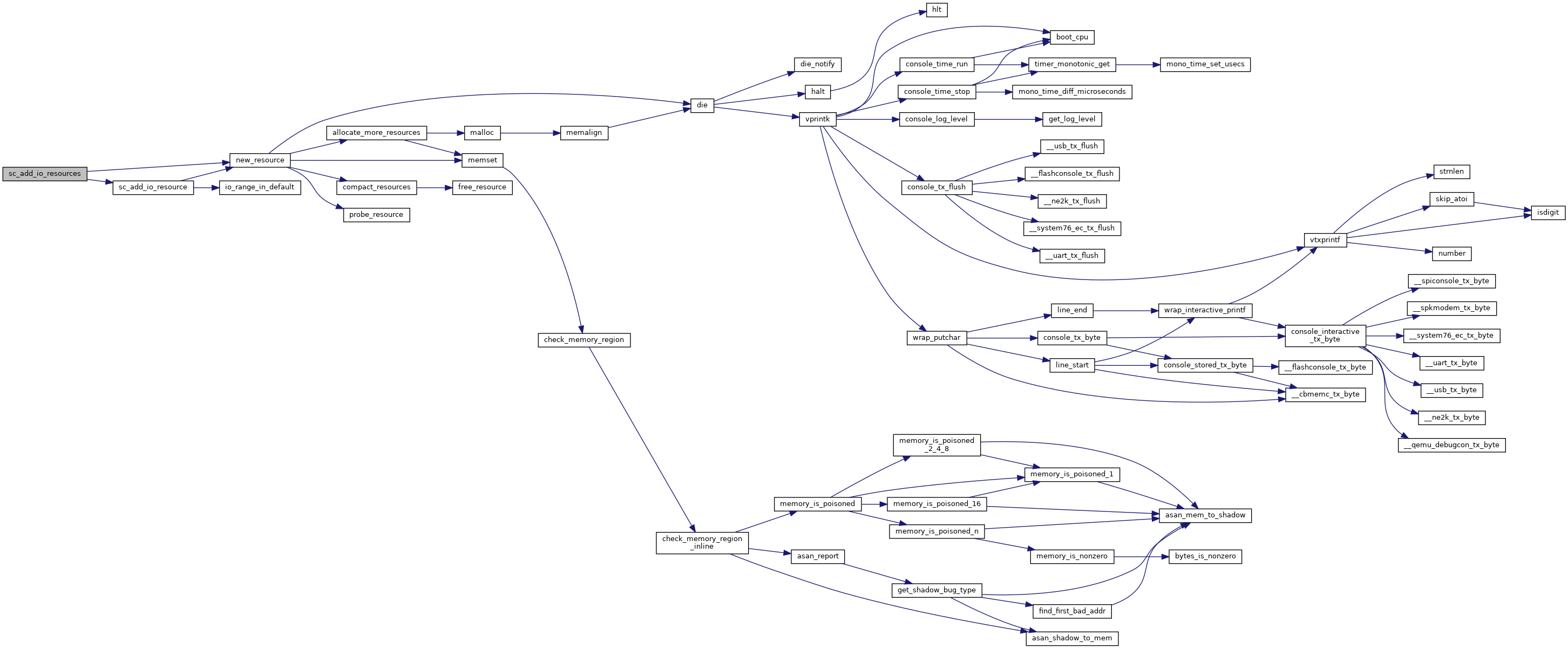

Definition at line 199 of file southcluster.c.

References resource::base, base, resource::flags, resource::index, io_range_in_default(), IORESOURCE_ASSIGNED, IORESOURCE_FIXED, IORESOURCE_IO, new_resource(), and resource::size.

Referenced by sc_add_io_resources().

Definition at line 212 of file southcluster.c.

References ABASE, ACPI_BASE_ADDRESS, ACPI_BASE_SIZE, resource::base, resource::flags, GBASE, GPIO_BASE_ADDRESS, GPIO_BASE_SIZE, IORESOURCE_ASSIGNED, IORESOURCE_FIXED, IORESOURCE_IO, LPC_DEFAULT_IO_RANGE_LOWER, LPC_DEFAULT_IO_RANGE_UPPER, new_resource(), sc_add_io_resource(), and resource::size.

Referenced by sc_read_resources().

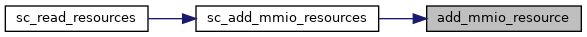

Definition at line 54 of file southcluster.c.

References ABORT_BASE_ADDRESS, ABORT_BASE_SIZE, add_mmio_resource(), IBASE, ILB_BASE_ADDRESS, ILB_BASE_SIZE, IO_APIC_ADDR, IO_BASE_ADDRESS, IO_BASE_SIZE, IOBASE, KiB, MPBASE, MPHY_BASE_ADDRESS, MPHY_BASE_SIZE, PBASE, PMC_BASE_ADDRESS, PMC_BASE_SIZE, PUBASE, PUNIT_BASE_ADDRESS, PUNIT_BASE_SIZE, RCBA, RCBA_BASE_ADDRESS, RCBA_BASE_SIZE, SBASE, SPI_BASE_ADDRESS, and SPI_BASE_SIZE.

Referenced by sc_read_resources().

Definition at line 305 of file southcluster.c.

References pci_path::devfn, FUNC_DIS, FUNC_DIS2, I2C1, I2C2, I2C3, I2C4, I2C5, I2C6, I2C7, mask, device::path, device_path::pci, PMC_BASE_ADDRESS, read32(), SD, SET_DIS_MASK, SET_DIS_MASK2, SMBUS, USH_SS_PHY_DIS, and write32().

Definition at line 241 of file southcluster.c.

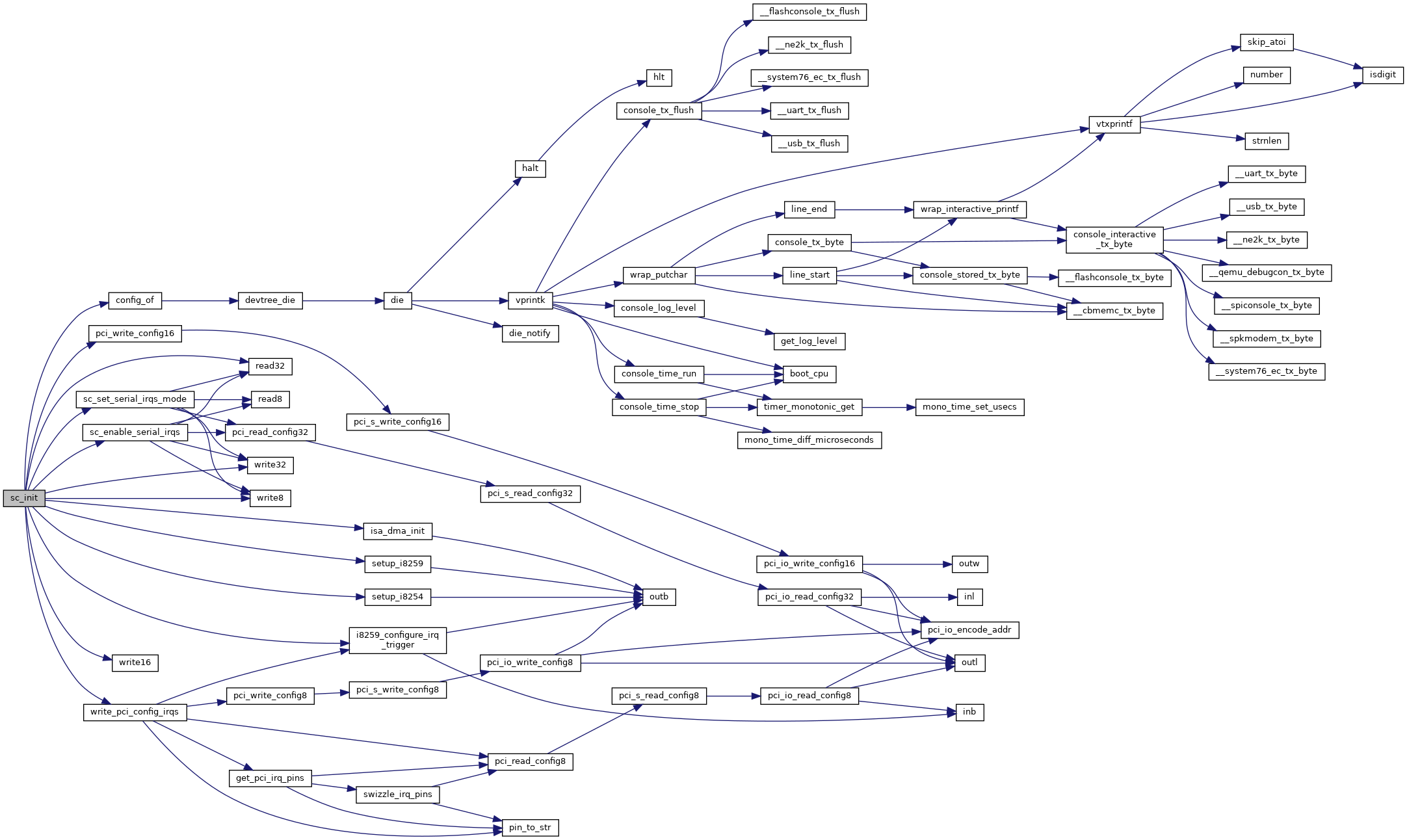

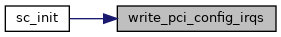

References ACTL, BIOS_DEBUG, config, config_of(), DIS_SLP_X_STRCH_SUS_UP, GEN_PMCON1, global_soc_irq_route, i8259_configure_irq_trigger(), ILB_BASE_ADDRESS, isa_dma_init(), NUM_IR_DEVS, NUM_PIRQS, PCI_COMMAND, PCI_COMMAND_IO, PCI_COMMAND_MASTER, PCI_COMMAND_MEMORY, PCI_COMMAND_SPECIAL, pci_write_config16(), soc_irq_route::pcidev, soc_irq_route::pic, PMC_BASE_ADDRESS, printk, read32(), sc_enable_serial_irqs(), sc_set_serial_irqs_mode(), setup_i8254(), setup_i8259(), write16(), write32(), write8(), and write_pci_config_irqs().

Definition at line 229 of file southcluster.c.

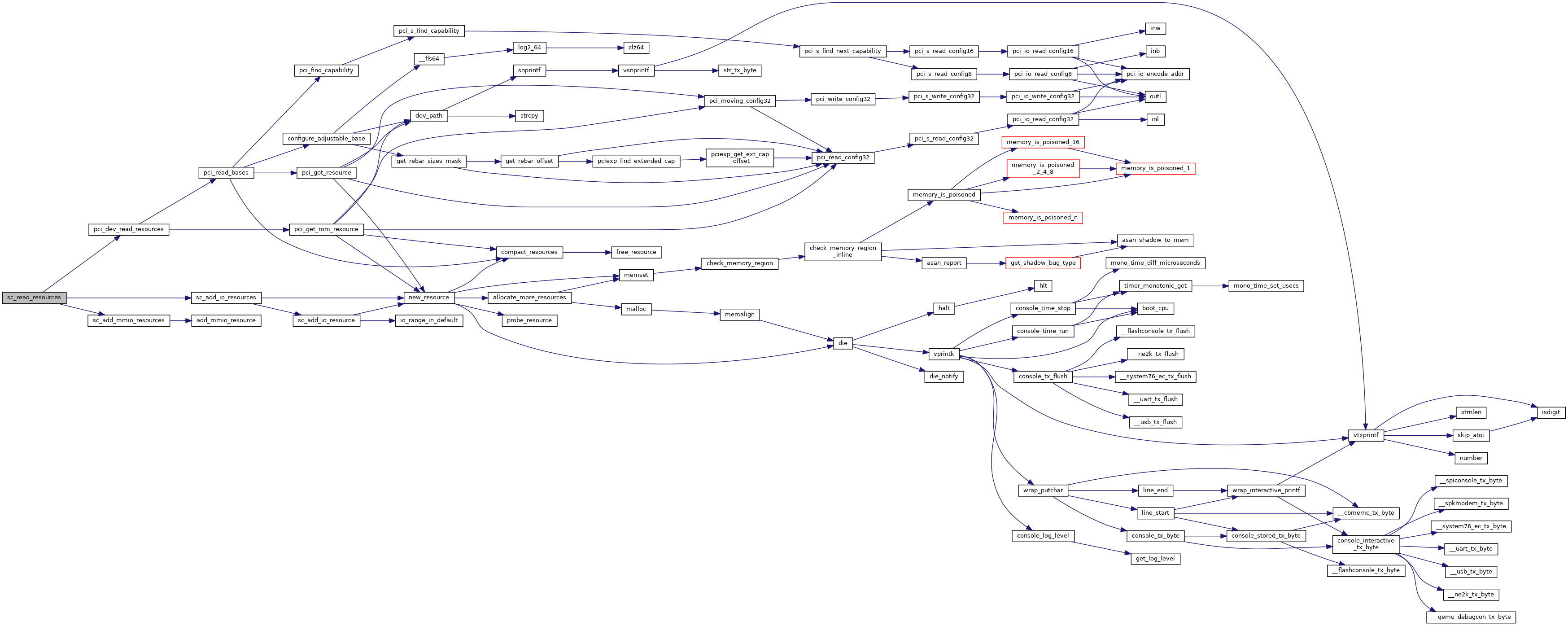

References pci_dev_read_resources(), sc_add_io_resources(), and sc_add_mmio_resources().

|

static |

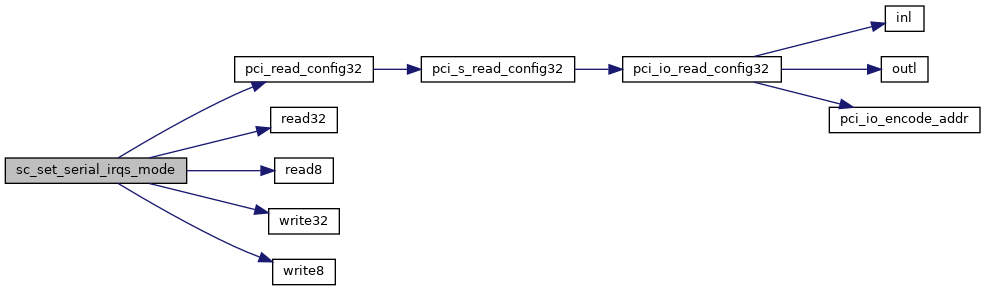

Definition at line 29 of file southcluster.c.

References IBASE, ILB_OIC, pci_read_config32(), read32(), read8(), SCNT, SCNT_MODE, SERIRQ_CONTINUOUS, SERIRQ_OFF, SERIRQ_QUIET, SIRQEN, write32(), and write8().

Referenced by sc_init().

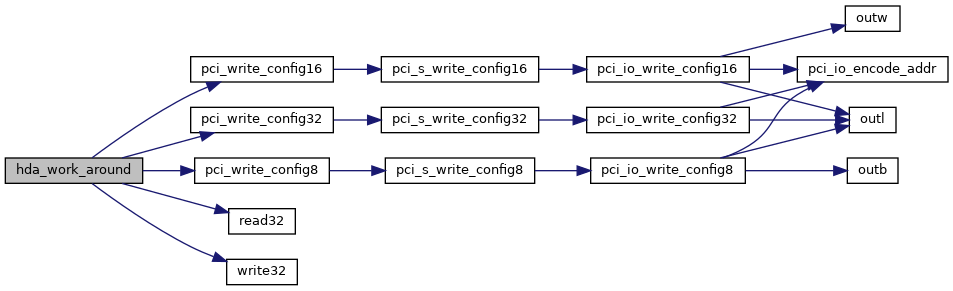

Definition at line 392 of file southcluster.c.

References BIOS_DEBUG, offset, pci_read_config8(), pci_write_config8(), and printk.

Referenced by place_device_in_d3hot().

Definition at line 500 of file southcluster.c.

Definition at line 95 of file southcluster.c.

References all_devices, BIOS_DEBUG, BIOS_SPEW, BIOS_WARNING, device::bus, pci_path::devfn, DEVICE_PATH_PCI, device::enabled, get_pci_irq_pins(), global_soc_irq_route, i8259_configure_irq_trigger(), IRQ_LEVEL_TRIGGERED, device::next, NULL, device::path, device_path::pci, PCI_INTERRUPT_LINE, PCI_INTERRUPT_PIN, pci_read_config8(), PCI_SLOT, pci_write_config8(), soc_irq_route::pcidev, soc_irq_route::pic, pin_to_str(), PIRQ_PIC_IRQDISABLE, PIRQ_PIC_UNKNOWN_UNUSED, printk, bus::secondary, and device_path::type.

Referenced by sc_init().

|

static |

Definition at line 500 of file southcluster.c.

|

static |

Definition at line 500 of file southcluster.c.