|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

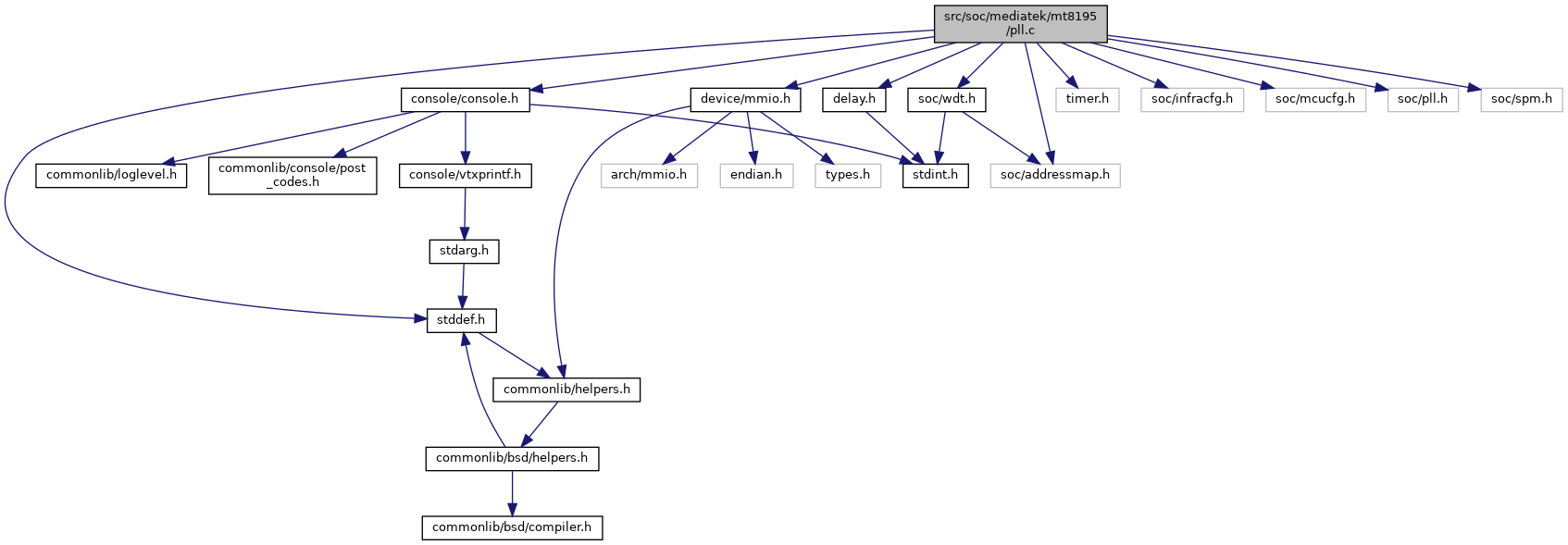

#include <console/console.h>#include <device/mmio.h>#include <delay.h>#include <stddef.h>#include <timer.h>#include <soc/addressmap.h>#include <soc/infracfg.h>#include <soc/mcucfg.h>#include <soc/pll.h>#include <soc/spm.h>#include <soc/wdt.h>

Go to the source code of this file.

Data Structures | |

| struct | mt8195_infracfg_ao_bcrm_regs |

| struct | mt8195_pericfg_ao_regs |

| struct | mt8195_scp_adsp_regs |

| struct | mux_sel |

| struct | rate |

Macros | |

| #define | MUX(_id, _reg, _mux_shift, _mux_width) |

| #define | MUX_UPD(_id, _reg, _mux_shift, _mux_width, _upd_reg, _upd_shift) |

Functions | |

| check_member (mt8195_infracfg_ao_bcrm_regs, vdnr_dcm_top_infra_ctrl0, 0x0034) | |

| check_member (mt8195_pericfg_ao_regs, peri_module_sw_cg_0_set, 0x0010) | |

| check_member (mt8195_scp_adsp_regs, audiodsp_ck_cg, 0x0180) | |

| void | pll_set_pcw_change (const struct pll *pll) |

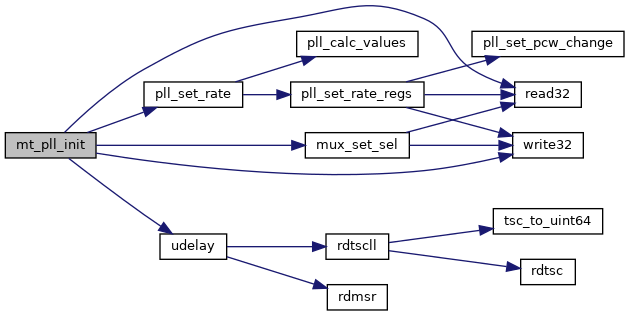

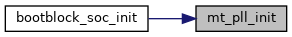

| void | mt_pll_init (void) |

| void | mt_pll_raise_little_cpu_freq (u32 freq) |

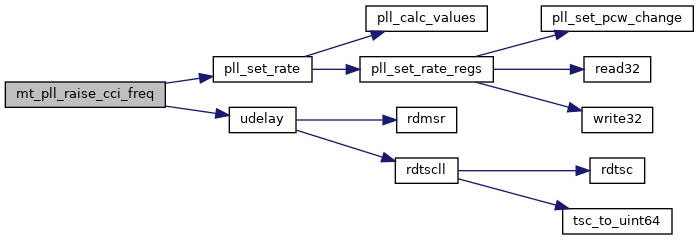

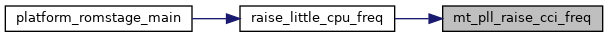

| void | mt_pll_raise_cci_freq (u32 freq) |

| void | mt_pll_set_tvd_pll1_freq (u32 freq) |

| void | edp_mux_set_sel (u32 sel) |

| u32 | mt_fmeter_get_freq_khz (enum fmeter_type type, u32 id) |

Variables | |

| static struct mt8195_infracfg_ao_bcrm_regs *const | mt8195_infracfg_ao_bcrm |

| static struct mt8195_pericfg_ao_regs *const | mt8195_pericfg_ao = (void *)PERICFG_AO_BASE |

| static struct mt8195_scp_adsp_regs *const | mt8195_scp_adsp |

| static const struct mux | muxes [] |

| static const struct mux_sel | mux_sels [] |

| static const u32 | pll_div_rate [] |

| static const struct pll | plls [] |

| static const struct rate | rates [] |

| #define MUX | ( | _id, | |

| _reg, | |||

| _mux_shift, | |||

| _mux_width | |||

| ) |

| #define MUX_UPD | ( | _id, | |

| _reg, | |||

| _mux_shift, | |||

| _mux_width, | |||

| _upd_reg, | |||

| _upd_shift | |||

| ) |

| enum mux_id |

| enum pll_id |

| check_member | ( | mt8195_infracfg_ao_bcrm_regs | , |

| vdnr_dcm_top_infra_ctrl0 | , | ||

| 0x0034 | |||

| ) |

| check_member | ( | mt8195_pericfg_ao_regs | , |

| peri_module_sw_cg_0_set | , | ||

| 0x0010 | |||

| ) |

| check_member | ( | mt8195_scp_adsp_regs | , |

| audiodsp_ck_cg | , | ||

| 0x0180 | |||

| ) |

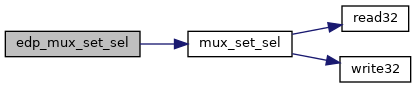

Definition at line 830 of file pll.c.

References mux_set_sel(), muxes, and TOP_EDP_SEL.

Referenced by mtk_dpintf_power_on().

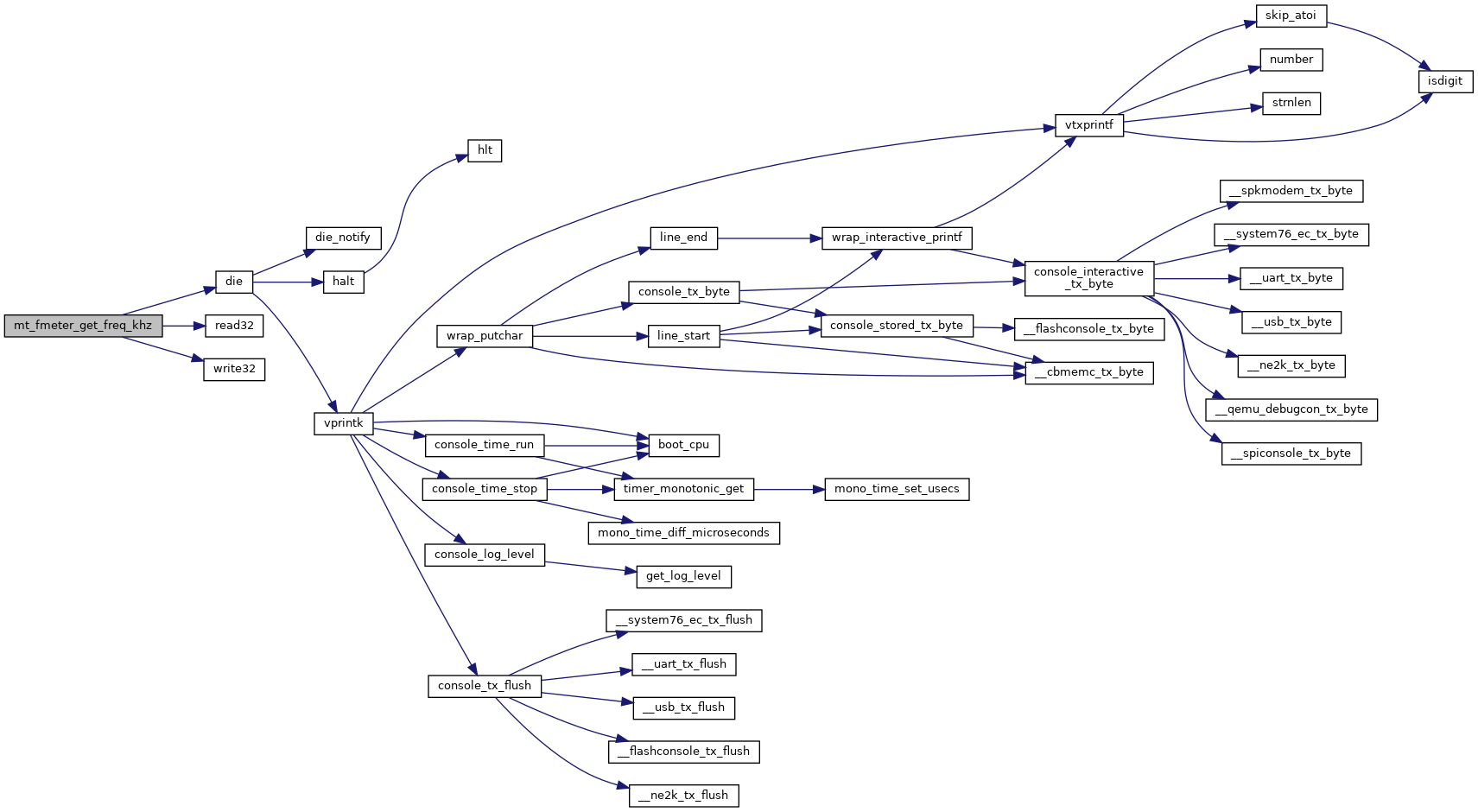

| u32 mt_fmeter_get_freq_khz | ( | enum fmeter_type | type, |

| u32 | id | ||

| ) |

Definition at line 835 of file pll.c.

References BIOS_WARNING, count, die(), FMETER_ABIST, FMETER_CKGEN, mtk_topckgen, printk, read32(), READ32_BITFIELD, SET32_BITFIELDS, type, wait_us, and write32().

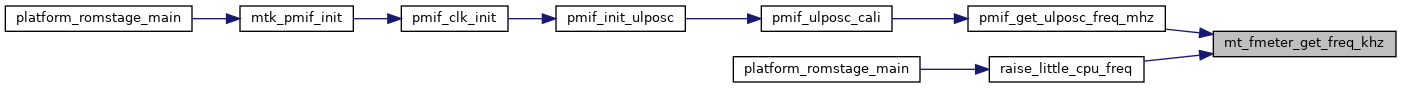

Referenced by pmif_get_ulposc_freq_mhz(), and raise_little_cpu_freq().

Definition at line 644 of file pll.c.

References mtk_spm_regs::ap_mdsrc_req, APMIXED_APLL5, APMIXED_NR_PLL, APMIXED_PLL_MAX, ARRAY_SIZE, mt8195_scp_adsp_regs::audiodsp_ck_cg, BIT, mt8186_mcucfg_regs::bus_plldiv_cfg, clrbits32, clrsetbits32, mt8186_mcucfg_regs::cpu_plldiv_cfg0, mt8186_mcucfg_regs::cpu_plldiv_cfg1, GLITCH_FREE_EN, mt8195_infracfg_ao_regs::infra_aximem_idle_bit_en_0, mt8195_infracfg_ao_regs::infra_bus_dcm_ctrl, INFRACFG_AO_AXIMEM_BUS_DCM_REG0_MASK, INFRACFG_AO_AXIMEM_BUS_DCM_REG0_ON, INFRACFG_AO_INFRA_BUS_DCM_REG0_MASK, INFRACFG_AO_INFRA_BUS_DCM_REG0_ON, INFRACFG_AO_INFRA_RX_P2P_DCM_REG0_MASK, INFRACFG_AO_INFRA_RX_P2P_DCM_REG0_ON, INFRACFG_AO_PERI_BUS_DCM_REG0_MASK, INFRACFG_AO_PERI_BUS_DCM_REG0_ON, INFRACFG_AO_PERI_MODULE_DCM_REG0_MASK, INFRACFG_AO_PERI_MODULE_DCM_REG0_ON, MCU_DIV_1, MCU_DIV_MASK, MCU_MUX_MASK, MCU_MUX_SRC_PLL, MHz, mt8195_infracfg_ao_regs::module_sw_cg_0_clr, mt8195_infracfg_ao_regs::module_sw_cg_1_clr, mt8195_infracfg_ao_regs::module_sw_cg_2_clr, mt8195_infracfg_ao_regs::module_sw_cg_3_clr, mt8173_infracfg, MT8195_APLL5_EN, mt8195_infracfg_ao, mt8195_infracfg_ao_bcrm, mt8195_pericfg_ao, MT8195_PLL_EN, mt8195_scp_adsp, mtk_apmixed, mtk_mcucfg, mtk_spm, mtk_topckgen, mux_sels, mux_set_sel(), muxes, NO_RSTB_SHIFT, mt8195_infracfg_ao_regs::p2p_rx_clk_on, mt8195_infracfg_ao_regs::peri_bus_dcm_ctrl, mt8195_pericfg_ao_regs::peri_module_sw_cg_0_set, PLL_CKSQ_ON_DELAY, PLL_DIV_EN, PLL_EN, PLL_EN_DELAY, PLL_ISO, PLL_ISO_DELAY, PLL_PWR_ON, PLL_PWR_ON_DELAY, pll_set_rate(), plls, rates, read32(), setbits32, mt8173_infracfg_regs::top_dcmctl, udelay(), mt8195_infracfg_ao_bcrm_regs::vdnr_dcm_top_infra_ctrl0, and write32().

Referenced by bootblock_soc_init().

Definition at line 798 of file pll.c.

References APMIXED_CCIPLL, mt8186_mcucfg_regs::bus_plldiv_cfg, clrbits32, clrsetbits32, MCU_MUX_MASK, MCU_MUX_SRC_26M, MCU_MUX_SRC_PLL, MT8186_PLL_EN, MT8195_PLL_EN, mtk_mcucfg, PLL_EN_DELAY, pll_set_rate(), plls, setbits32, and udelay().

Referenced by raise_little_cpu_freq().

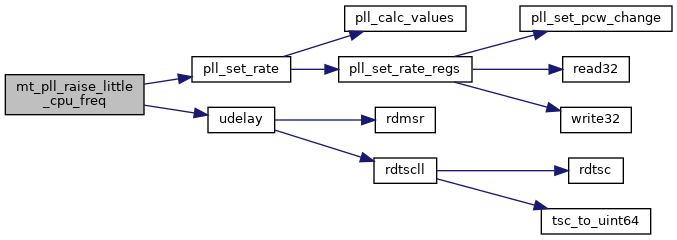

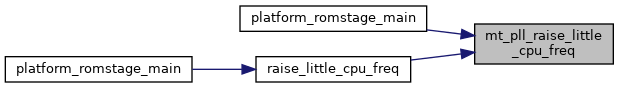

Definition at line 779 of file pll.c.

References APMIXED_ARMCA7PLL, APMIXED_ARMPLL_LL, clrbits32, clrsetbits32, mt8186_mcucfg_regs::cpu_plldiv_cfg0, MCU_MUX_MASK, MCU_MUX_SRC_26M, MCU_MUX_SRC_PLL, MT8195_PLL_EN, mtk_mcucfg, PLL_EN_DELAY, pll_set_rate(), plls, setbits32, and udelay().

Referenced by platform_romstage_main(), and raise_little_cpu_freq().

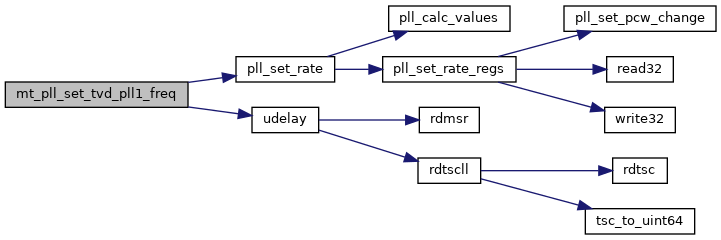

Definition at line 817 of file pll.c.

References APMIXED_TVDPLL1, clrbits32, MT8195_PLL_EN, PLL_EN_DELAY, pll_set_rate(), plls, setbits32, and udelay().

Referenced by mtk_dpintf_power_on().

Definition at line 639 of file pll.c.

References pll::div_reg, pll::pcw_reg, PLL_PCW_CHG, and setbits32.

|

static |

Definition at line 21 of file pll.c.

Referenced by mt_pll_init().

|

static |

Definition at line 29 of file pll.c.

Referenced by mt_pll_init().

|

static |

Definition at line 36 of file pll.c.

Referenced by mt_pll_init().

|

static |

Definition at line 36 of file pll.c.

Referenced by mt_pll_init().

|

static |

Definition at line 36 of file pll.c.

Referenced by edp_mux_set_sel(), and mt_pll_init().

|

static |

|

static |

Definition at line 515 of file pll.c.

Referenced by mt_pll_init(), mt_pll_raise_cci_freq(), mt_pll_raise_little_cpu_freq(), and mt_pll_set_tvd_pll1_freq().

|

static |

Definition at line 515 of file pll.c.

Referenced by mt_pll_init().