|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

#include <stdint.h>

Go to the source code of this file.

Functions | |

| void | bootblock_mainboard_early_init (void) |

| void | bootblock_soc_early_init (void) |

| void | bootblock_soc_init (void) |

| void | bootblock_mainboard_init (void) |

| void | bootblock_main (const uint64_t reg_x0, const uint64_t reg_pc) |

Definition at line 17 of file bootblock.c.

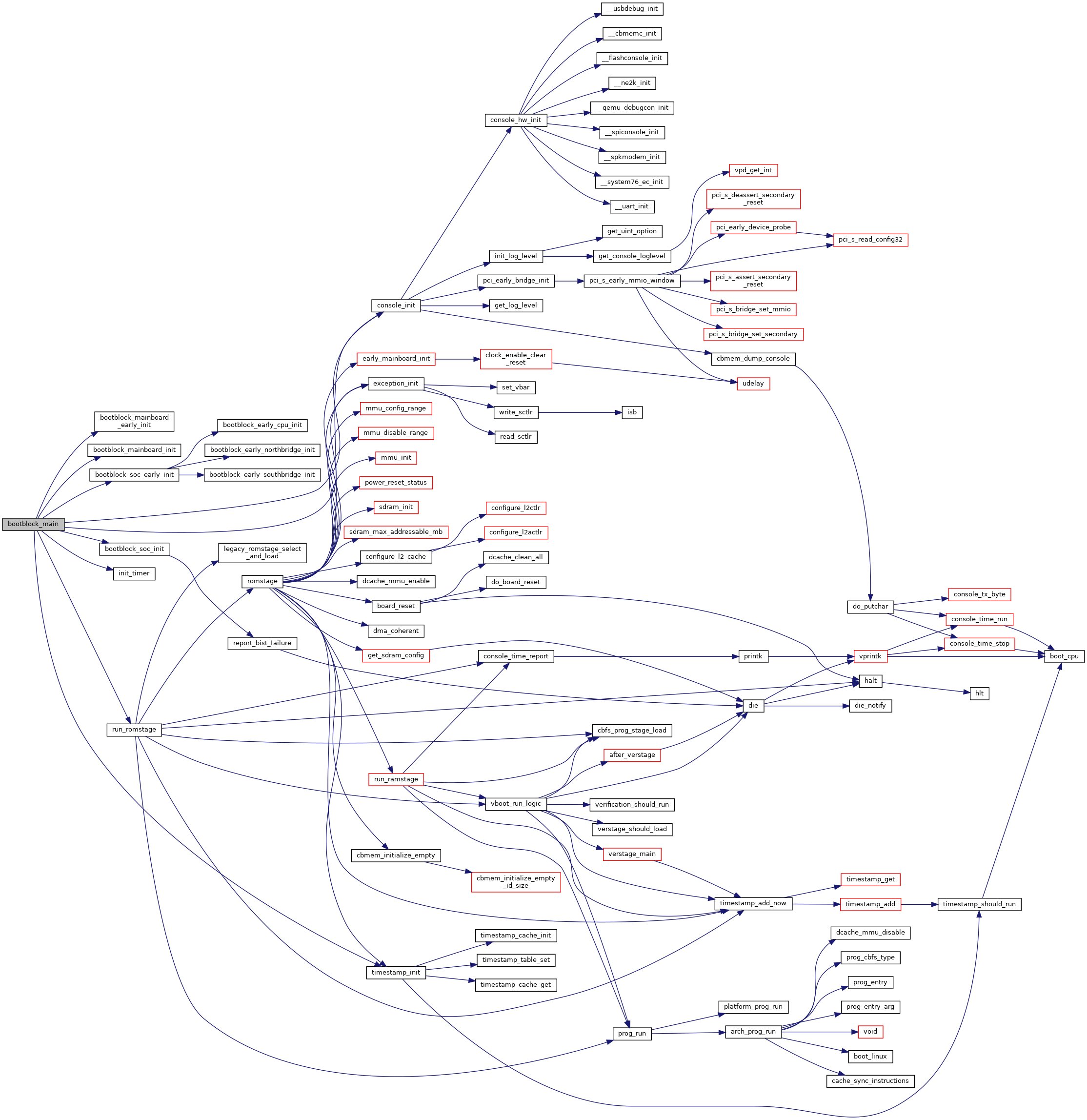

References BIOS_ERR, bootblock_mainboard_early_init(), bootblock_mainboard_init(), bootblock_soc_early_init(), bootblock_soc_init(), CONFIG, console_init(), exception_init(), init_timer(), printk, REGION_SIZE, run_romstage(), timestamp_get, and timestamp_init().

Definition at line 16 of file bootblock.c.

References _Static_assert(), ACPI_DEV, acpi_get_sleep_type(), am335x_cm_per, am335x_cm_wkup, am335x_disable_gpio_irqs(), am335x_pinmux_uart0(), am335x_pinmux_uart1(), am335x_pinmux_uart2(), am335x_pinmux_uart3(), am335x_pinmux_uart4(), am335x_pinmux_uart5(), ARRAY_SIZE, ASPEED_CONFIG_INDEX, aspeed_enable_port80_direct_gpio(), aspeed_enable_serial(), aspeed_enable_uart_pin(), ASPEED_SIO_PORT, assert, AST2400_GPIO, AST2400_SUART1, BEAGLEBONE_LED_USR0, BEAGLEBONE_LED_USR1, BEAGLEBONE_LED_USR2, BEAGLEBONE_LED_USR3, beaglebone_leds_init(), beaglebone_leds_set(), BIOS_DEBUG, bmc_init(), BUC_LAND, CLKIN_DEV, clrbits32, CM_FCLK_EN, CM_ST_SW_WKUP, CNF1_LPC_EN, CNF2_LPC_EN, com_to_ast_sio(), COMA_LPC_EN, COMB_LPC_EN, CONFIG, configure_early_gpio_pads(), D27IP, D27IR, D28IP, D29IP, D29IR, D30IP, D30IR, D31IP, D31IR, DECODE_ENABLE_SERIAL_PORT0, DECODE_ENABLE_SERIAL_PORT1, dlpc_init(), dock_connect(), dock_err, dock_present(), early_config_gpio(), early_config_superio(), early_gpio_table, early_superio_config(), EC_DEV, ec_set_bit(), ELGON_GPIO_ERROR_LED, ELGON_GPIO_UART_SEL, enable_espi_lpc_io_windows(), enable_serial(), ENVC_DEV, espi_disable_lpc_ldrq(), espi_switch_to_spi1_pads(), espi_switch_to_spi2_pads(), FC350_PCIE_INIT_DELAY_US, fch_clk_output_48Mhz(), FD, FD_INTLAN, fintek_enable_serial(), GEN2_DEC, get_cpufanin_gpio_config(), GLOBAL_DEV, GP_SOUTHWEST, rk3399_pmugrf_regs::gpio0b_iomux, am335x_cm_per_regs::gpio1, am335x_cm_per_regs::gpio2, am335x_cm_per_regs::gpio3, GPIO6789_DEV, gpio_100_write8(), gpio_configure_pads(), gpio_configure_pads_with_override(), GPIO_DEV, gpio_init(), gpio_output(), GPIO_P15V_EN, GPIO_P30V_EN, gpio_pad_config_reg(), gpio_table, GPIOH, HOST_BRIDGE, hudson_clk_output_48Mhz(), hudson_lpc_port80(), hwm_init(), i82801gx_setup_bars(), inb(), init_cpld(), rk3399_grf_regs::io_vsel, rk3288_grf_regs::iomux_uart2, IOMUX_UART2, rk3399_grf_regs::iomux_uart2c, IOMUX_UART2C, IT8728F_EC, it8772f_ac_resume_southbridge(), IT8772F_GPIO_DEV, IT8772F_SERIAL_DEV, IT8772F_SUPERIO_DEV, IT8783EF_GPIO, ite_conf_clkin(), ite_delay_pwrgd3(), ite_enable_3vsbsw(), ite_enable_serial(), ite_evc_conf(), ite_gpio_conf(), ite_kill_watchdog(), ite_reg_write(), ITE_UART_CLK_PREDIVIDE_24, ITE_UART_CLK_PREDIVIDE_48, kbc1100_early_init(), kbc1100_early_serial(), kbc1126_com1_init(), kbc1126_disable4e(), kbc1126_ec_init(), kbc1126_enter_conf(), kbc1126_exit_conf(), kbc1126_kbc_init(), kbc1126_mailbox_init(), kbc1126_pm1_init(), KBC_LPC_EN, kempld_enable_uart_for_console(), LED_ON, legacy_io_init(), legacy_io_present(), lpc47m10x_enable_serial(), lpc47m15x_enable_serial(), lpc47n217_enable_serial(), lpc47n227_enable_serial(), LPC_DEV, LPC_EN, lpc_enable_decode(), lpc_enable_sio_decode(), LPC_IO_DEC, LPC_SELECT_SIO_4E4F, lpc_set_wideio_range(), M2, mainboard_config_stage_gpios(), mainboard_configure_early_gpios(), mainboard_configure_super_io(), mainboard_early_bootblock_gpio_table(), mainboard_ec_init(), mainboard_gpio_map, mainboard_program_early_gpios(), MCHBAR, mchbar_write16(), misc_read32(), misc_write32(), mt8173_pericfg, nct5104d_enable_uartd(), NCT6776_ACPI, nuvoton_enable_serial(), nuvoton_pnp_enter_conf_state(), nuvoton_pnp_exit_conf_state(), outb(), PAD_CONFIG0_DEFAULT0, pc87382_early(), PCH_DEV_LPC, PCI_DEV, pci_or_config16(), pci_read_config8(), pci_s_write_config32(), pci_write_config16(), pci_write_config32(), pci_write_config8(), pcie_init_timeout_sw, pcr_write32(), mt8173_pericfg_regs::pdn0_set, PERICFG_UART0_PDN, PID_DMI, pm_io_write8(), pm_write8(), PME_DEV, PNP_DEV, pnp_enter_conf_state(), pnp_enter_ext_func_mode(), pnp_exit_conf_state(), pnp_exit_ext_func_mode(), PNP_IDX_EN, PNP_IDX_IO0, PNP_IDX_IO1, PNP_IDX_IRQ0, PNP_IDX_MSC0, PNP_IDX_MSC1, PNP_IDX_MSC3, PNP_IDX_MSC5, pnp_read_config(), pnp_set_enable(), pnp_set_iobase(), pnp_set_irq(), pnp_set_logical_device(), pnp_write_config(), post_code, printk, program_early_gpio_pads(), RCBA16, RCBA32, RCBA_BUC, RCBA_CG, rk3288_grf, rk3399_grf, rk3399_pmugrf, RK_CLRBITS, RK_SETBITS, sbxxx_enable_48mhzout(), sch5545_early_init(), sch5545_ec_early_init(), sch5545_emi_disable_interrupts(), sch5545_emi_init(), sch5545_enable_uart(), SERIAL1_DEV, SERIAL2_DEV, SERIAL3_DEV, SERIAL4_DEV, SERIAL5_DEV, SERIAL6_DEV, SERIAL_DEV, SERIAL_DEV1, SERIAL_DEV2, SERIAL_DEV_R1, SERIAL_DEV_R2, SERIRQ_CNTL, SET_PAD_MODE_SELECTION, set_power_led(), setup_pch_gpios(), setup_sio_gpios(), sio1007_enable_uart_at(), sio1007_setreg(), sio1036_enable_serial(), SIO_DEV, SIO_GPIO, SIO_PORT, smscsuperio_enable_serial(), rk3399_pmugrf_regs::soc_con0, rk3399_grf_regs::soc_con7, soc_configure_pads(), SSKPD_HI, stopwatch_init_usecs_expire(), SUPERIO_DEV, SUPERIO_GPIO, superio_init(), superio_init_m(), superio_init_m_pro(), try_enabling_LPC47N207_uart(), am335x_cm_per_regs::uart1, UART1_RXD_PAD, UART1_TXD_PAD, am335x_cm_per_regs::uart2, UART2_BASE, UART2C_SEL, am335x_cm_per_regs::uart3, am335x_cm_per_regs::uart4, am335x_cm_per_regs::uart5, uart_console_pads, UART_CONT, UART_DEV, uart_is_enabled(), uart_setup(), val, variant_bootblock_gpio_table(), variant_configure_early_gpio_pads(), variant_configure_early_gpios(), variant_early_gpio_configure(), variant_early_gpio_table(), variant_early_override_gpio_table(), variant_espi_gpio_table(), variant_pcie_gpio_configure(), variant_tpm_gpio_table(), variant_wlan_rst_early_gpio_table(), W83627EHG_FDC, W83627EHG_GPIO2, W83627EHG_GPIO3, W83627EHG_HWM, W83627EHG_KBC, W83627EHG_PP, W83627EHG_SP1, W83627EHG_SP2, W83627THG_FDC, W83627THG_GAME_MIDI_GPIO1, W83627THG_GPIO2, W83627THG_GPIO3, W83627THG_HWM, W83627THG_KBC, W83627THG_PP, W83627THG_SP1, W83627THG_SP2, winbond_enable_serial(), am335x_cm_wkup_regs::wkup_gpio0, am335x_cm_wkup_regs::wkup_uart0, and write32().

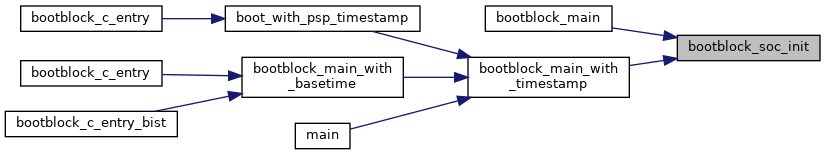

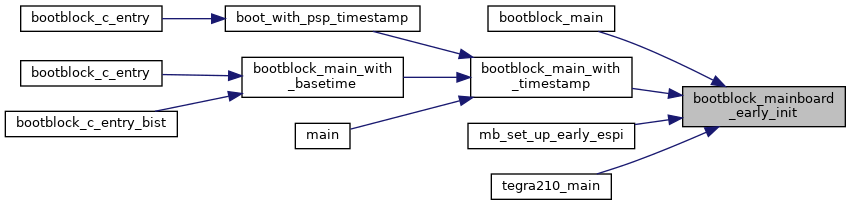

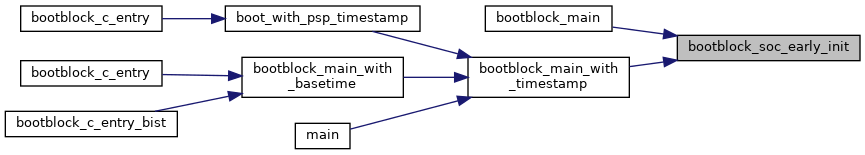

Referenced by bootblock_main(), bootblock_main_with_timestamp(), mb_set_up_early_espi(), and tegra210_main().

Definition at line 19 of file bootblock.c.

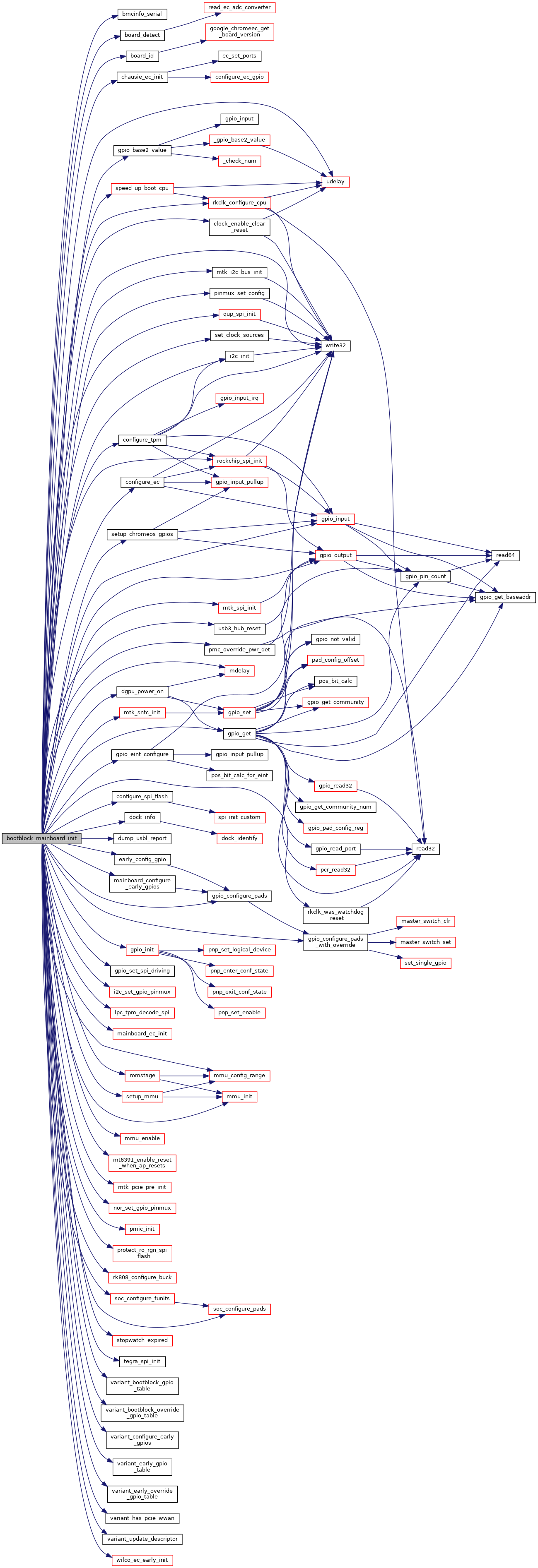

References _dram, _ewifi_imem_0, _wifi_imem_0, APLL_1416_MHZ, APLL_1800_MHZ, ARRAY_SIZE, assert, BIOS_DEBUG, BIOS_ERR, BIOS_INFO, BIOS_SPEW, bmcinfo_serial(), board_detect(), board_id(), chausie_ec_init(), CLK_H_APBDMA, CLK_H_I2C5, CLK_L_CACHE2, CLK_L_TMR, CLK_V_MSELECT, clock_enable_clear_reset(), CONFIG, configure_ec(), configure_spi_flash(), configure_tpm(), dgpu_power_on(), dock_err, dock_info(), DRAM_NOT_INITIALIZED, dump_usbl_report(), early_config_gpio(), early_gpio_table, uber_sbl_shared_info::end_magic, funits, GiB, GPIO, gpio_base2_value(), gpio_configure_pads(), gpio_configure_pads_with_override(), GPIO_EINT_1P8V, gpio_eint_configure(), gpio_get(), GPIO_GSC_AP_INT, GPIO_GSC_AP_INT_ODL, GPIO_H1_AP_INT, gpio_init(), gpio_input(), gpio_output(), gpio_set_spi_driving(), GPP_H10, GPP_H15, GPP_H16, GPP_H17, GPP_K12, GPP_K13, GPP_K14, GPP_K16, I2C2_BUS, I2C3_BUS, i2c_init(), i2c_set_gpio_pinmux(), I2C_SPEED_FAST, I2CPWR_BUS, uber_sbl_shared_info::info, rk3288_pmu_regs::iomux_i2c0scl, IOMUX_I2C0SCL, rk3288_pmu_regs::iomux_i2c0sda, IOMUX_I2C0SDA, rk3288_grf_regs::iomux_i2c1, IOMUX_I2C1, rk3288_grf_regs::iomux_spi0, IOMUX_SPI0, IOMUX_SPI2_CSCLK, IOMUX_SPI2_TXRX, rk3288_grf_regs::iomux_spi2csclk, rk3288_grf_regs::iomux_spi2txrx, IRQ_TYPE_EDGE_RISING, KHz, lpc_tpm_decode_spi(), MA_DEV, MA_MEM, MA_RW, MA_S, mainboard_configure_early_gpios(), mainboard_ec_init(), maskrom_param, mdelay(), MHz, mmu_config_range(), mmu_enable(), mmu_init(), mt6391_enable_reset_when_ap_resets(), mtk_i2c_bus_init(), mtk_pcie_pre_init(), mtk_snfc_init(), mtk_spi_init(), nor_set_gpio_pinmux(), uber_sbl_shared_info::num, padcfgs, pcie_init_timeout_sw, PINMUX_INPUT_ENABLE, PINMUX_PULL_UP, pinmux_set_config(), PMC_AUDIO_RAIL_AO_DISABLE, PMC_AUDIO_RAIL_AO_MASK, PMC_GPIO_RAIL_AO_DISABLE, PMC_GPIO_RAIL_AO_MASK, pmc_override_pwr_det(), PMC_SDMMC3_RAIL_AO_DISABLE, PMC_SDMMC3_RAIL_AO_MASK, pmic_init(), printk, protect_ro_rgn_spi_flash(), qup_spi_init(), REGION_SIZE, rk3288_grf, rk3288_pmu, rk808_configure_buck(), rkclk_configure_cpu(), rkclk_was_watchdog_reset(), rockchip_spi_init(), romstage(), set_clock_sources(), setbits32, setup_chromeos_gpios(), setup_mmu(), soc_configure_funits(), soc_configure_pads(), speed_up_boot_cpu(), SPI_NOR_GPIO_SET1, SPI_PAD0_MASK, SPI_PAD1_MASK, uber_sbl_shared_info::start_magic, stopwatch_expired(), tegra_spi_init(), UBER_SBL_SHARED_INFO_END_MAGIC, UBER_SBL_SHARED_INFO_START_MAGIC, udelay(), usb3_hub_reset(), variant_bootblock_gpio_table(), variant_bootblock_override_gpio_table(), variant_configure_early_gpios(), variant_early_gpio_table(), variant_early_override_gpio_table(), variant_has_pcie_wwan(), variant_update_descriptor(), uber_sbl_shared_info::version, wilco_ec_early_init(), and write32().

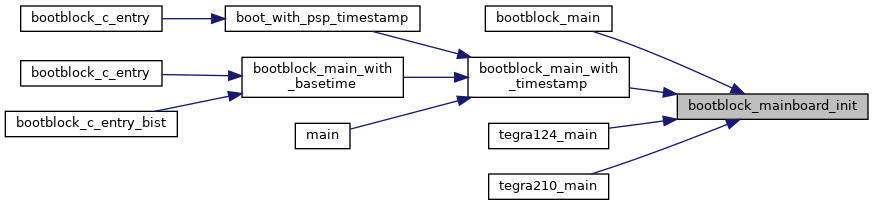

Referenced by bootblock_main(), bootblock_main_with_timestamp(), tegra124_main(), and tegra210_main().

Definition at line 20 of file bootblock.c.

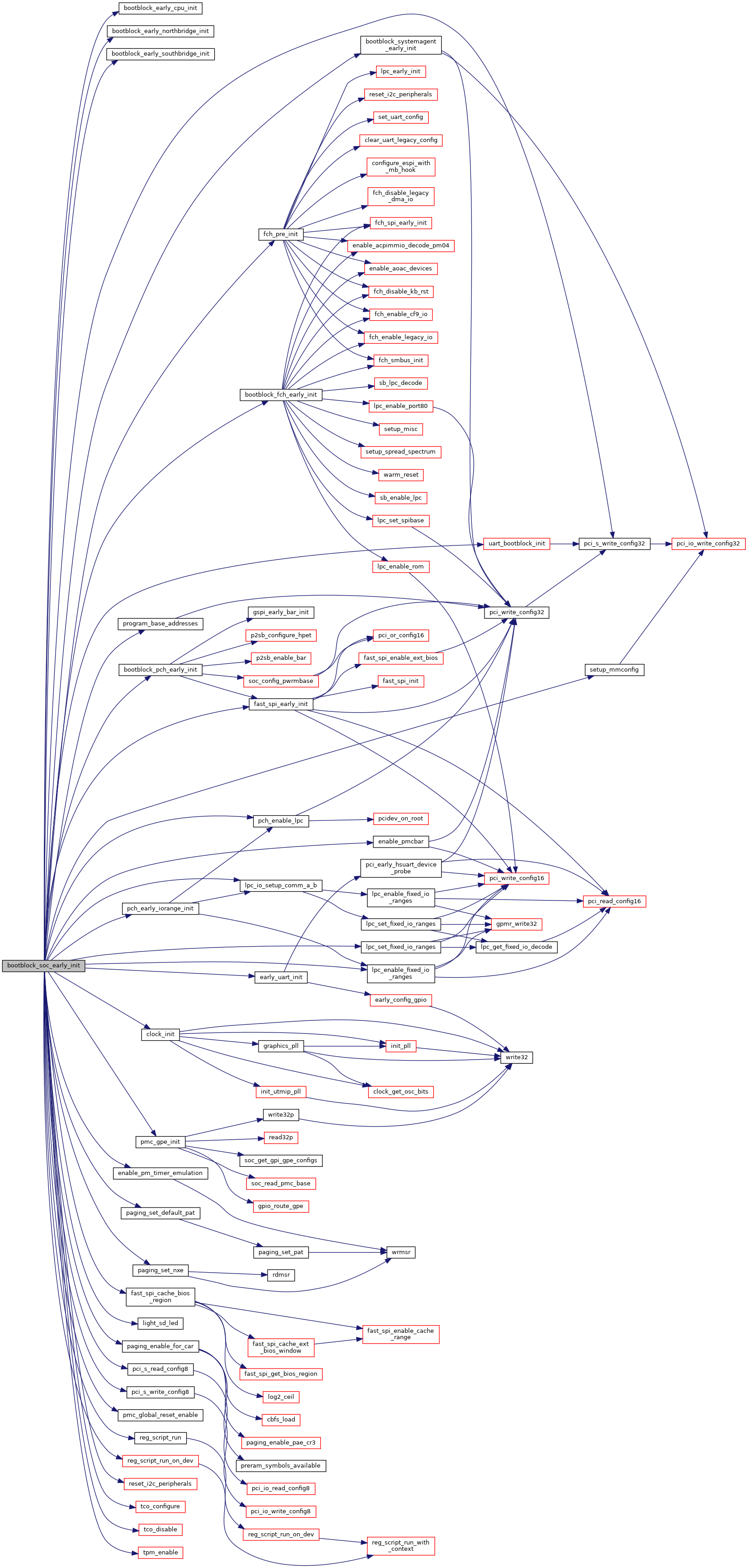

References bootblock_early_cpu_init(), bootblock_early_northbridge_init(), bootblock_early_southbridge_init(), bootblock_fch_early_init(), bootblock_pch_early_init(), bootblock_systemagent_early_init(), clock_init(), config, CONFIG, config_of_soc, DEFAULT_SPI_BASE, early_uart_init(), enable_pm_timer_emulation(), enable_pmcbar(), fast_spi_cache_bios_region(), fast_spi_early_init(), fch_pre_init(), HSUART0_BDF, HSUART1_BDF, hsuart_init, i2c_gpio_controller_init, I2CGPIO_BDF, legacy_gpio_init, light_sd_led(), LPC_BDF, lpc_enable_fixed_io_ranges(), lpc_io_setup_comm_a_b(), LPC_IOE_EC_62_66, LPC_IOE_KBC_60_64, LPC_IOE_SUPERIO_2E_2F, lpc_set_fixed_io_ranges(), mtrr_init, paging_enable_for_car(), paging_set_default_pat(), paging_set_nxe(), PCH_DEV_P2SB, pch_early_iorange_init(), pch_enable_lpc(), PCI_BASE_ADDRESS_0, PCI_COMMAND, PCI_COMMAND_MEMORY, pci_s_read_config8(), pci_s_write_config32(), pci_s_write_config8(), pmc_global_reset_enable(), pmc_gpe_init(), post_code, program_base_addresses(), reg_script_run(), reg_script_run_on_dev(), reset_i2c_peripherals(), setup_mmconfig(), SPI_BASE_ADDRESS, tco_configure(), tco_disable(), tpm_enable(), and uart_bootblock_init().

Referenced by bootblock_main(), and bootblock_main_with_timestamp().

Definition at line 27 of file bootblock.c.

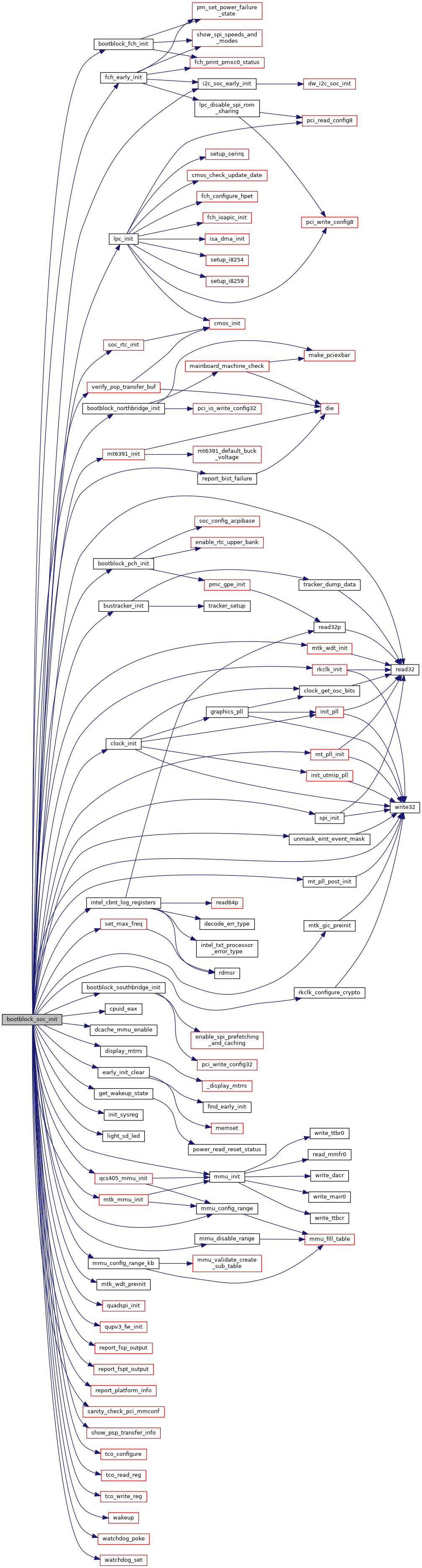

References assembly_timestamp, assert, BIOS_DEBUG, BIOS_INFO, BIOS_WARNING, bootblock_fch_init(), bootblock_northbridge_init(), bootblock_pch_init(), bootblock_southbridge_init(), bootblock_timestamp, bustracker_init(), clock_init(), CONFIG, cpuid_eax(), dcache_mmu_enable(), DCACHE_OFF, DCACHE_WRITEBACK, DCACHE_WRITETHROUGH, rk3399_pmusgrf_regs::ddr_rgn_con, display_mtrrs(), DRAM_SIZE, DRAM_START, early_init_clear(), fch_early_init(), FU540_MSEL, get_wakeup_state(), i2c_soc_early_init(), init_sysreg(), intel_cbnt_log_registers(), KHz, KiB, light_sd_led(), lpc_init(), mmu_config_range(), mmu_config_range_kb(), mmu_disable_range(), mmu_init(), mt6391_init(), mt_pll_init(), mt_pll_post_init(), mtk_gic_preinit(), mtk_mmu_init(), mtk_wdt_init(), mtk_wdt_preinit(), rk3399_pmusgrf_regs::pmu_slv_con0, printk, qcs405_mmu_init(), quadspi_init(), qupv3_fw_init(), read32(), REGION_SIZE, report_bist_failure(), report_fsp_output(), report_fspt_output(), report_platform_info(), rk3399_pmusgrf, rkclk_configure_crypto(), rkclk_init(), sanity_check_pci_mmconf(), saved_bist, set_max_freq(), show_psp_transfer_info(), rk3399_pmusgrf_regs::soc_con4, rk3399_pmusgrf_regs::soc_con7, soc_rtc_init(), spi_init(), SRAM_END, SRAM_SIZE, SRAM_START, TCO1_CNT, tco_configure(), tco_read_reg(), tco_write_reg(), unmask_eint_event_mask(), val, verify_psp_transfer_buf(), wakeup(), WAKEUP_DIRECT, watchdog_poke(), watchdog_set(), and write32().

Referenced by bootblock_main(), and bootblock_main_with_timestamp().