|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

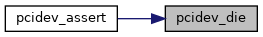

#include <stdint.h>#include <device/device.h>#include <device/pci_type.h>#include <arch/pci_ops.h>

Go to the source code of this file.

Macros | |

| #define | ENV_PCI_SIMPLE_DEVICE 0 |

|

static |

Definition at line 147 of file pci_ops.h.

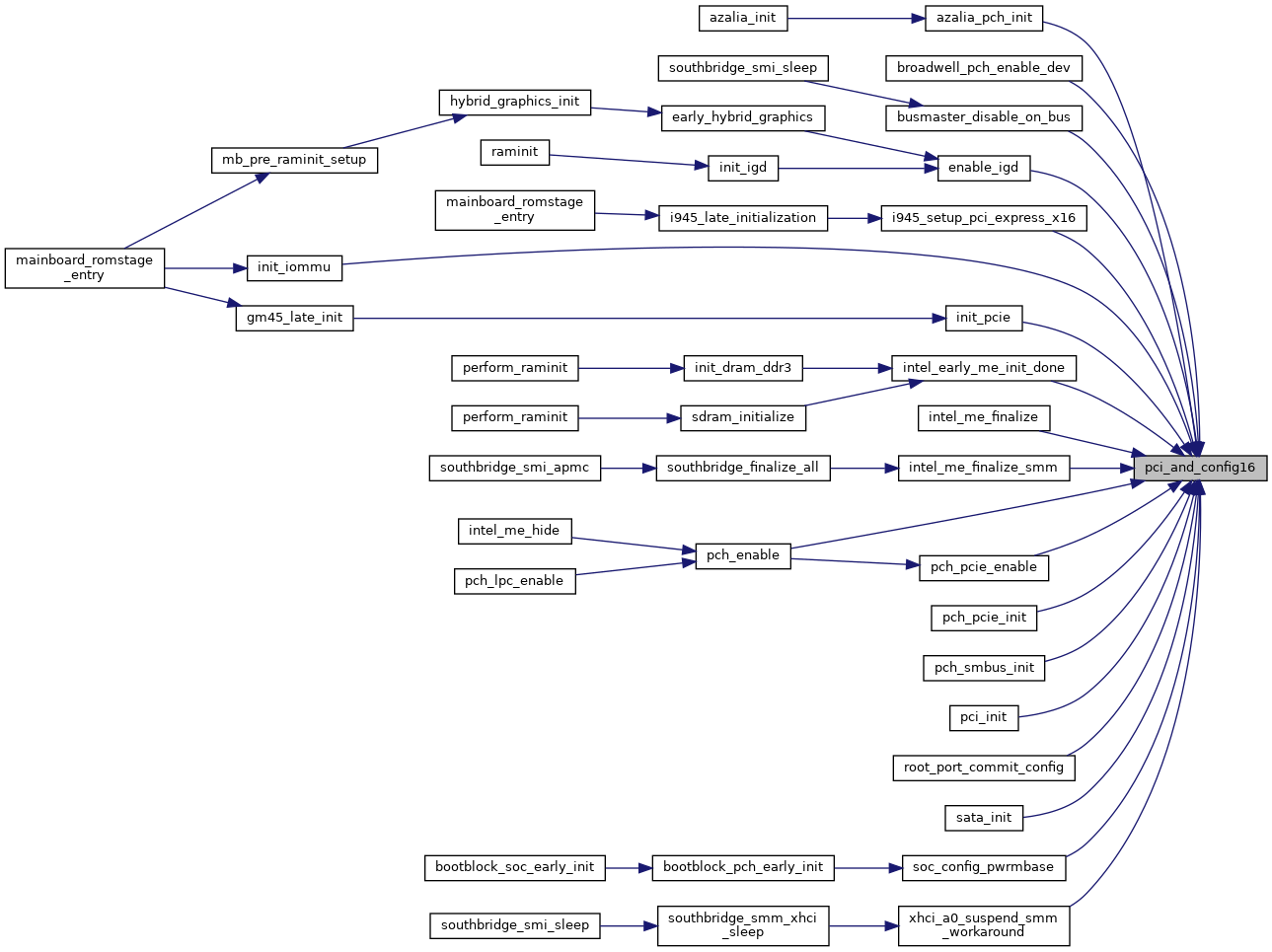

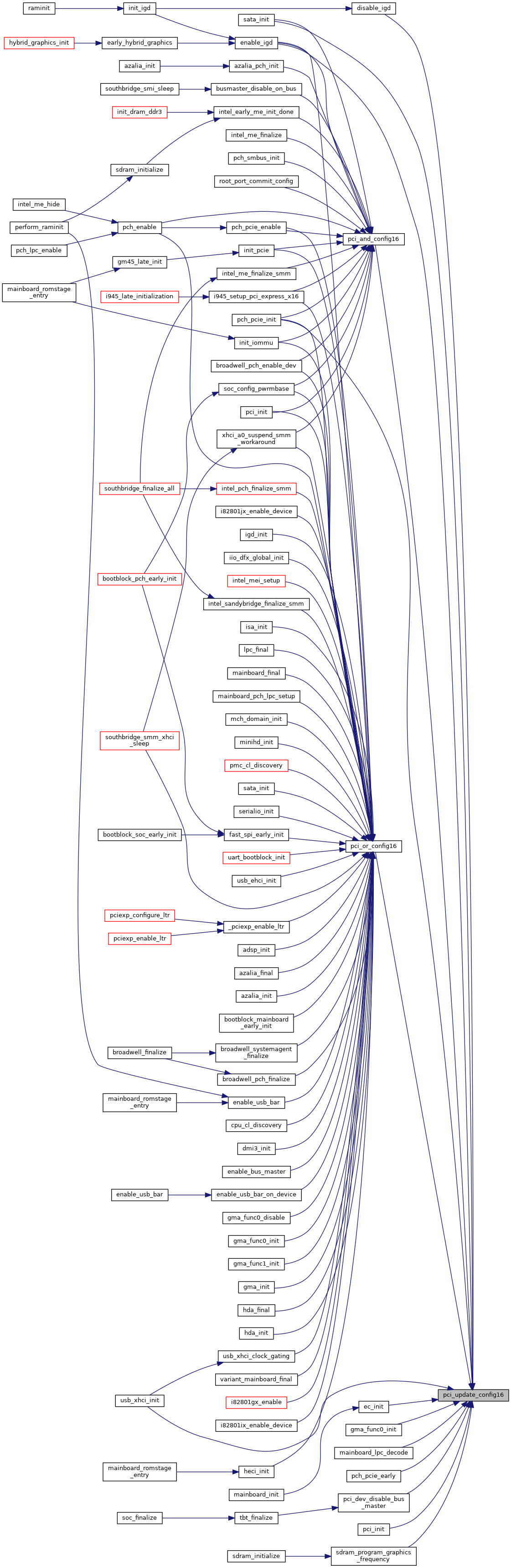

References pci_update_config16().

Referenced by azalia_pch_init(), broadwell_pch_enable_dev(), busmaster_disable_on_bus(), enable_igd(), i945_setup_pci_express_x16(), init_iommu(), init_pcie(), intel_early_me_init_done(), intel_me_finalize(), intel_me_finalize_smm(), pch_enable(), pch_pcie_enable(), pch_pcie_init(), pch_smbus_init(), pci_init(), root_port_commit_config(), sata_init(), soc_config_pwrmbase(), and xhci_a0_suspend_smm_workaround().

|

static |

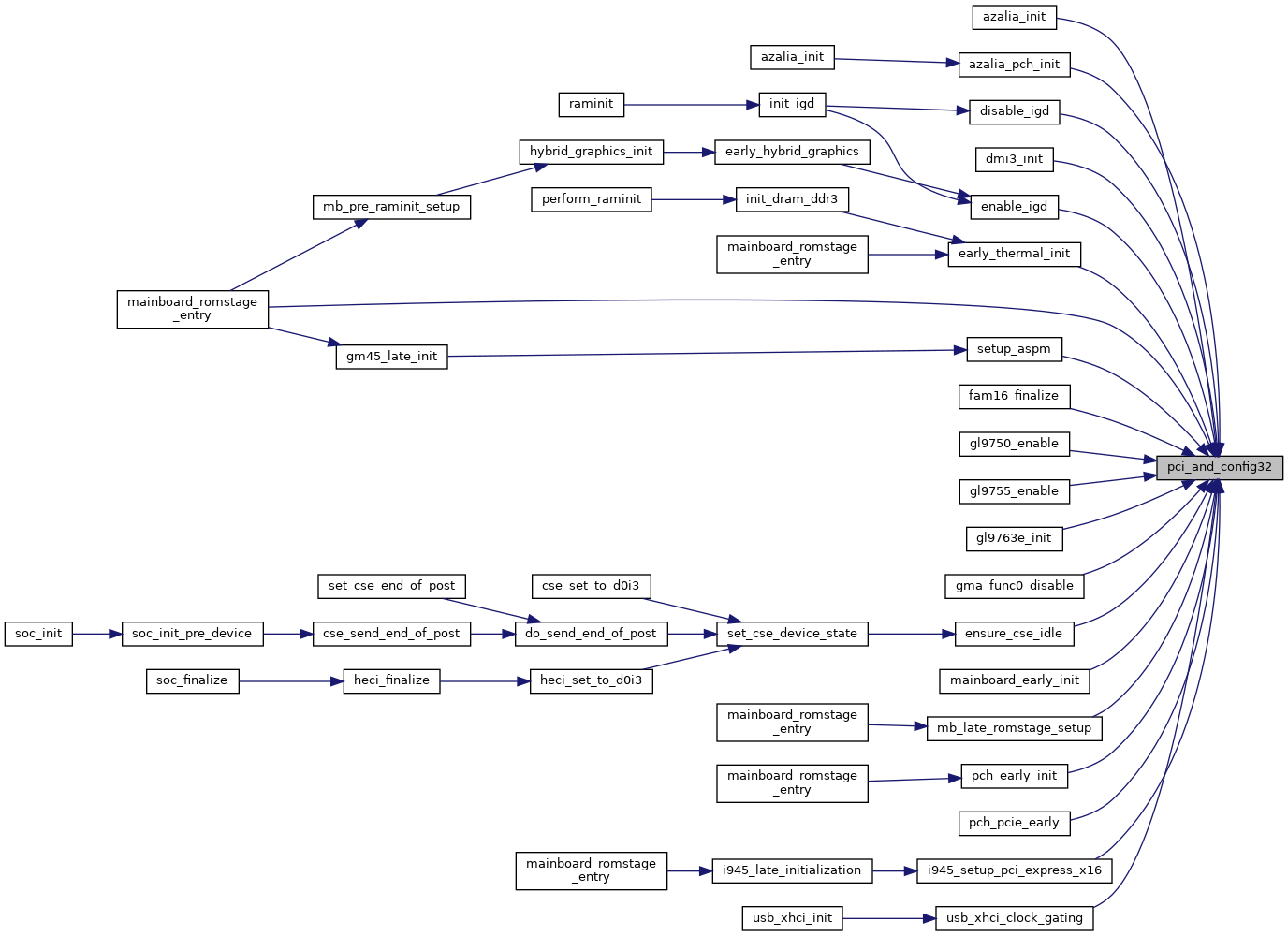

Definition at line 158 of file pci_ops.h.

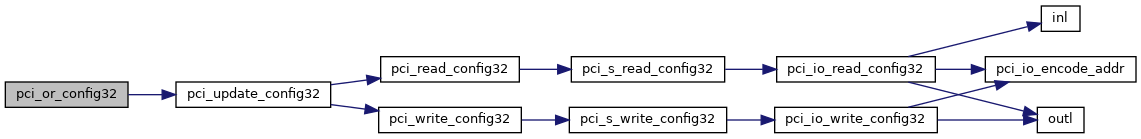

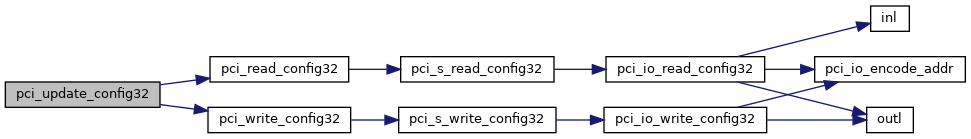

References pci_update_config32().

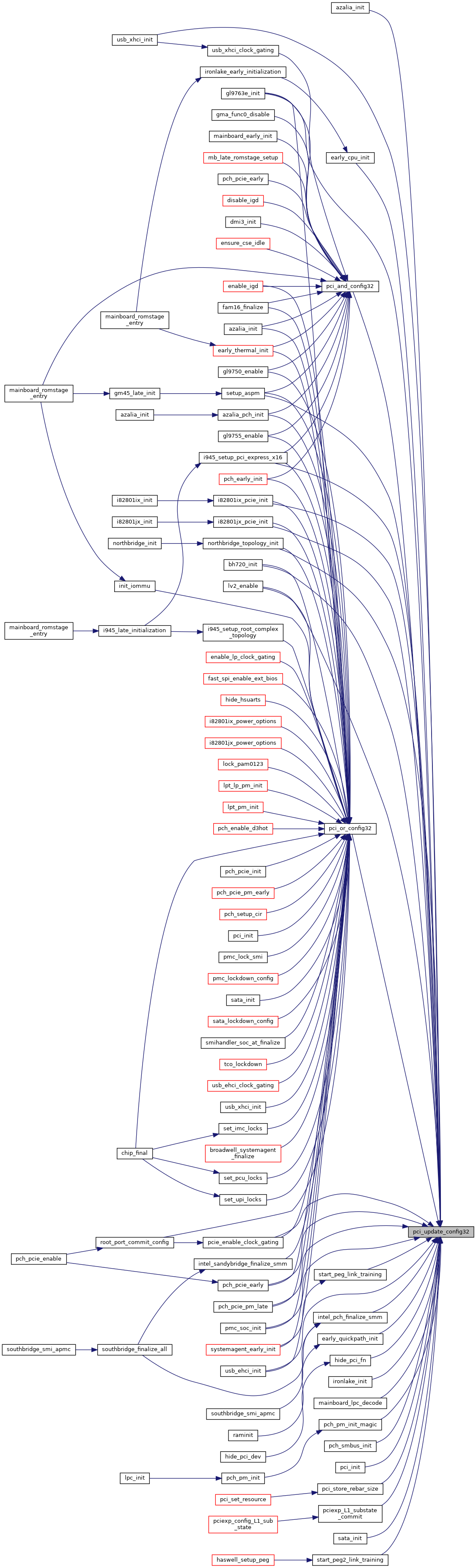

Referenced by azalia_init(), azalia_pch_init(), disable_igd(), dmi3_init(), early_thermal_init(), enable_igd(), ensure_cse_idle(), fam16_finalize(), gl9750_enable(), gl9755_enable(), gl9763e_init(), gma_func0_disable(), i945_setup_pci_express_x16(), mainboard_early_init(), mainboard_romstage_entry(), mb_late_romstage_setup(), pch_early_init(), pch_pcie_early(), setup_aspm(), and usb_xhci_clock_gating().

|

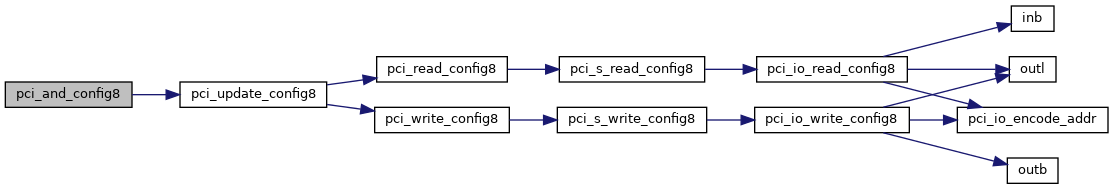

static |

Definition at line 136 of file pci_ops.h.

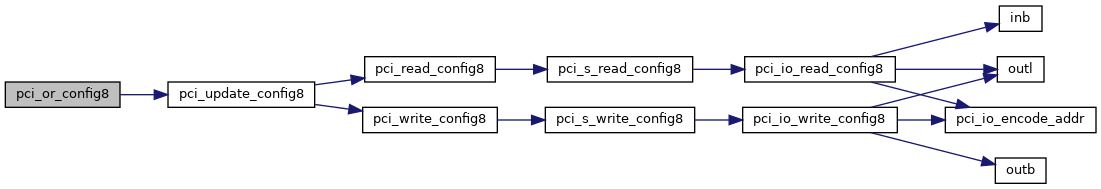

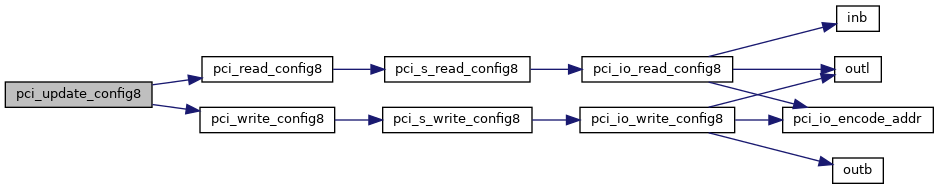

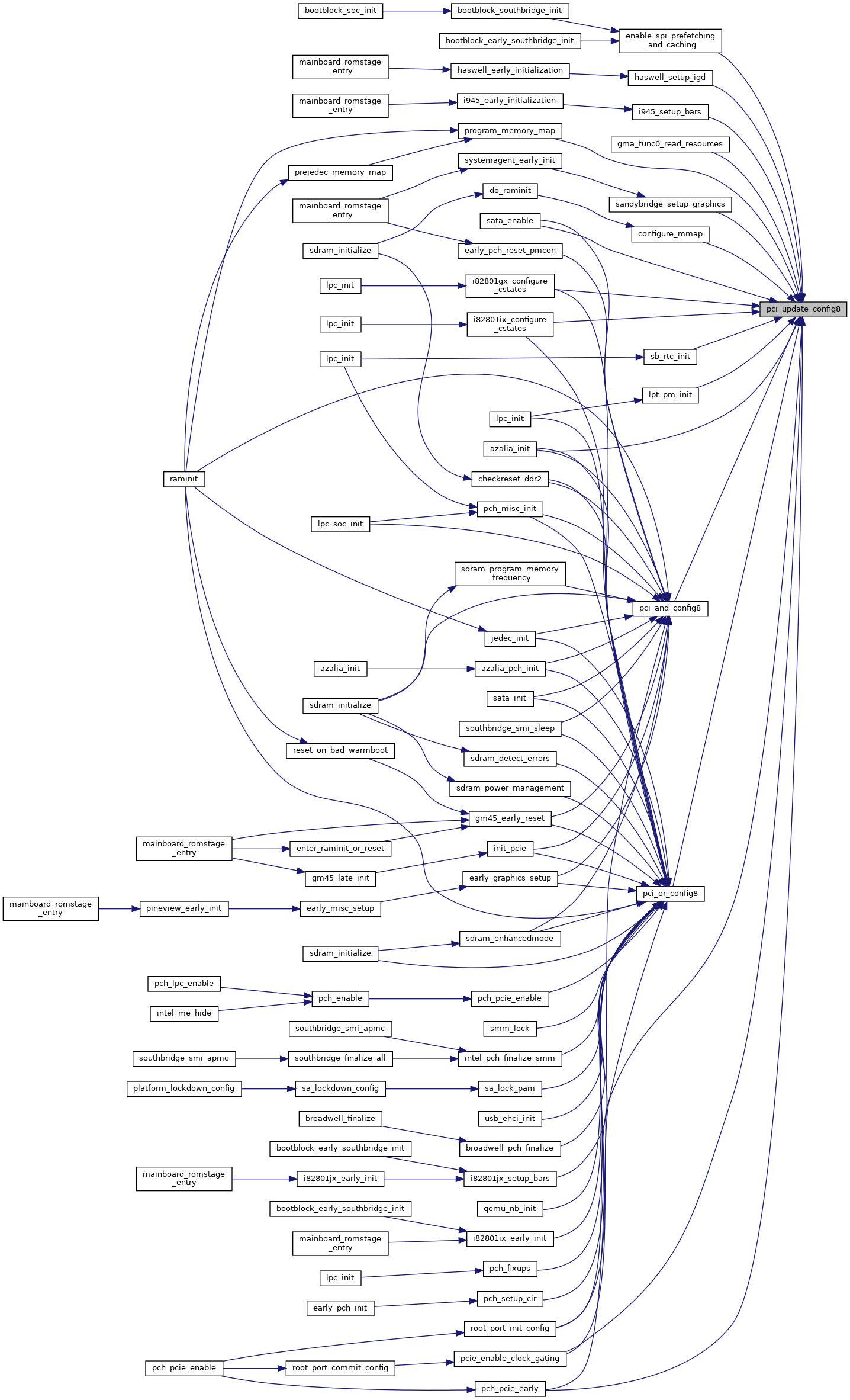

References pci_update_config8().

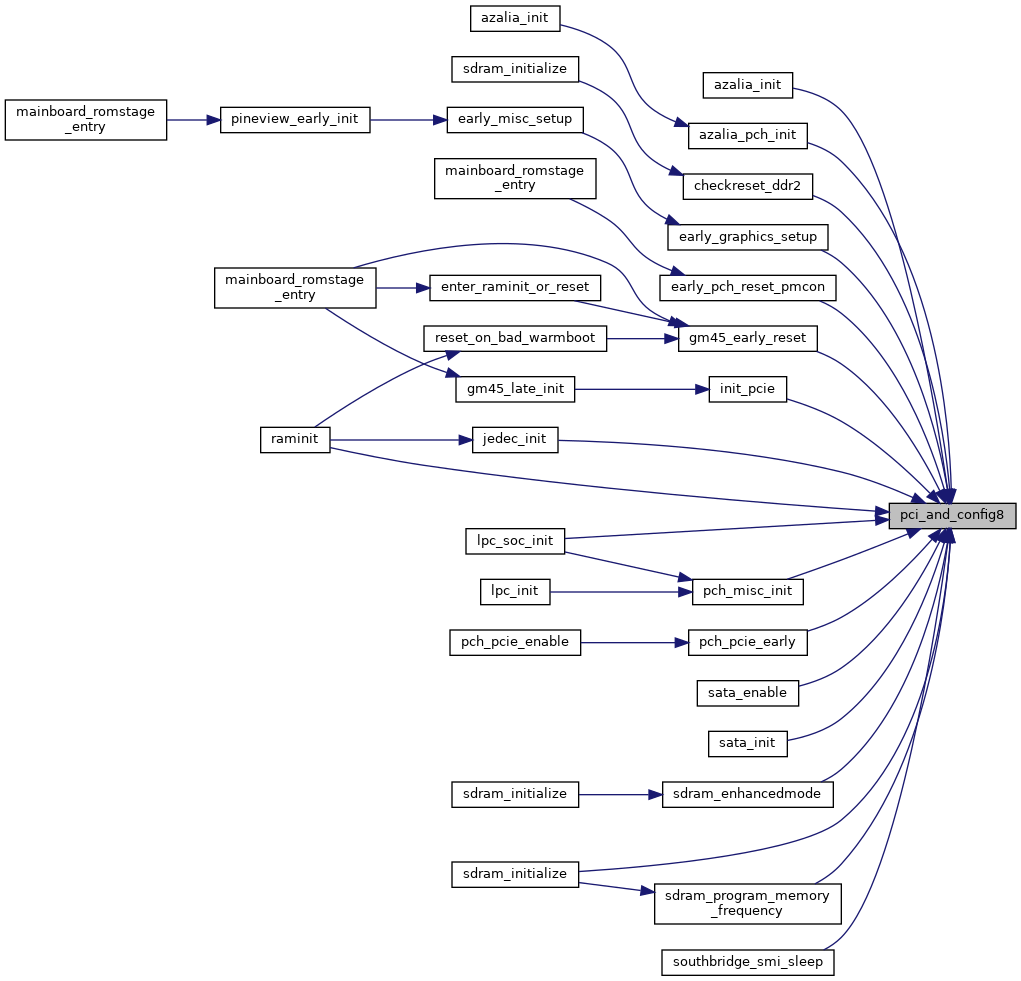

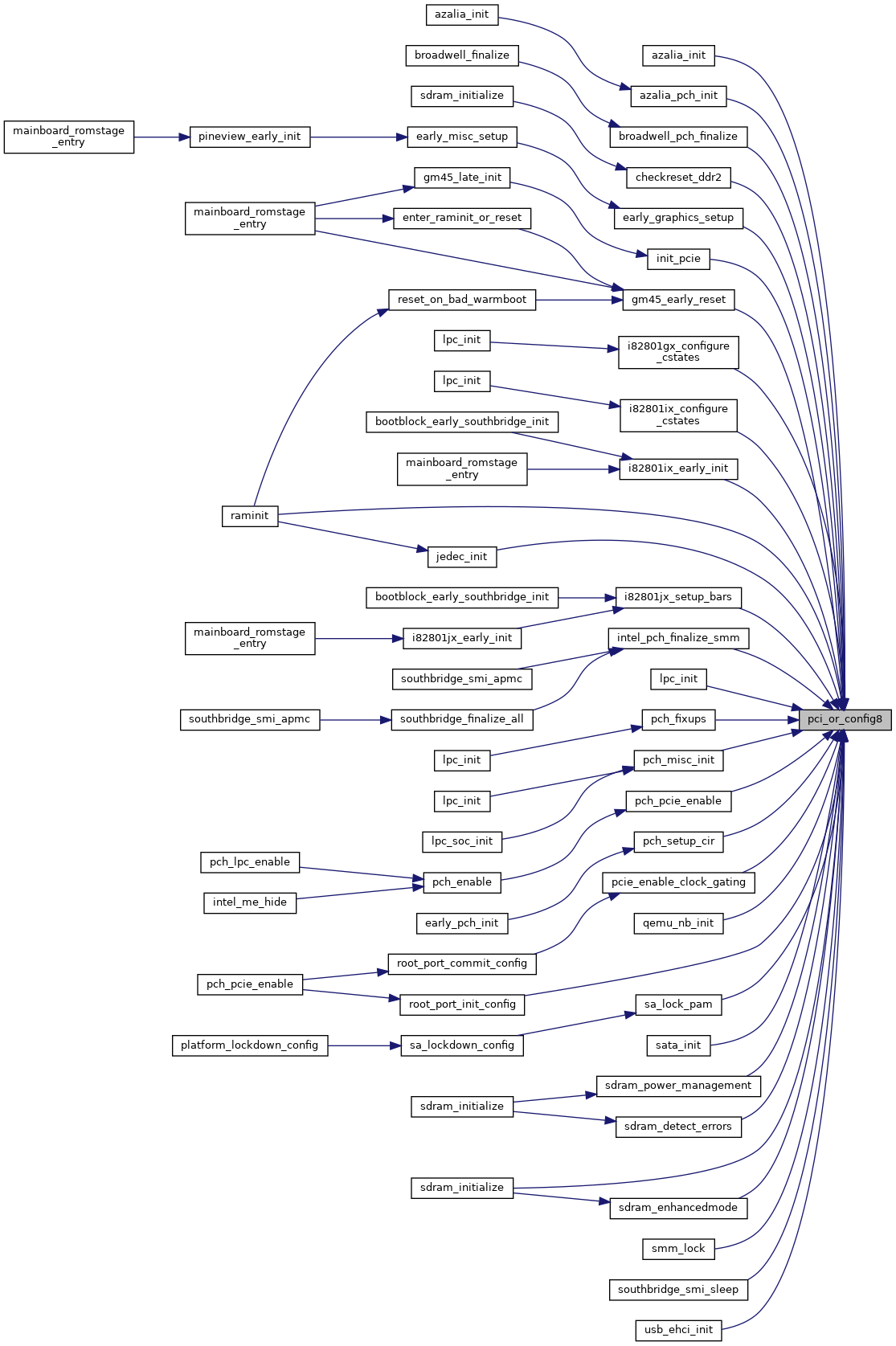

Referenced by azalia_init(), azalia_pch_init(), checkreset_ddr2(), early_graphics_setup(), early_pch_reset_pmcon(), gm45_early_reset(), init_pcie(), jedec_init(), lpc_soc_init(), pch_misc_init(), pch_pcie_early(), raminit(), sata_enable(), sata_init(), sdram_enhancedmode(), sdram_initialize(), sdram_program_memory_frequency(), and southbridge_smi_sleep().

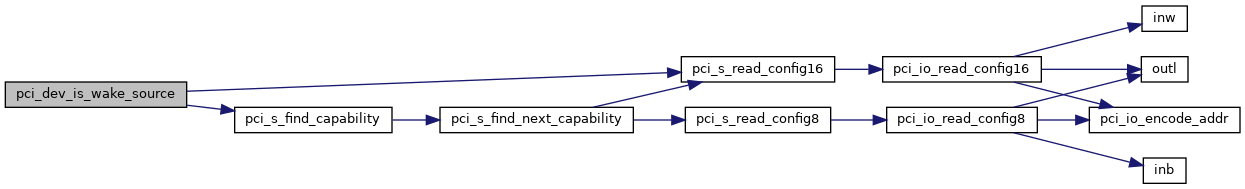

| bool pci_dev_is_wake_source | ( | pci_devfn_t | dev | ) |

Definition at line 82 of file pci_ops.c.

References PCI_CAP_ID_PM, PCI_PM_CTRL, PCI_PM_CTRL_PME_ENABLE, PCI_PM_CTRL_PME_STATUS, pci_s_find_capability(), and pci_s_read_config16().

Referenced by pch_log_pme_internal_wake_source(), and pch_log_rp_wake_source().

|

static |

Definition at line 207 of file pci_ops.h.

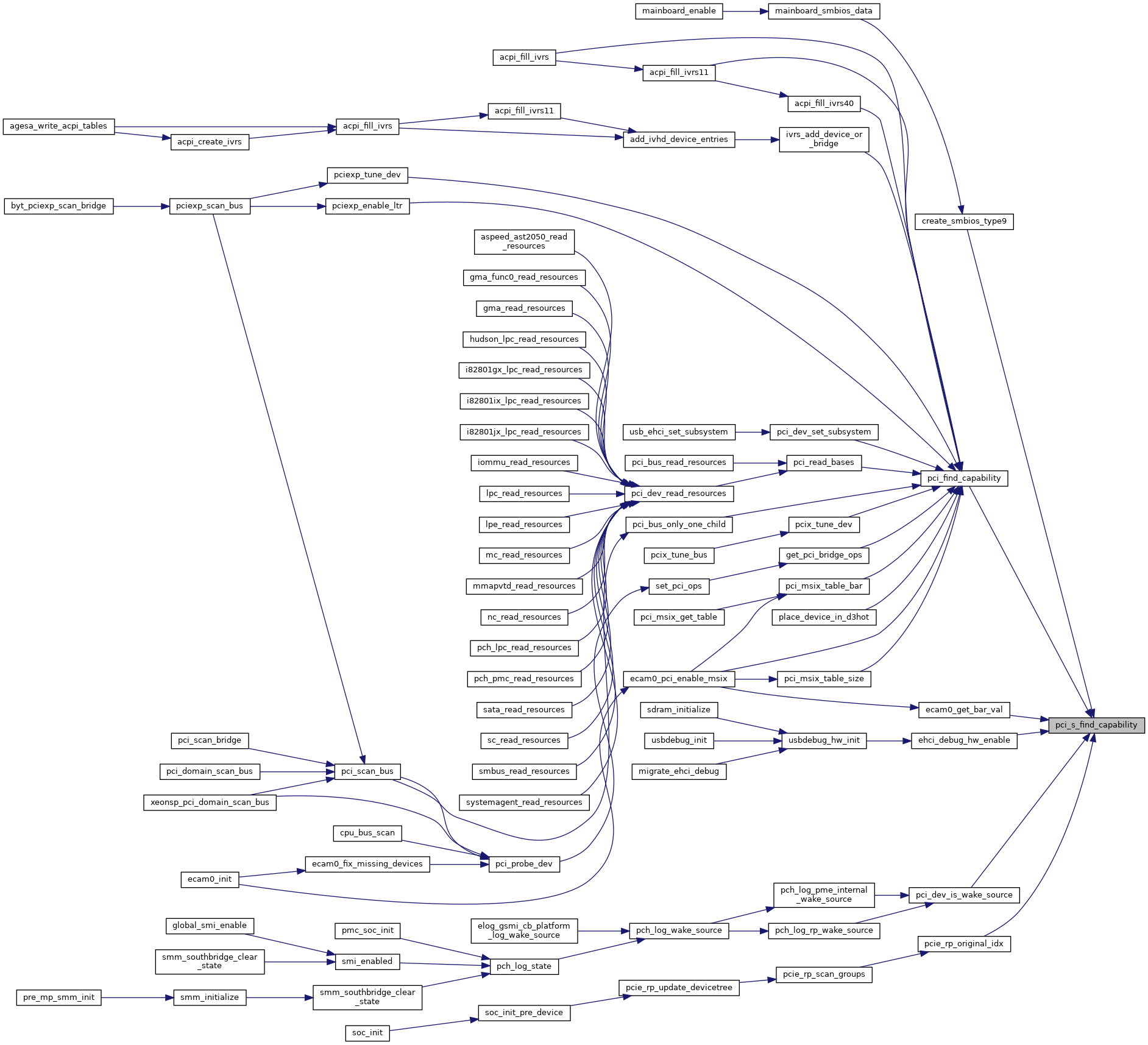

References PCI_BDF, and pci_s_find_capability().

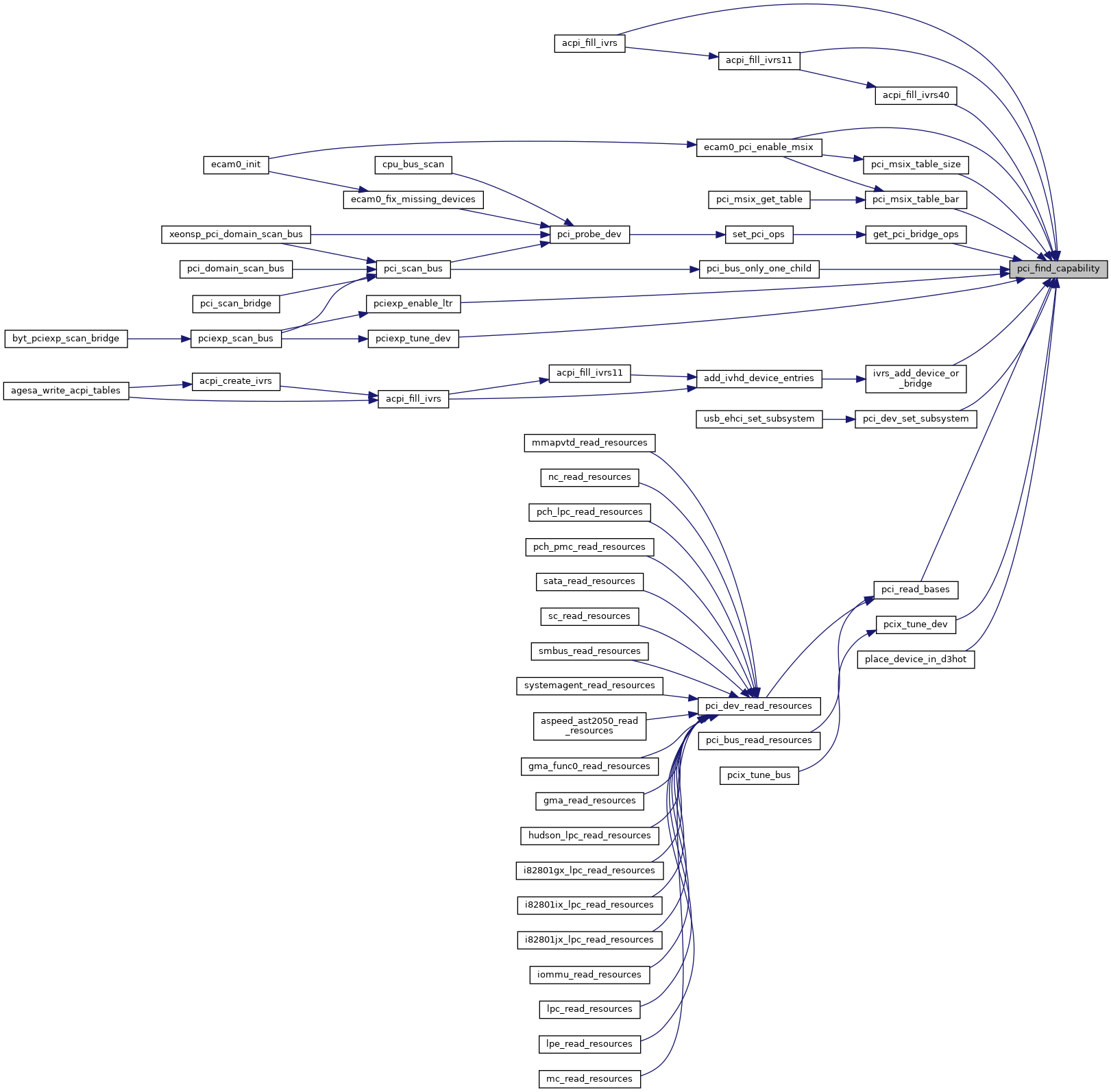

Referenced by acpi_fill_ivrs(), acpi_fill_ivrs11(), acpi_fill_ivrs40(), ecam0_pci_enable_msix(), get_pci_bridge_ops(), ivrs_add_device_or_bridge(), pci_bus_only_one_child(), pci_dev_set_subsystem(), pci_msix_table_bar(), pci_msix_table_size(), pci_read_bases(), pciexp_enable_ltr(), pciexp_tune_dev(), pcix_tune_dev(), and place_device_in_d3hot().

|

static |

Definition at line 201 of file pci_ops.h.

References PCI_BDF, and pci_s_find_next_capability().

|

static |

Definition at line 180 of file pci_ops.h.

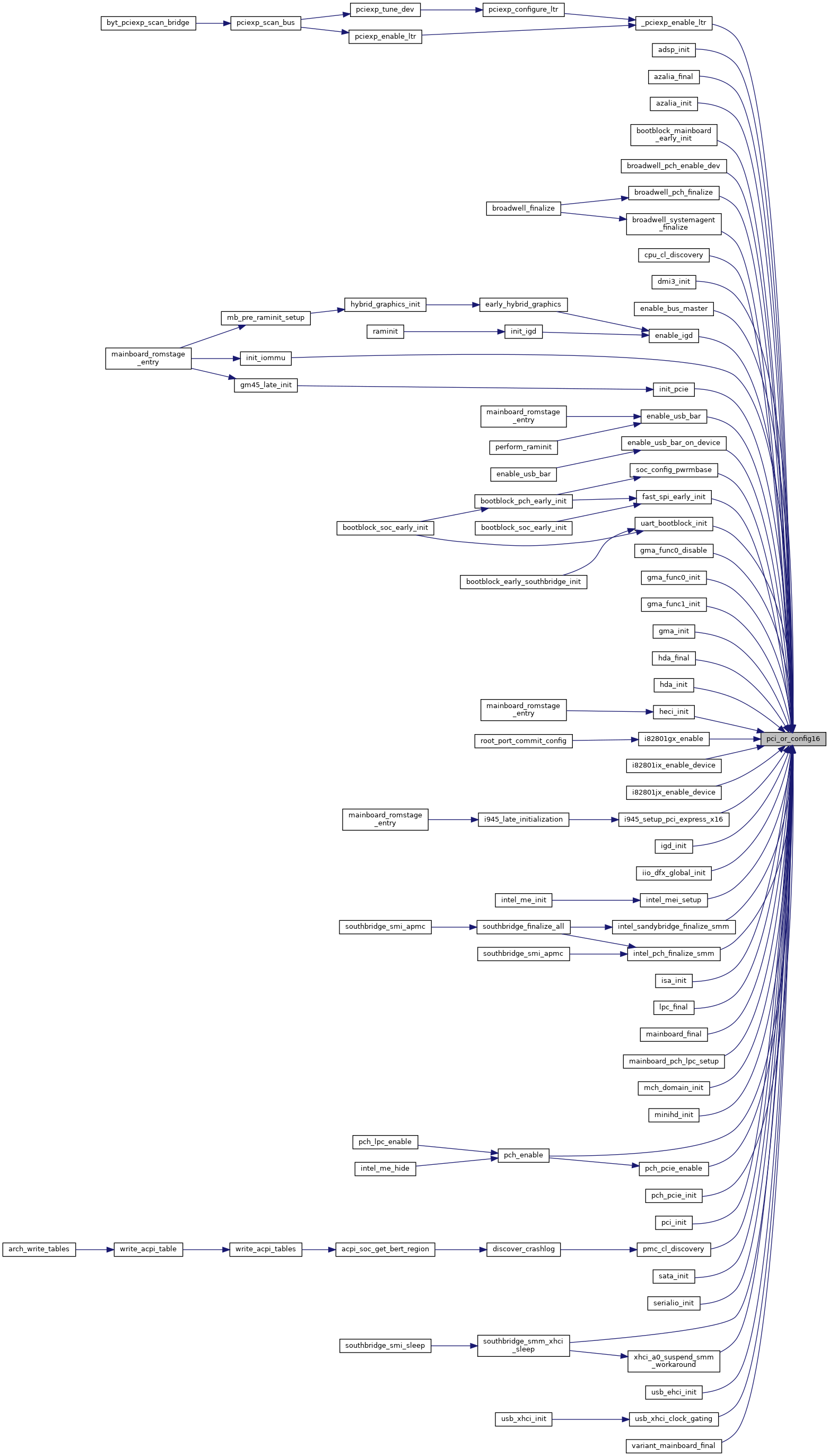

References pci_update_config16().

Referenced by _pciexp_enable_ltr(), adsp_init(), azalia_final(), azalia_init(), bootblock_mainboard_early_init(), broadwell_pch_enable_dev(), broadwell_pch_finalize(), broadwell_systemagent_finalize(), cpu_cl_discovery(), dmi3_init(), enable_bus_master(), enable_igd(), enable_usb_bar(), enable_usb_bar_on_device(), fast_spi_early_init(), gma_func0_disable(), gma_func0_init(), gma_func1_init(), gma_init(), hda_final(), hda_init(), heci_init(), i82801gx_enable(), i82801ix_enable_device(), i82801jx_enable_device(), i945_setup_pci_express_x16(), igd_init(), iio_dfx_global_init(), init_iommu(), init_pcie(), intel_mei_setup(), intel_pch_finalize_smm(), intel_sandybridge_finalize_smm(), isa_init(), lpc_final(), mainboard_final(), mainboard_pch_lpc_setup(), mch_domain_init(), minihd_init(), pch_enable(), pch_pcie_enable(), pch_pcie_init(), pci_init(), pmc_cl_discovery(), sata_init(), serialio_init(), soc_config_pwrmbase(), southbridge_smm_xhci_sleep(), uart_bootblock_init(), usb_ehci_init(), usb_xhci_clock_gating(), variant_mainboard_final(), and xhci_a0_suspend_smm_workaround().

|

static |

Definition at line 191 of file pci_ops.h.

References pci_update_config32().

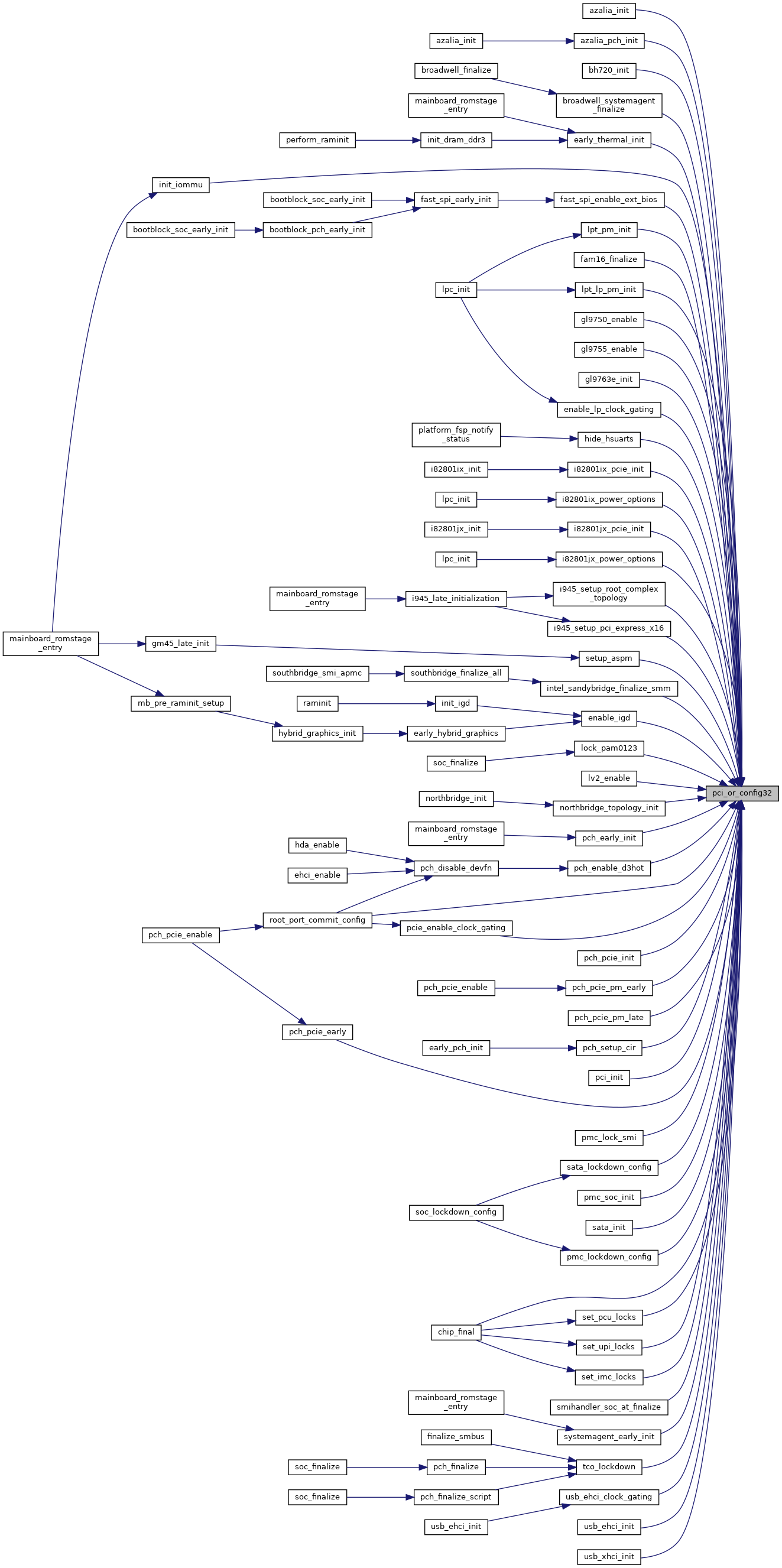

Referenced by azalia_init(), azalia_pch_init(), bh720_init(), broadwell_systemagent_finalize(), chip_final(), early_thermal_init(), enable_igd(), enable_lp_clock_gating(), fam16_finalize(), fast_spi_enable_ext_bios(), gl9750_enable(), gl9755_enable(), gl9763e_init(), hide_hsuarts(), i82801ix_pcie_init(), i82801ix_power_options(), i82801jx_pcie_init(), i82801jx_power_options(), i945_setup_pci_express_x16(), i945_setup_root_complex_topology(), init_iommu(), intel_sandybridge_finalize_smm(), lock_pam0123(), lpt_lp_pm_init(), lpt_pm_init(), lv2_enable(), northbridge_topology_init(), pch_early_init(), pch_enable_d3hot(), pch_pcie_early(), pch_pcie_init(), pch_pcie_pm_early(), pch_pcie_pm_late(), pch_setup_cir(), pci_init(), pcie_enable_clock_gating(), pmc_lock_smi(), pmc_lockdown_config(), pmc_soc_init(), root_port_commit_config(), sata_init(), sata_lockdown_config(), set_imc_locks(), set_pcu_locks(), set_upi_locks(), setup_aspm(), smihandler_soc_at_finalize(), systemagent_early_init(), tco_lockdown(), usb_ehci_clock_gating(), usb_ehci_init(), and usb_xhci_init().

|

static |

Definition at line 169 of file pci_ops.h.

References pci_update_config8().

Referenced by azalia_init(), azalia_pch_init(), broadwell_pch_finalize(), checkreset_ddr2(), early_graphics_setup(), gm45_early_reset(), i82801gx_configure_cstates(), i82801ix_configure_cstates(), i82801ix_early_init(), i82801jx_setup_bars(), init_pcie(), intel_pch_finalize_smm(), jedec_init(), lpc_init(), pch_fixups(), pch_misc_init(), pch_pcie_enable(), pch_setup_cir(), pcie_enable_clock_gating(), qemu_nb_init(), raminit(), root_port_init_config(), sa_lock_pam(), sata_init(), sdram_detect_errors(), sdram_enhancedmode(), sdram_initialize(), sdram_power_management(), smm_lock(), southbridge_smi_sleep(), and usb_ehci_init().

|

static |

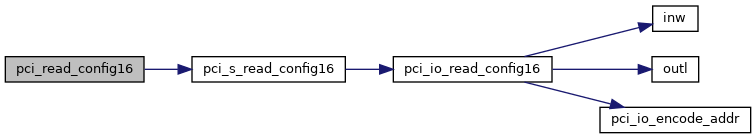

Definition at line 52 of file pci_ops.h.

References PCI_BDF, and pci_s_read_config16().

Referenced by _pciexp_ltr_enabled(), _pciexp_ltr_supported(), ac97_audio_init(), acpi_fill_fadt(), acpi_fill_ivrs(), ahci_raid_init(), aseg_smm_relocate(), bootblock_early_southbridge_init(), bridge_silicon_revision(), busmaster_disable_on_bus(), cardbus_enable_resources(), cardbus_read_resources(), cbmem_top_chipset(), chipset_init(), cl_pmc_sram_has_mmio_access(), collect_system_info(), configure_e7501_cas_latency(), configure_e7501_ram_addresses(), configure_mmap(), cpu_pci_domain_read_resources(), do_ram_command(), dram_memorymap(), early_graphics_setup(), early_pmc_init(), early_tco_init(), ecam0_pci_enable_msix(), enable_clock_gating(), enable_igd(), enable_lp_clock_gating(), enable_pm(), fast_spi_early_init(), fast_spi_wpd_status(), fill_power_state(), fill_vr_domain_config(), find_vbt_location(), get_cdclk(), get_cpu_count(), get_dev_id(), get_gmch_info(), get_gpio_base(), get_gpiobase(), get_ich7_sata_ports(), get_pch_platform_type(), get_pci_bridge_ops(), get_pl2(), get_pmbase(), get_sku_ac_dc_loadline(), get_sku_icc_max(), get_tcobase(), get_vccin_aux_imon_iccmax(), gma_func0_init(), gma_pm_init_post_vbios(), handleInt1a(), haswell_setup_igd(), hda_enable(), heci_init(), hudson_enable(), hudson_lpc_enable_childrens_resources(), i82801dx_enable(), i82801dx_lpc_route_dma(), i82801dx_power_options(), i82801gx_enable(), i82801gx_power_options(), i82801ix_power_options(), i82801jx_power_options(), i945_setup_pci_express_x16(), ich7_setup_cir(), ide_init_enable(), igd_disable(), igd_get_cdclk_broadwell(), igd_get_cdclk_haswell(), iio_dfx_global_init(), init_dram_ddr3(), init_iommu(), int1a_handler(), intel_gma_init_lvds(), intel_gma_init_vga(), intel_me_finalize(), intel_me_finalize_smm(), intel_mei_setup(), is_cse_devfn_visible(), is_sandybridge(), isa_init(), lan_init(), late_quickpath_init(), lpc_enable_fixed_io_ranges(), lpc_find_wideio_range(), lpc_get_fixed_io_decode(), lpc_get_pmbase(), mainboard_init(), mainboard_pch_lpc_setup(), mainboard_romstage_entry(), mainboard_set_power_limits(), mc_read_resources(), mc_report_map_entries(), mch_domain_read_resources(), mchinfo_ddr2(), northbridge_get_tseg_base(), p2sb_dev_is_hidden(), pch_cg_init(), pch_enable(), pch_log_pme_internal_wake_source(), pch_log_state(), pch_pcie_init(), pch_power_options(), pch_setup_cir(), pch_type(), pci7420_cardbus_init(), pci_bridge_route(), pci_bridge_vga_compat(), pci_bus_enable_resources(), pci_bus_only_one_child(), pci_bus_reset(), pci_cfg_read(), pci_dev_enable_resources(), pci_early_hsuart_device_probe(), pci_init(), pci_moving_config16(), pci_msix_table_size(), pci_update_config16(), pciexp_enable_aspm(), pciexp_enable_clock_power_pm(), pciexp_enable_common_clock(), pciexp_retrain_link(), pciexp_set_max_payload_size(), pcix_tune_dev(), pcr_execute_sideband_msg(), pcr_wait_for_completion(), platform_fsp_memory_init_params_cb(), platform_is_up3(), program_total_memory_map(), raminit(), reg_script_read_pci(), report_igd_info(), report_mch_info(), report_pch_info(), sandybridge_setup_graphics(), sata_enable(), sata_init(), sdram_enable(), sdram_initialize(), sdram_mmap_regs(), sdram_set_registers(), select_cas_dramfreq_ddr3(), smbus_enable_iobar(), smm_region(), soc_enable_psp_early(), soc_systemagent_init(), southbridge_gate_memory_reset(), southbridge_smi_handler(), southbridge_smi_tco(), start_peg_link_training(), storage_test_init(), variant_devtree_update(), and watchdog_off().

|

static |

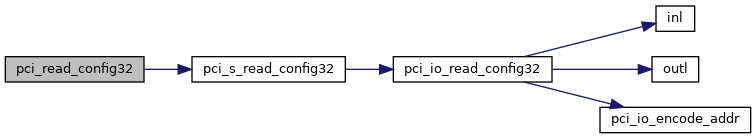

Definition at line 58 of file pci_ops.h.

References PCI_BDF, and pci_s_read_config32().

Referenced by acpi_create_igfx_rmrr(), acpi_fill_dmar(), acpi_fill_fadt(), acpi_fill_ivrs(), acpi_fill_ivrs11(), acpi_fill_ivrs40(), add_fixed_resources(), adsp_init(), aggressive_write_training(), ahci_raid_init(), all_ports_no_dev_present(), attach_iio_stacks(), azalia_init(), azalia_pch_init(), backlight_off(), bh720_init(), bh720_program_hs200_mode(), biosemu_dev_get_device_vendor_id(), board_BeforeAgesa(), bootblock_early_southbridge_init(), busmaster_disable_on_bus(), byt_pcie_enable(), byt_pcie_init(), cf9_reset_prepare(), check_device_present(), cirrus_init_linear_fb(), cl_get_cpu_bar_addr(), clear_bios_reset(), collect_system_info(), com1_configure_resume(), configure_child_lpc_windows(), configure_dpr(), configure_e7501_cas_latency(), configure_e7501_dram_controller_mode(), configure_e7501_dram_timing(), continue_spi_dma_transaction(), cpu_bus_scan(), cpu_cl_get_capability(), create_vga_resource(), d060_control(), data_fabric_broadcast_read32(), data_fabric_read32(), disable_devices(), disable_peg(), do_ram_command(), dpr_region_start(), dram_memorymap(), dump_pci_devices(), dw_i2c_base_address(), e7505_mch_is_ready(), early_lpc_init(), early_pmc_init(), early_quickpath_init(), early_thermal_init(), ecam0_get_bar_val(), ecam0_init(), eeprom_read_buffer(), eeprom_write_byte(), enable_hpet(), enable_igd(), enable_serial(), enable_wideio(), espi_disable_lpc_ldrq(), exit_soft_temp_disable_wait(), f1_read_config32(), fam15_finalize(), fam16_finalize(), fast_spi_clear_sync_smi_status(), fast_spi_get_bar(), fast_spi_set_bios_control_reg(), find_cas_tck(), find_unused_pmio_window(), generate_cpu_entries(), get_bar(), get_cse_bar(), get_dram_base_limit(), get_gmch_info(), get_gpe0_address(), get_gpio_address(), get_host_ecc_cap(), get_host_ecc_forced(), get_i2c_address(), get_legacy_gpio_address(), get_mem_min_tck(), get_node_nums(), get_num_ports(), get_pcie_bar(), get_pciebase(), get_pcielength(), get_pmbase(), get_rebar_offset(), get_rebar_sizes_mask(), get_spi_bar(), get_top_of_low_memory(), get_top_of_upper_memory(), get_touud(), get_tseg_memory(), gfx_init(), gl9755_enable(), gl9763e_init(), gm45_init(), gma_func0_init(), gma_ngi(), gpi_route_interrupt(), gpp_dxio_update_clk_req_config(), gspi_get_base_addr(), gtt_setup(), handleInt1a(), haswell_setup_igd(), haswell_setup_iommu(), haswell_setup_peg(), haswell_unhide_peg(), hda_pch_init(), heci_fw_sts(), hudson_lpc_enable_childrens_resources(), hudson_lpc_set_resources(), hudson_spibase(), hudson_tpm_decode_spi(), hybrid_graphics_init(), i82801dx_enable_ioapic(), i82801dx_rtc_init(), i82801gx_lpc_read_resources(), i82801ix_ehci_init(), i82801ix_pcie_init(), i82801jx_ehci_init(), i82801jx_lpc_read_resources(), i82801jx_pcie_init(), i945_early_initialization(), i945_setup_bars(), i945_setup_pci_express_x16(), igd_compute_ggc(), init(), init_dram_ddr3(), init_fan_control(), init_iommu(), int1a_handler(), intel_early_me_init(), intel_early_me_init_done(), intel_early_me_status(), intel_early_me_uma_size(), intel_me_extend_valid(), intel_me_finalize(), intel_me_finalize_smm(), intel_me_hsio_version(), intel_me_mbp_clear(), intel_me_path(), intel_me_read_mbp(), intel_pch_finalize_smm(), ironlake_early_initialization(), is_cnvi_held_in_reset(), is_warm_reset(), isa_init(), lpc_disable_decodes(), lpc_enable_childrens_resources(), lpc_enable_port80(), lpc_enable_sio_decode(), lpc_enable_spi_prefetch(), lpc_enable_spi_rom(), lpc_get_spibase(), lpc_init(), lpc_open_mmio_window(), lpc_open_pmio_window(), lpc_set_resources(), lpc_set_spibase(), lpc_set_wideio_range(), lpc_spibase(), lpc_tpm_decode(), lpc_tpm_decode_spi(), lpc_wideio_size(), lpc_wideio_window(), mainboard_early_init(), mainboard_final(), mainboard_machine_check(), mainboard_smi_brightness_down(), mainboard_smi_brightness_up(), mainboard_smi_sleep(), mc_add_dram_resources(), mc_read_resources(), mch_domain_read_resources(), mchinfo_ddr2(), mchtest_control(), mdr_read(), me_read_config32(), me_read_dword_ptr(), nc_fpga_init(), northbridge_get_tseg_base(), northbridge_get_tseg_limit(), northbridge_write_acpi_tables(), p2sb_configure_endpoints(), pch_lpc_add_io_resources(), pch_lpc_add_mmio_resources(), pch_pcie_init(), pch_pcie_pm_early(), pch_pcie_pm_late(), pci7420_cardbus_init(), pci_cfg_read(), pci_dev_set_subsystem(), pci_ehci_dbg_dev(), pci_ehci_dbg_set_port(), pci_get_resource(), pci_get_rom_resource(), pci_init(), pci_locate_device(), pci_moving_config32(), pci_msix_table_bar(), pci_probe_dev(), pci_read_config_dword(), pci_read_dword_ptr(), pci_rom_probe(), pci_update_config32(), pcie_iosf_port_grant_count(), pcie_update_device_tree(), pciexp_aspm_latency(), pciexp_enable_aspm(), pciexp_enable_clock_power_pm(), pciexp_find_next_extended_cap(), pciexp_get_ext_cap_offset(), pciexp_L1_substate_cal(), pciexp_L1_substate_commit(), pciexp_set_max_payload_size(), pcix_tune_dev(), pcr_execute_sideband_msg(), platform_BeforeInitReset(), pmc_mmio_regs(), pmc_set_disb(), pmc_soc_init(), print_dram_info(), print_pci_devices(), program_memory_map(), program_total_memory_map(), protect_a_range(), quickpath_configure_pll_ratio(), raminit(), read_flash(), read_map_entry(), read_register(), reg_script_read_pci(), rl5c476_init(), root_port_commit_config(), root_port_init_config(), sa_get_gsm_base(), sa_get_tolud_base(), sa_get_tseg_base(), sa_read_map_entry(), sa_set_pci_bar(), sa_soc_systemagent_init(), sa_write_acpi_tables(), sata_enable(), sata_init(), sata_program_indexed(), sc_enable_serial_irqs(), sc_set_serial_irqs_mode(), sdram_capabilities_dual_channel(), sdram_capabilities_interleave(), sdram_capabilities_max_supported_memory_frequency(), sdram_enable(), sdram_mmap_regs(), sdram_post_ecc(), sdram_set_registers(), set_global_reset(), set_ram_mode(), set_sb_gnvs(), set_warm_reset_flag(), setup_aspm(), setup_heci_uma(), setup_sdram_meminfo(), sir_read(), sir_unset_and_set_mask(), smbios_mainboard_serial_number(), smbus_i2c_block_write(), smm_region(), smn_read32(), soc_add_fixed_mmio_resources(), soc_config_acpibase(), soc_config_pwrmbase(), soc_enable_sata_features(), soc_fill_power_state(), soc_get_mbox_address(), soc_read_sci_irq_select(), soc_vtd_enabled(), southbridge_smm_xhci_sleep(), spi_dma_has_error(), spi_dma_is_busy(), spi_init(), start_peg_link_training(), start_spi_dma_transaction(), storage_test_init(), sysconf_init(), system_agent_region_base(), systemagent_early_init(), systemagent_read_resources(), systemagent_vtd_init(), systemagent_write_acpi_tables(), tco_enable_bar(), tsc_freq_mhz(), usb_xhci_clock_gating(), usb_xhci_init(), usb_xhci_mem_base(), usb_xhci_reset_usb3(), workaround_stacked_mode(), write_flash(), x4x_early_init(), xhci_a0_suspend_smm_workaround(), xhci_enable(), xhci_mem_base(), and xhci_route_all().

|

static |

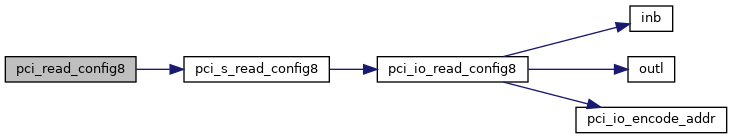

Definition at line 46 of file pci_ops.h.

References PCI_BDF, and pci_s_read_config8().

Referenced by acpi_fill_dmar(), ahci_raid_init(), all_ports_no_dev_present(), azalia_pch_init(), baytrail_run_reference_code(), bootblock_mainboard_early_init(), busmaster_disable_on_bus(), cbmem_top_chipset(), checkreset_ddr2(), chipset_init(), collect_system_info(), configure_dmi_pm(), disable_igd(), dnv_get_int_line(), do_ram_command(), do_raminit(), dump_pci_device(), early_lpc_init(), early_pch_init_native(), ecam0_get_bar_val(), enable_e7501_clocks(), enable_lp_clock_gating(), enable_pm(), enter_raminit_or_reset(), fast_spi_disable_wp(), fast_spi_enable_wp(), fast_spi_init(), fast_spi_read_post_write(), fill_in_pattrs(), generate_fake_intel_oprom(), get_dev_revision(), get_gmch_info(), get_mem_min_tck(), get_pci_class_entry(), get_pci_irq_pins(), get_pci_subclass_name(), get_pcie_rp_pmc_idx(), gfx_init(), gm45_late_init(), gma_func0_init(), gtt_setup(), handleInt1a(), hda_enable(), hda_pch_init(), hudson_lpc_enable_childrens_resources(), hudson_lpc_port80(), hudson_pci_port80(), i440bx_domain_read_resources(), i82801dx_power_options(), i82801dx_rtc_init(), i82801gx_pirq_init(), i82801gx_power_options(), i82801gx_rtc_init(), i82801ix_early_init(), i82801ix_pirq_init(), i82801ix_power_options(), i82801ix_rtc_init(), i82801jx_early_init(), i82801jx_pirq_init(), i82801jx_power_options(), i82801jx_rtc_init(), i945_detect_chipset(), i945_setup_dmi_rcrb(), i945_setup_egress_port(), i945_setup_root_complex_topology(), i945_silicon_revision(), i945m_detect_chipset(), ich7_setup_cir(), ide_init_udma33(), igd_disable(), imc_reg_init(), init_igd(), init_iommu(), init_pcie(), int1a_handler(), intel_acpi_gen_def_acpi_pirq(), ironlake_early_initialization(), late_quickpath_init(), lpc_configure_write_protect(), lpc_disable_clkrun(), lpc_disable_spi_rom_sharing(), lpc_enable_rom(), lpc_init(), lpc_set_bios_control_reg(), lpc_set_serirq_mode(), lpc_set_wideio_range(), lpc_wideio_size(), mainboard_init(), mainboard_romstage_entry(), mainboard_smi_apmc(), mainboard_smi_brightness_down(), mainboard_smi_brightness_up(), mainboard_smi_save_cmos(), mch_domain_read_resources(), nc_fpga_init(), northbridge_get_tseg_base(), northbridge_get_tseg_size(), p2sb_dev_set_hide_bit(), p2sb_lock_endpoints(), pch_cg_init(), pch_log_state(), pch_misc_init(), pch_pcie_early(), pch_pcie_pm_early(), pch_pirq_init(), pch_revision(), pch_rtc_init(), pch_silicon_revision(), pch_silicon_type(), pci7420_cardbus_init(), pci_cfg_read(), pci_dev_set_resources(), pci_moving_config8(), pci_probe_dev(), pci_read_config_byte(), pci_rom_probe(), pci_update_config8(), pmc_soc_set_afterg3_en(), power_settings(), program_memory_map(), punit_init(), pwrmgt_enable(), qemu_nb_init(), RAM_RESET_DDR_PTR(), ram_set_rcomp_regs(), raminit(), reg_script_read_pci(), report_cpu_info(), report_igd_info(), report_mch_info(), report_pch_info(), rtc_failure(), sata_enable(), sata_init(), sdram_capabilities_core_frequencies(), sdram_capabilities_enhanced_addressing_xor(), sdram_checkreset(), sdram_detect_errors(), sdram_detect_ram_speed(), sdram_initialize(), sdram_mmap_regs(), sdram_power_management(), sdram_program_graphics_frequency(), sdram_program_row_boundaries(), sdram_set_registers(), set_d3hot_bits(), set_dram_buffer_strength(), set_dram_row_attributes(), set_enhanced_mode(), silicon_stepping(), smbus_enable_iobar(), smm_region(), soc_lockdown(), SocStepping(), southbridge_smi_sleep(), southbridge_smi_tco(), spd_enable_refresh(), swizzle_irq_pins(), systemagent_early_init(), systemagent_revision(), ti_pci1x2y_init(), usb_ehci_init(), usb_ehci_set_subsystem(), write_pci_cfg_irqs(), and write_pci_config_irqs().

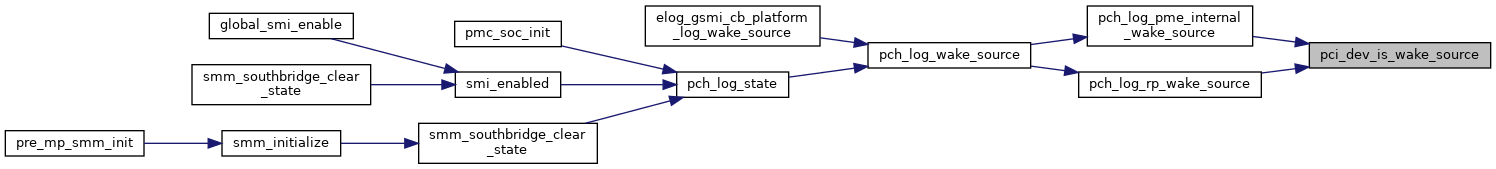

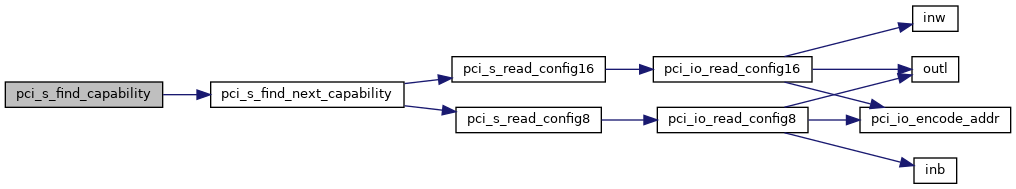

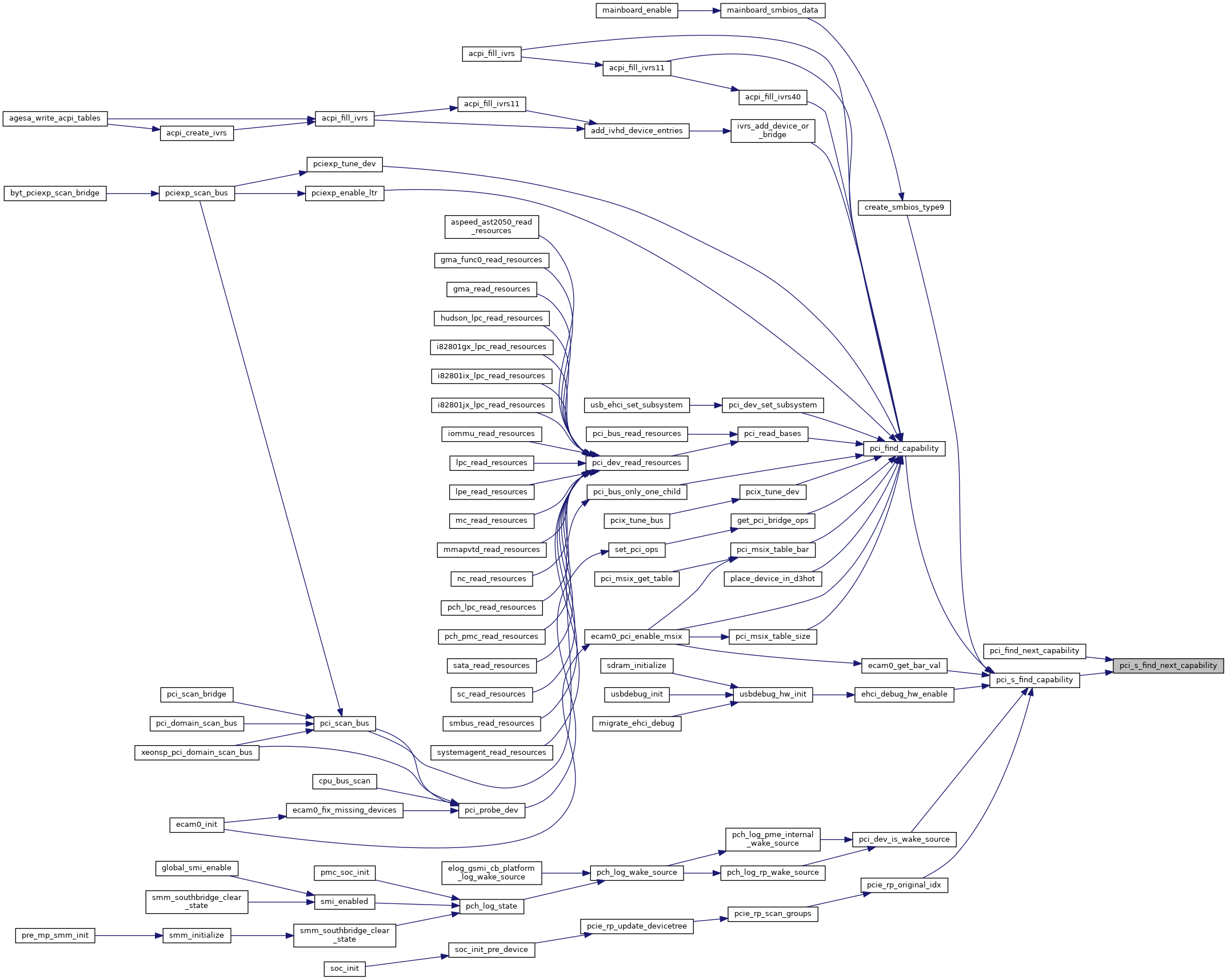

| u16 pci_s_find_capability | ( | pci_devfn_t | dev, |

| u16 | cap | ||

| ) |

Given a device, and a capability type, return the next matching capability.

Always start at the head of the list.

| dev | Pointer to the device structure. |

| cap | PCI_CAP_LIST_ID of the PCI capability we're looking for. |

Definition at line 72 of file pci_ops.c.

References pci_s_find_next_capability().

Referenced by create_smbios_type9(), ecam0_get_bar_val(), ehci_debug_hw_enable(), pci_dev_is_wake_source(), pci_find_capability(), and pcie_rp_original_idx().

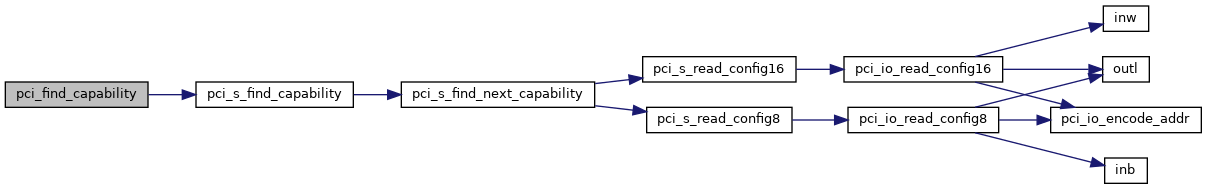

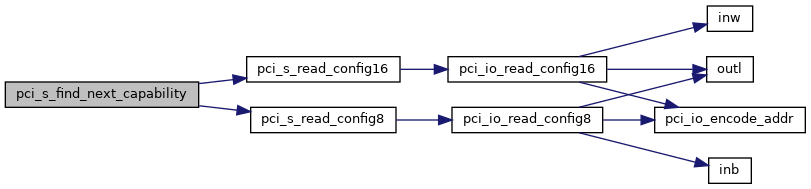

| u16 pci_s_find_next_capability | ( | pci_devfn_t | dev, |

| u16 | cap, | ||

| u16 | last | ||

| ) |

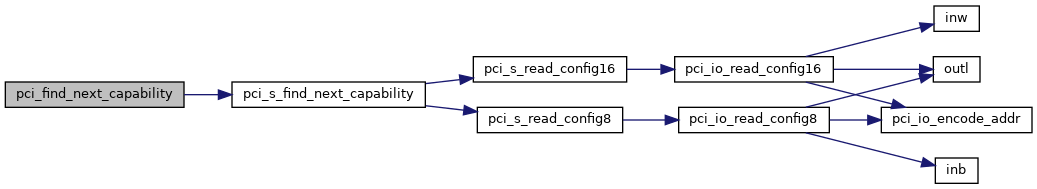

Given a device, a capability type, and a last position, return the next matching capability.

Always start at the head of the list.

| dev | Pointer to the device structure. |

| cap | PCI_CAP_LIST_ID of the PCI capability we're looking for. |

| last | Location of the PCI capability register to start from. |

Definition at line 21 of file pci_ops.c.

References PCI_CAP_LIST_ID, PCI_CAP_LIST_NEXT, PCI_CAPABILITY_LIST, PCI_CB_CAPABILITY_LIST, PCI_HEADER_TYPE, PCI_HEADER_TYPE_BRIDGE, PCI_HEADER_TYPE_CARDBUS, PCI_HEADER_TYPE_NORMAL, pci_s_read_config16(), pci_s_read_config8(), PCI_STATUS, and PCI_STATUS_CAP_LIST.

Referenced by pci_find_next_capability(), and pci_s_find_capability().

|

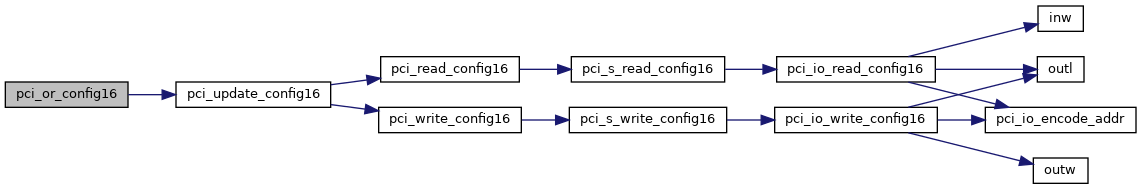

static |

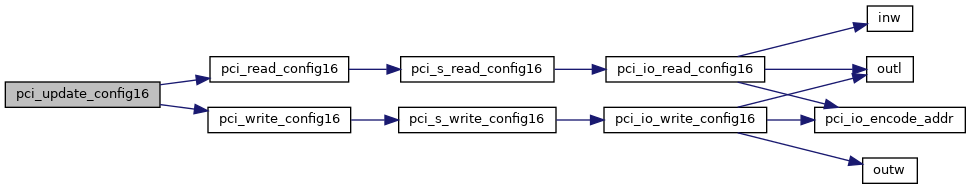

Definition at line 104 of file pci_ops.h.

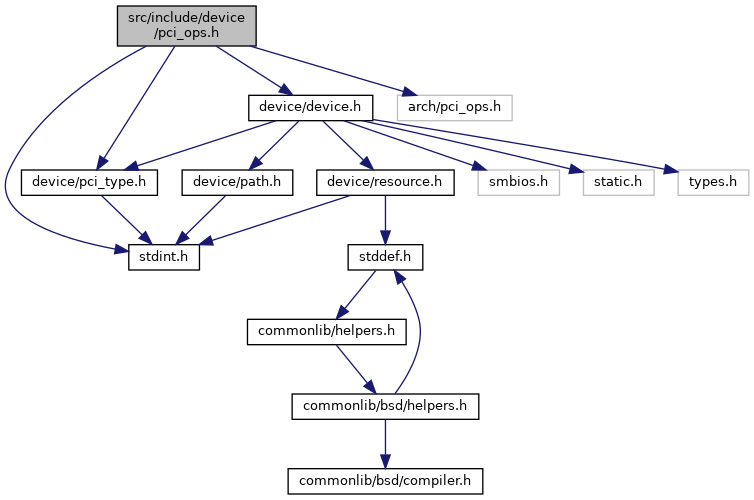

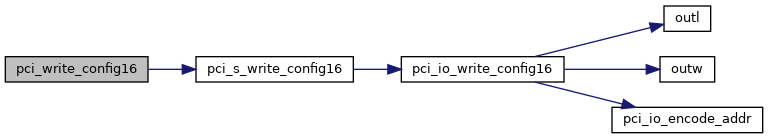

References mask, pci_read_config16(), and pci_write_config16().

Referenced by disable_igd(), ec_init(), enable_igd(), gma_func0_init(), mainboard_lpc_decode(), pch_pcie_early(), pch_pcie_init(), pci_and_config16(), pci_dev_disable_bus_master(), pci_init(), pci_or_config16(), sata_init(), sdram_program_graphics_frequency(), and usb_xhci_init().

|

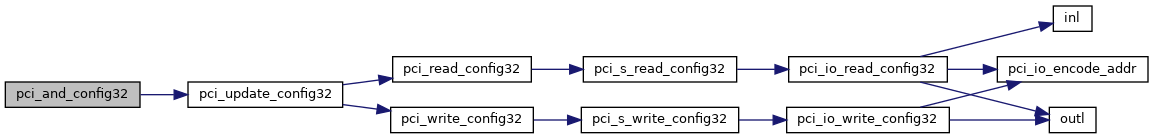

static |

Definition at line 120 of file pci_ops.h.

References mask, pci_read_config32(), and pci_write_config32().

Referenced by azalia_init(), bh720_init(), early_cpu_init(), early_quickpath_init(), gl9763e_init(), hide_pci_fn(), i82801ix_pcie_init(), i82801jx_pcie_init(), i945_setup_pci_express_x16(), intel_pch_finalize_smm(), ironlake_init(), lv2_enable(), mainboard_lpc_decode(), northbridge_topology_init(), pch_pcie_early(), pch_pcie_pm_late(), pch_pm_init_magic(), pch_smbus_init(), pci_and_config32(), pci_init(), pci_or_config32(), pci_store_rebar_size(), pcie_enable_clock_gating(), pciexp_L1_substate_commit(), pmc_soc_init(), sata_init(), setup_aspm(), start_peg2_link_training(), start_peg_link_training(), usb_ehci_init(), and usb_xhci_init().

|

static |

Definition at line 88 of file pci_ops.h.

References mask, pci_read_config8(), and pci_write_config8().

Referenced by azalia_init(), configure_mmap(), enable_spi_prefetching_and_caching(), gma_func0_read_resources(), haswell_setup_igd(), i82801gx_configure_cstates(), i82801ix_configure_cstates(), i945_setup_bars(), lpt_pm_init(), pch_pcie_early(), pci_and_config8(), pci_or_config8(), pcie_enable_clock_gating(), program_memory_map(), root_port_init_config(), sandybridge_setup_graphics(), sata_enable(), and sb_rtc_init().

|

static |

Definition at line 70 of file pci_ops.h.

References PCI_BDF, pci_s_write_config16(), and val.

Referenced by bootblock_c_entry(), bootblock_early_southbridge_init(), bootblock_mainboard_early_init(), busmaster_disable_on_bus(), cardbus_enable_resources(), cardbus_read_resources(), chipset_init(), configure_e7501_cas_latency(), configure_e7501_ram_addresses(), configure_mmap(), disable_mmc_controller_bar(), do_ram_command(), early_graphics_setup(), early_lpc_init(), early_tco_init(), ecam0_pci_enable_msix(), enable_clock_gating(), enable_espi_lpc_io_windows(), enable_hpet(), enable_lp_clock_gating(), enable_mmc_controller_bar(), enable_pm(), enable_pmcbar(), fast_spi_early_init(), find_vbt_location(), gma_func0_disable(), handleInt1a(), haswell_setup_igd(), hda_enable(), hda_work_around(), heci_init(), hudson_lpc_enable_childrens_resources(), hybrid_graphics_init(), i82801dx_enable(), i82801dx_lpc_decode_en(), i82801dx_lpc_route_dma(), i82801dx_power_options(), i82801gx_enable(), i82801gx_lpc_setup(), i82801gx_power_options(), i82801ix_lpc_setup(), i82801ix_power_options(), i82801jx_lpc_setup(), i82801jx_power_options(), i945_setup_bars(), i945_setup_pci_express_x16(), ich7_setup_dmi_rcrb(), ide_init_enable(), igd_disable(), iio_dfx_global_init(), init_sb800_IMC_fans(), int1a_handler(), intel_gma_init(), intel_me_finalize(), intel_mei_setup(), isa_init(), lpc_enable_childrens_resources(), lpc_enable_fixed_io_ranges(), lpc_enable_rom(), lpc_init(), lpc_set_fixed_io_ranges(), lpc_set_wideio_range(), lpss_i2c_early_init_bus(), mainboard_early_init(), mainboard_lpc_decode(), mainboard_pch_lpc_setup(), mainboard_romstage_entry(), p2sb_dev_enable_bar(), p2sb_get_ioapic_bdf(), p2sb_set_ioapic_bdf(), p64h2_ioapic_enable(), pch_cg_init(), pch_early_lpc(), pch_enable(), pch_enable_ioapic(), pch_enable_lpc(), pch_enable_lpc_decode(), pch_pcie_init(), pch_pmc_add_io_resources(), pch_power_options(), pci7420_cardbus_init(), pci_bridge_route(), pci_bridge_vga_compat(), pci_bus_enable_resources(), pci_bus_reset(), pci_cfg_write(), pci_dev_enable_resources(), pci_early_hsuart_device_probe(), pci_init(), pci_moving_config16(), pci_store_bridge_resource(), pci_update_config16(), pciexp_configure_ltr(), pciexp_enable_aspm(), pciexp_enable_clock_power_pm(), pciexp_enable_common_clock(), pciexp_retrain_link(), pciexp_set_max_payload_size(), pcix_tune_dev(), pcr_execute_sideband_msg(), pmc_soc_init(), pre_jedec_memory_map(), program_memory_map(), program_total_memory_map(), pwrmgt_enable(), r8168_init(), raminit(), reg_script_write_pci(), rl5c476_init(), sandybridge_setup_graphics(), sata_enable(), sata_init(), sc_init(), sdram_initialize(), sdram_mmap(), sdram_mmap_regs(), sdram_program_row_boundaries(), sdram_set_registers(), sdram_set_spd_registers(), set_dram_buffer_strength(), set_dram_row_attributes(), set_usb_over_current(), smbus_common_init(), smbus_enable_iobar(), soc_enable_psp_early(), storage_test_complete(), storage_test_init(), systemagent_vtd_init(), try_cached_training(), usb_xhci_clock_gating(), watchdog_off(), and x4x_early_init().

|

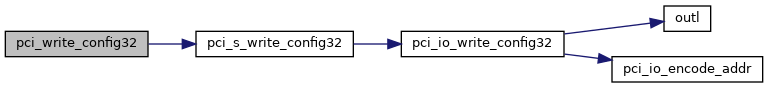

static |

Definition at line 76 of file pci_ops.h.

References PCI_BDF, pci_s_write_config32(), and val.

Referenced by adsp_init(), amd_initcpuio(), azalia_init(), azalia_pch_init(), bh720_init(), board_BeforeAgesa(), bootblock_early_southbridge_init(), bootblock_mainboard_early_init(), bootblock_southbridge_init(), bootblock_systemagent_early_init(), broadwell_setup_bars(), byt_config_com1_and_enable(), byt_pcie_init(), cf9_reset_prepare(), check_device_present(), clear_bios_reset(), configure_child_lpc_windows(), configure_dpr(), configure_e7501_cas_latency(), configure_e7501_dram_controller_mode(), configure_e7501_dram_timing(), configure_e7501_ram_addresses(), configure_e7501_row_attributes(), configure_mmap(), cpu_cl_discovery(), create_vga_resource(), d060_control(), data_fabric_broadcast_write32(), data_fabric_set_indirect_address(), data_fabric_write32(), disable_devices(), disable_mmc_controller_bar(), disable_peg(), do_ram_command(), dram_memorymap(), early_gpio_init(), early_lpc_init(), early_misc_setup(), early_pmc_init(), early_quickpath_init(), early_thermal_init(), early_usb_init(), ecam0_init(), eeprom_read_buffer(), eeprom_write_byte(), enable_hpet(), enable_igd(), enable_mmc_controller_bar(), enable_pm(), enable_pmcbar(), enable_serial(), enable_usb_bar(), enable_usb_bar_on_device(), enable_wideio(), espi_disable_lpc_ldrq(), exit_soft_temp_disable(), f1_write_config32(), fam15_finalize(), fam16_finalize(), fast_spi_clear_sync_smi_status(), fast_spi_early_init(), fast_spi_enable_ext_bios(), fast_spi_set_bios_control_reg(), find_vbt_location(), gfx_init(), gl9755_enable(), gm45_early_init(), gm45_init(), gma_read_resources(), gpi_route_interrupt(), gpio_init(), gspi_set_base_addr(), handleInt1a(), haswell_setup_bars(), haswell_unhide_peg(), hda_pch_init(), hda_work_around(), heci_init(), hudson_lpc_decode(), hudson_lpc_enable_childrens_resources(), hudson_lpc_set_resources(), hudson_spibase(), hudson_tpm_decode_spi(), hybrid_graphics_init(), i82801dx_enable_acpi(), i82801dx_enable_ioapic(), i82801gx_gpi_routing(), i82801gx_lpc_setup(), i82801gx_setup_bars(), i82801ix_early_init(), i82801ix_ehci_init(), i82801ix_gpi_routing(), i82801ix_lpc_setup(), i82801ix_pcie_init(), i82801jx_ehci_init(), i82801jx_gpi_routing(), i82801jx_lpc_setup(), i82801jx_pcie_init(), i82801jx_setup_bars(), i945_setup_bars(), i945_setup_pci_express_x16(), i945_setup_root_complex_topology(), ibexpeak_setup_bars(), ich7_setup_dmi_rcrb(), ich7_setup_pci_express(), init_fan_control(), init_iommu(), init_pcie(), int1a_handler(), intel_early_me_init_done(), intel_me_hsio_version(), intel_me_mbp_give_up(), intel_pch_finalize_smm(), ironlake_early_initialization(), ironlake_setup_bars(), isa_init(), lpc_disable_decodes(), lpc_enable_childrens_resources(), lpc_enable_decode(), lpc_enable_port80(), lpc_enable_sio_decode(), lpc_enable_spi_prefetch(), lpc_enable_spi_rom(), lpc_init(), lpc_open_mmio_window(), lpc_open_pmio_window(), lpc_set_gen_decode_range(), lpc_set_resources(), lpc_set_spibase(), lpc_set_wideio_range(), lpc_spibase(), lpc_tpm_decode(), lpc_tpm_decode_spi(), lpc_wideio_window(), lpe_stash_firmware_info(), lpss_i2c_early_init_bus(), lv2_enable(), lv2_enable_ltr(), mainboard_after_memory_init(), mainboard_early_init(), mainboard_pch_lpc_setup(), mainboard_smi_sleep(), map_rcba(), mchtest_control(), mcr_write(), mdr_write(), mea_write(), northbridge_topology_init(), p2sb_configure_endpoints(), p2sb_dev_enable_bar(), pch_enable_bars(), pch_enable_lpc(), pch_enable_lpc_decode(), pch_gpi_routing(), pch_pcie_pm_early(), pch_pcie_pm_late(), pch_setup_cir(), pci7420_cardbus_init(), pci_cfg_write(), pci_dev_set_subsystem(), pci_early_hsuart_device_probe(), pci_ehci_dbg_set_port(), pci_moving_config32(), pci_rom_probe(), pci_store_bridge_resource(), pci_store_resource(), pci_update_config32(), pci_write_config_dword(), pcr_execute_sideband_msg(), pineview_setup_bars(), pmc_cl_discovery(), pmc_set_disb(), pre_jedec_memory_map(), program_base_addresses(), program_board_delay(), program_sigid(), program_total_memory_map(), protect_a_range(), punit_init(), ram_set_rcomp_regs(), raminit(), reg_script_write_pci(), root_port_init_config(), sa_set_pci_bar(), sandybridge_setup_bars(), sata_enable(), sata_init(), sata_program_indexed(), sdram_enable(), sdram_mmap(), sdram_mmap_regs(), sdram_post_ecc(), sdram_set_registers(), set_global_reset(), set_io_addr_reg(), set_mmio_addr_reg(), set_warm_reset_flag(), setup_aspm(), setup_heci_uma(), sir_read(), sir_unset_and_set_mask(), sir_write(), smbus_common_init(), smbus_enable_iobar(), smbus_i2c_block_write(), smn_read32(), smn_write32(), soc_config_acpibase(), soc_config_pwrmbase(), soc_enable_psp_early(), soc_enable_sata_features(), southbridge_smi_tco(), spi_init(), start_spi_dma_transaction(), storage_test_complete(), storage_test_init(), systemagent_early_init(), tco_enable_bar(), ti_pci1x2y_init(), uart_bootblock_init(), usb_ehci_init(), usb_oc_setup(), usb_xhci_clock_gating(), usb_xhci_init(), and x4x_early_init().

|

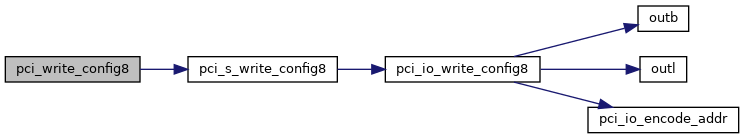

static |

Definition at line 64 of file pci_ops.h.

References PCI_BDF, pci_s_write_config8(), and val.

Referenced by adsp_init(), ahci_raid_init(), all_ports_no_dev_present(), aseg_smm_install(), aseg_smm_lock(), azalia_init(), azalia_pch_init(), bootblock_early_southbridge_init(), bootblock_mainboard_early_init(), broadwell_setup_bars(), checkreset_ddr2(), chipset_init(), clear_errors(), configure_dimm_row_boundaries(), configure_e7501_ram_addresses(), cpt_pm_init(), do_ram_training(), early_gpio_init(), early_graphics_setup(), early_lpc_init(), early_misc_setup(), early_pch_init_native(), enable_e7501_clocks(), enable_pam_region(), enable_pm(), enter_raminit_or_reset(), fast_spi_disable_wp(), fast_spi_enable_wp(), fast_spi_init(), gfx_init(), gm45_early_init(), gma_func0_init(), gma_func1_init(), gpio_init(), handleInt1a(), haswell_setup_bars(), hda_enable(), hda_pch_init(), hda_work_around(), hudson_lpc_enable_childrens_resources(), hudson_lpc_port80(), hudson_pci_port80(), i82801dx_enable_acpi(), i82801dx_enable_serial_irqs(), i82801dx_lpc_decode_en(), i82801dx_pirq_init(), i82801dx_power_options(), i82801dx_rtc_init(), i82801gx_enable_serial_irqs(), i82801gx_fixups(), i82801gx_lpc_setup(), i82801gx_pirq_init(), i82801gx_power_options(), i82801gx_rtc_init(), i82801gx_setup_bars(), i82801ix_early_init(), i82801ix_enable_serial_irqs(), i82801ix_lpc_setup(), i82801ix_pcie_init(), i82801ix_pirq_init(), i82801ix_power_options(), i82801ix_rtc_init(), i82801jx_early_init(), i82801jx_enable_serial_irqs(), i82801jx_lpc_setup(), i82801jx_pcie_init(), i82801jx_pirq_init(), i82801jx_power_options(), i82801jx_rtc_init(), i82801jx_setup_bars(), i945_setup_bars(), ibexpeak_setup_bars(), ide_init_udma33(), igd_disable(), imc_reg_init(), init_pcie(), int1a_handler(), ironlake_early_initialization(), ironlake_setup_bars(), lan_init(), lpc_configure_write_protect(), lpc_disable_clkrun(), lpc_disable_spi_rom_sharing(), lpc_enable_pci_clk_cntl(), lpc_enable_rom(), lpc_init(), lpc_set_bios_control_reg(), lpc_set_serirq_mode(), lpc_set_wideio_range(), lpt_lp_pm_init(), lpt_pm_init(), mainboard_final(), mainboard_init(), mainboard_smi_apmc(), mainboard_smi_brightness_down(), mainboard_smi_brightness_up(), mobile5_pm_init(), northbridge_write_smram(), p2sb_configure_hpet(), p2sb_dev_set_hide_bit(), p2sb_lock_endpoints(), pch_enable_bars(), pch_enable_serial_irqs(), pch_misc_init(), pch_pcie_enable(), pch_pcie_init(), pch_pcie_pm_early(), pch_pirq_init(), pch_pm_init_magic(), pch_rtc_init(), pch_setup_cir(), pci7420_cardbus_init(), pci_bridge_route(), pci_cfg_write(), pci_dev_set_resources(), pci_init(), pci_moving_config8(), pci_store_bridge_resource(), pci_update_config8(), pineview_setup_bars(), pmc_soc_set_afterg3_en(), ppt_pm_init(), punit_init(), pwrmgt_enable(), qemu_nb_init(), quickpath_configure_pll_ratio(), RAM_RESET_DDR_PTR(), raminit(), rce822_enable(), rce822_init(), reg_script_write_pci(), rtc_failure(), sata_enable(), sata_init(), sata_program_indexed(), sdram_checkreset(), sdram_detect_errors(), sdram_enable(), sdram_initialize(), sdram_mmap_regs(), sdram_program_graphics_frequency(), sdram_program_row_boundaries(), sdram_set_registers(), set_d3hot_bits(), set_dram_buffer_strength(), set_dram_row_attributes(), set_enhanced_mode(), setup_heci_uma(), smbus_common_init(), smbus_enable_iobar(), smm_lock(), soc_early_romstage_init(), soc_lockdown(), southbridge_smi_sleep(), southbridge_smi_tco(), spd_enable_refresh(), systemagent_early_init(), ti_pci1x2y_init(), usb_ehci_init(), usb_ehci_set_subsystem(), usb_xhci_clock_gating(), variant_mainboard_final(), write_pci_cfg_irqs(), write_pci_config_irqs(), and x4x_early_init().

|

static |

Definition at line 18 of file pci_ops.h.

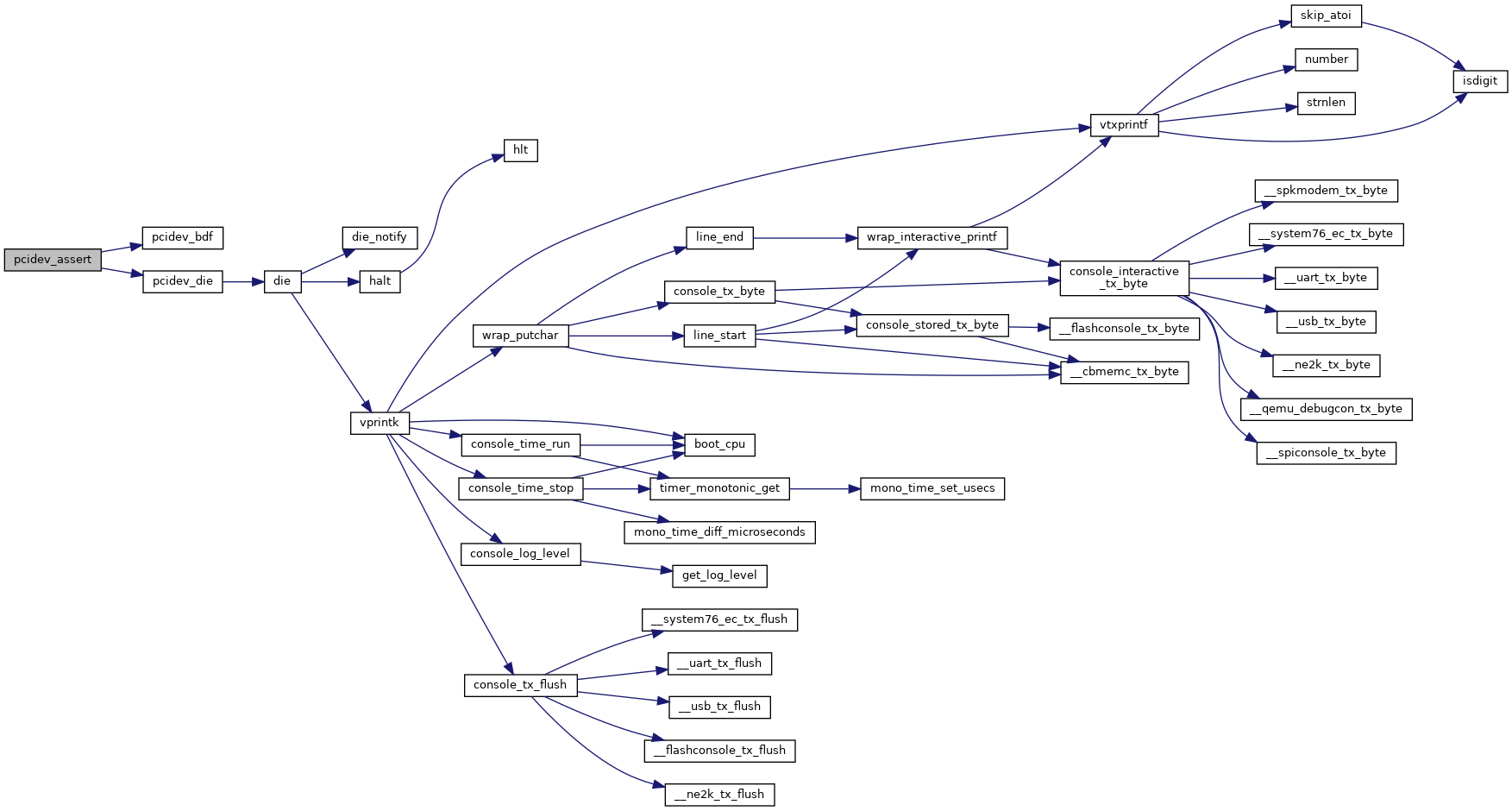

References pcidev_bdf(), and pcidev_die().

|

static |

Definition at line 13 of file pci_ops.h.

References device::bus, pci_path::devfn, device::path, device_path::pci, and bus::secondary.

Referenced by pcidev_assert().

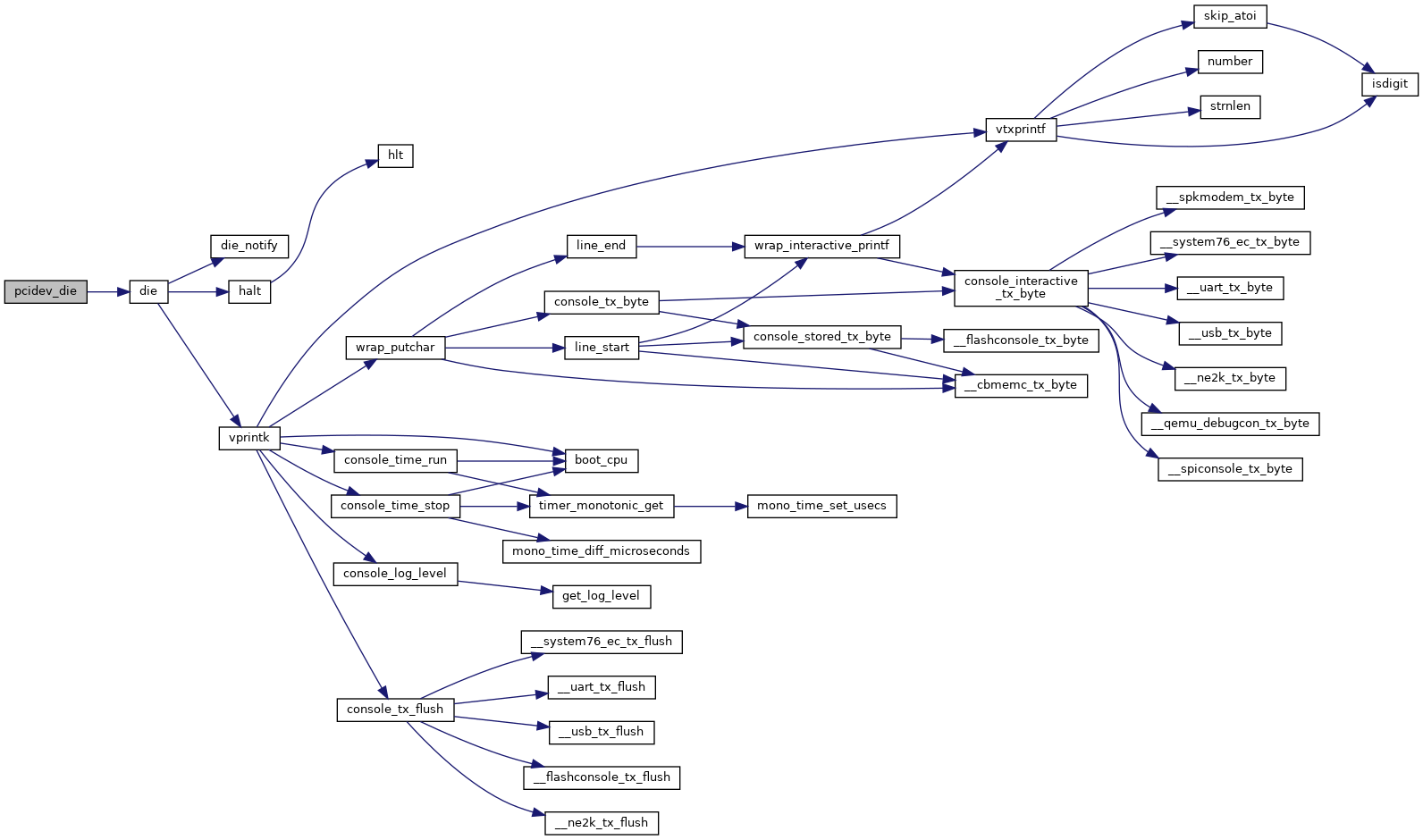

| void __noreturn pcidev_die | ( | void | ) |

Definition at line 77 of file pci_ops.c.

References die().

Referenced by pcidev_assert().